Single machine application verification system compatible with sparc V8 framework SOC

A stand-alone application and verification system technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve problems such as low efficiency, insufficient, inability to verify automated application verification, etc., to improve efficiency, ensure coverage, The effect of improving verification efficiency and coverage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

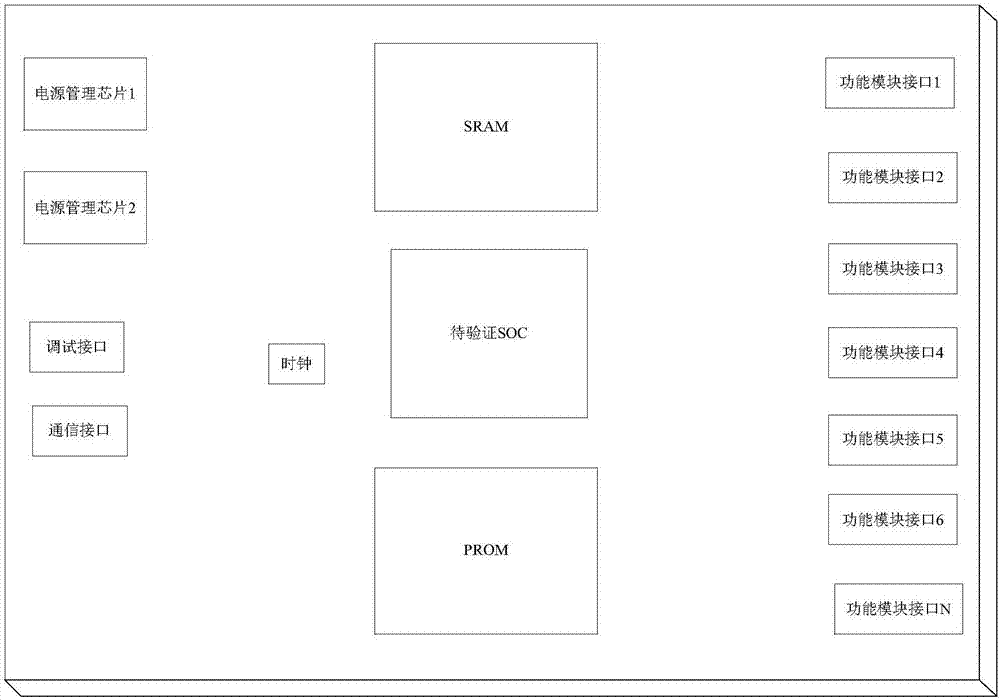

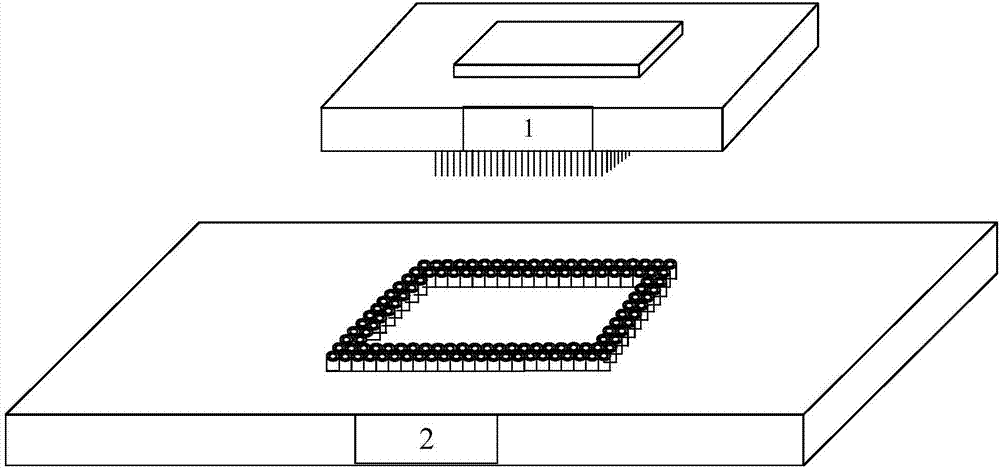

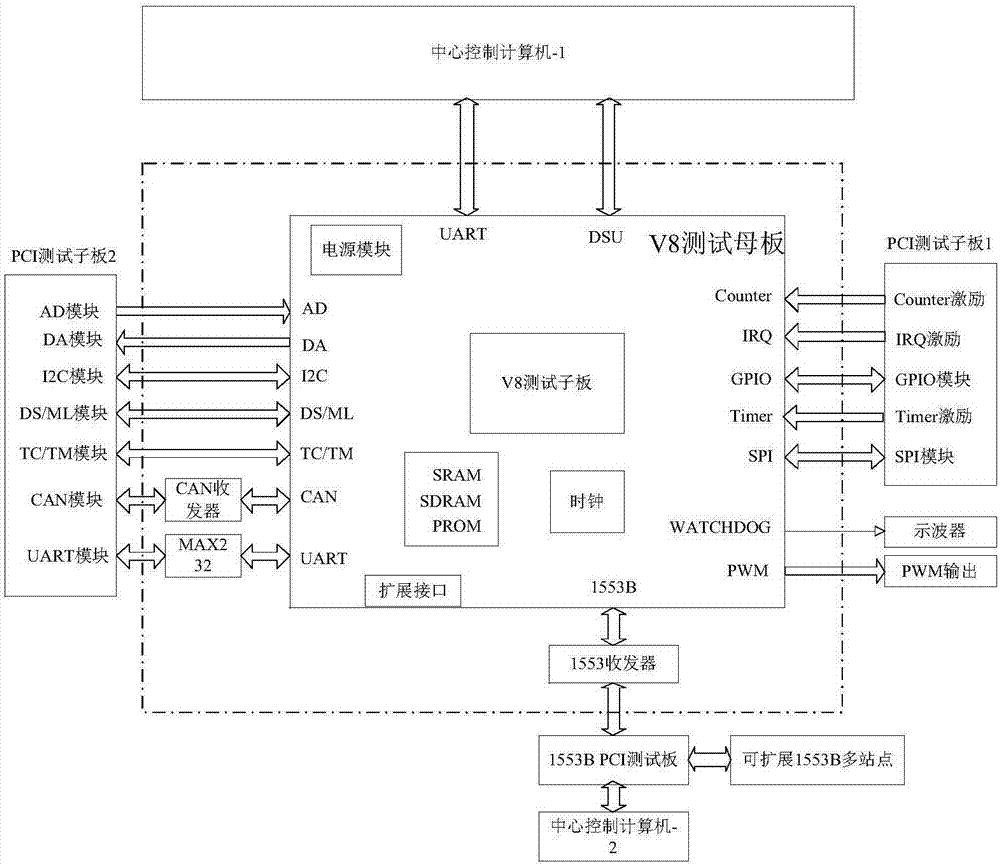

Embodiment 1

[0045] Based on the LCSOC3201 produced by the sparc V8 architecture used by a key model, the fully automatic full-function coverage application verification and the functional verification of the integrated 3 stand-alone machines used in the model are carried out. Among them, LCSOC3201 integrates 13 functional modules including CPU core, memory controller, external interrupt, programmable Timer, GPIO, UART, DSU, programmable Counter, I2C, 1553B control bus, ADC converter, PWM and PLL, and 3 sets The stand-alone only uses part of the design functions of the LCSOC3201. In view of the above application verification requirements, the mother board of the stand-alone application verification board and the daughter board of LCSOC3201 are designed. The daughter board is responsible for leading all the pins of LCSOC3201 to the mother board, and the mother board integrates the function of application verification for the design function of LCSOC3201 Modules and reserved interfaces, sub-...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More