Circuit board manufacturing method

A manufacturing method and circuit board technology, applied in the direction of multi-layer circuit manufacturing, printed circuit manufacturing, printed circuit, etc., can solve the problems of area utilization rate and wiring density decrease, unfavorable electronic product design, area utilization rate decrease, etc. Area usage, improvement of confinement issues, effect of increasing routing density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

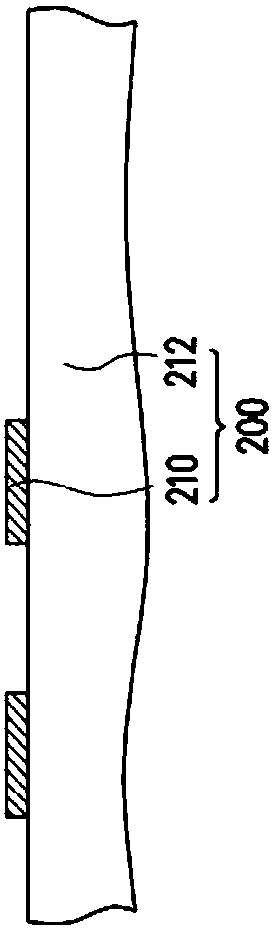

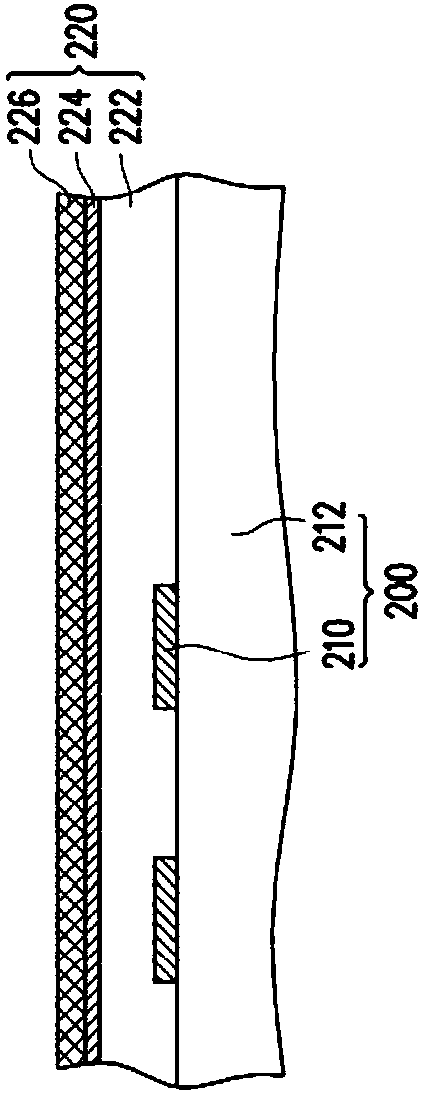

[0043] Figure 2A to Figure 2K It is a schematic cross-sectional view of the manufacturing method of the circuit board according to the first embodiment of the present invention.

[0044] First, please refer to Figure 2A , providing a core layer 200 , wherein the core layer 200 includes a core dielectric layer 212 and a conductive layer 210 on the core dielectric layer 212 . In more detail, the material of the core dielectric layer 212 is, for example, epoxy resin, but not limited thereto. The conductive layer 210 is, for example, a copper layer, and the conductive layer 210 is formed on the core dielectric layer 212 by, for example, lamination. In this embodiment, the core layer 200 may be a double-sided structure or a single-sided structure. For clarity and convenience, Figure 2A to Figure 2K Only a single-panel structure is shown in , but the present invention is not limited thereto.

[0045] Next, please refer to Figure 2B , forming a composite material layer 220 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More