Semiconductor device package structure and package method

A device packaging and semiconductor technology, which is applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, and semiconductor/solid-state device parts, etc. Low production cost and small package size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

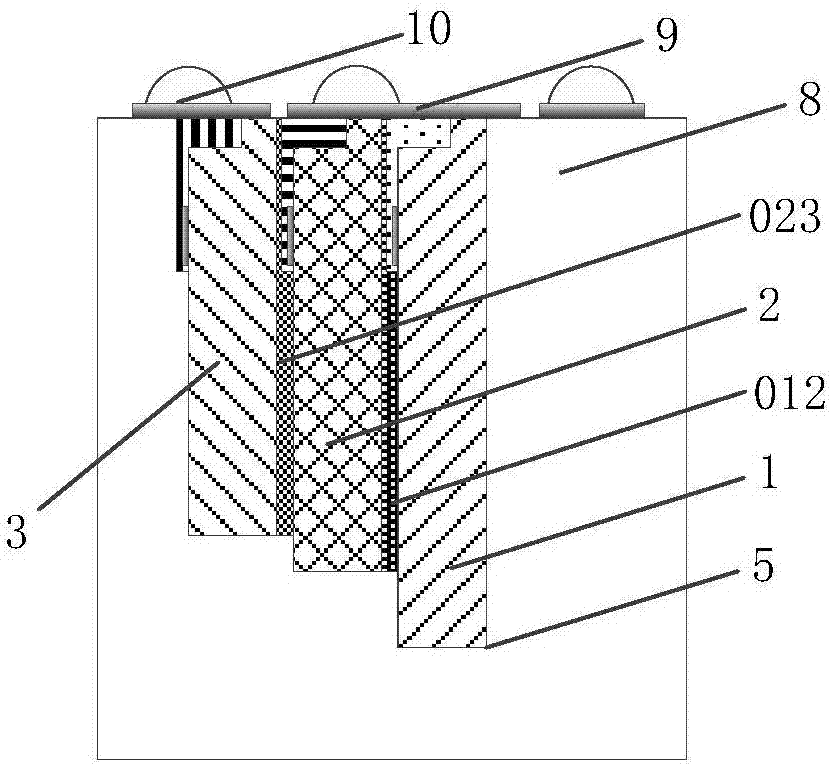

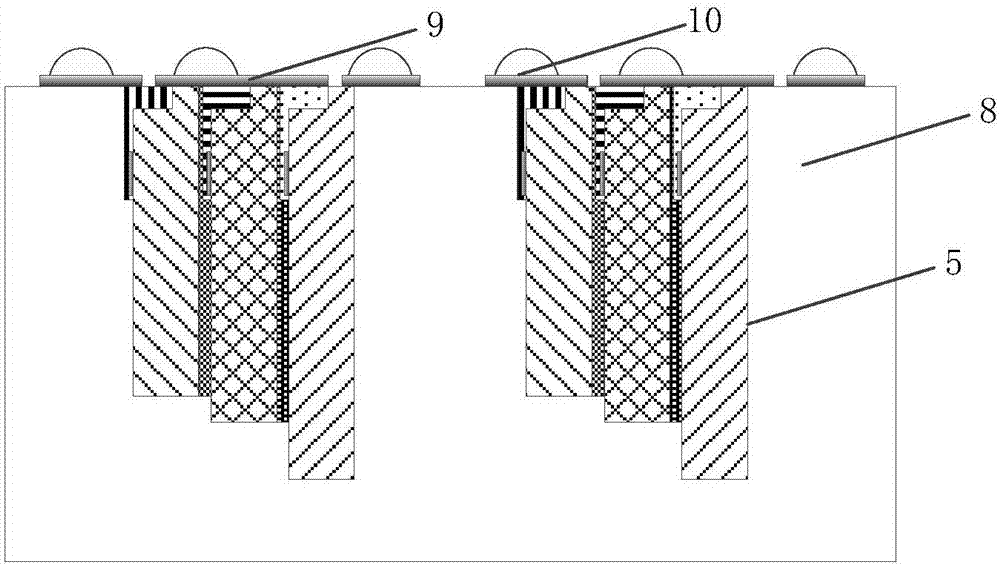

[0034] This embodiment provides a semiconductor device packaging structure, such as figure 1 As shown, it includes: a chipset 5, the chipset 5 is arranged in the encapsulation layer 8, the chipset 5 includes a plurality of chips connected in the vertical direction, and the leads of each chip in the plurality of chips are all located in the chipset 5 On the side wall, the side wall is exposed outside the encapsulation layer 8; the redistribution layer 9 is arranged on the side wall and the encapsulation layer 8, and is connected to the lead on the side wall; the bump 10 is arranged on the redistribution layer 9, and Rewiring layer 9 connections. Each chipset 5 is obtained by cutting a plurality of chipsets placed vertically above the carrier, wherein the side walls are connected to the carrier. In this embodiment, the chipset 5 includes a chipset, such as figure 1 shown; of course, in other embodiments, the chipset 5 can also include multiple chipsets, such as two chipsets, s...

Embodiment 2

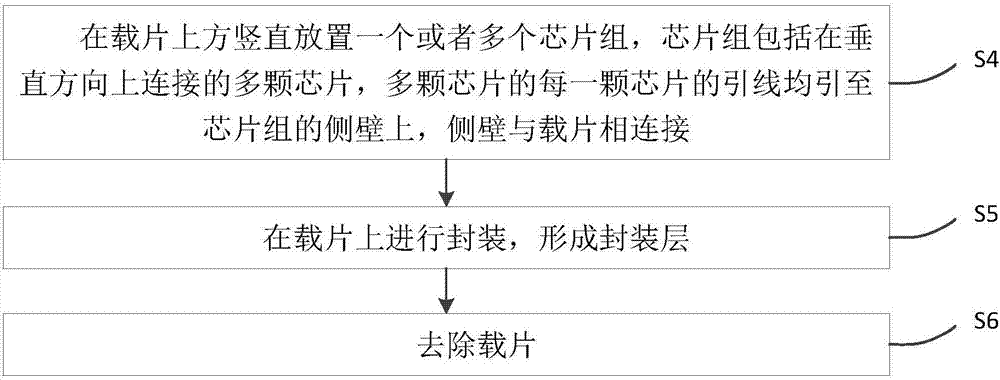

[0039] This embodiment provides a semiconductor device packaging method, the flow chart is as follows image 3 Shown; As a preferred solution of this embodiment, the flow chart is as follows Figure 4 shown, including the following steps:

[0040] S1: lead the leads of each of the chips to the sidewall. In this embodiment, there are three chips, which are the first chip 1, the second chip 2 and the third chip 3 in sequence. The first chip 1 is cut from the first wafer 01, and the second chip 2 is cut from the first wafer 01. Two wafers are cut, and the third chip 3 is cut from the third wafer; of course, in other embodiments, the number of chips can also be two, four or even more, and it can be reasonably set as required. Can. In this embodiment, the three chips are different chips, and of course, in other embodiments, they may also be the same chip, which can be reasonably set as required.

[0041] Taking the first chip 1 obtained by cutting the first wafer 01 as an examp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More