Bus synchronous control framework and control method

A technology of synchronous control and control method, which is applied to the photolithography process of the pattern surface, the photolithography process exposure device, optics, etc., which can solve the problem of the strict requirements of the maglev dual-stage photolithography machine, and achieve increased bandwidth and enhanced stability. , The effect of reducing the number of pins occupied

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

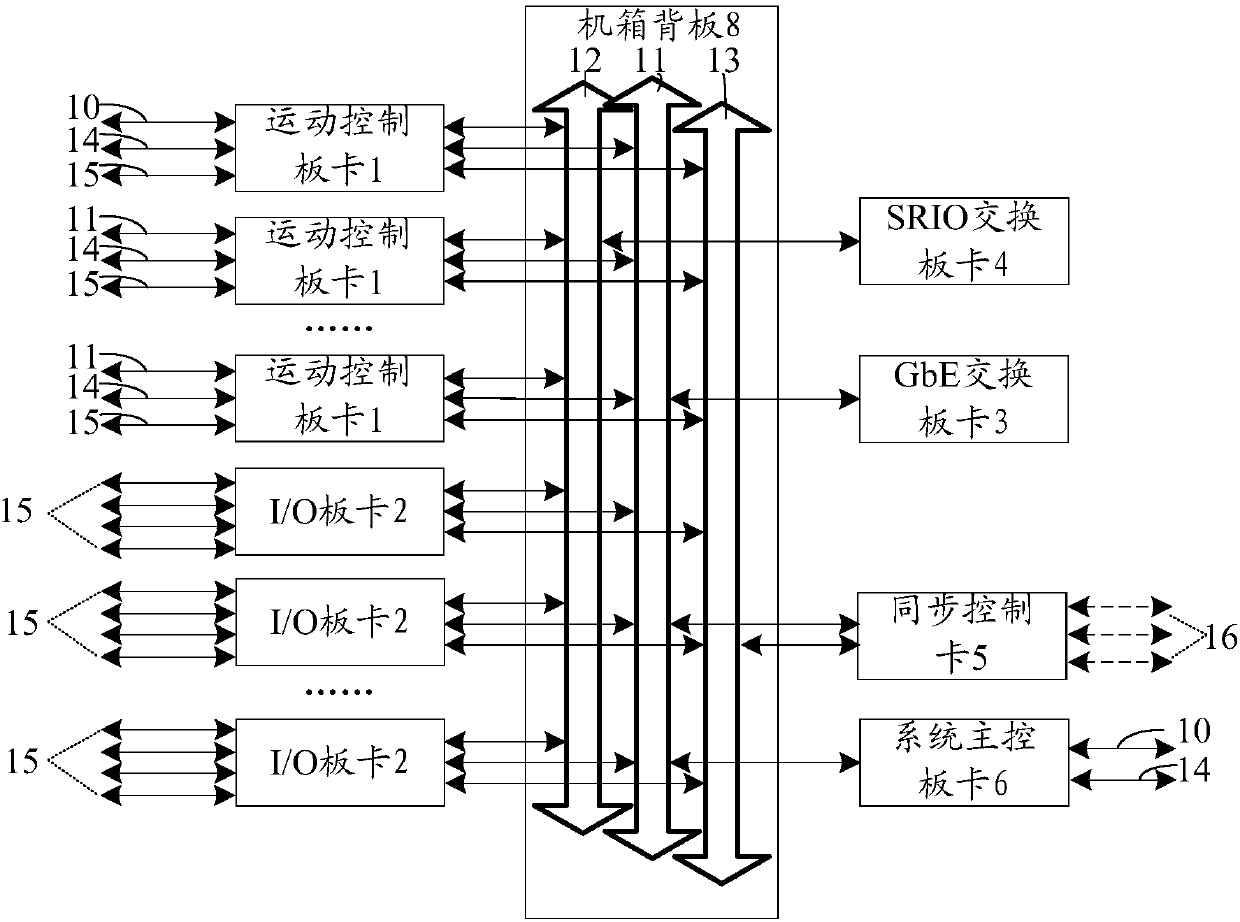

[0045] Such as figure 1 As shown, the present invention is based on a synchronous control framework of SRIO (Serial RapidIO) bus, including motion control board 1, I / O board 2, GbE (Gigabit Ethernet) switching board 3, SRIO switching board 4 , synchronous control board 5 and system main control board 6. Among them, there are multiple motion control boards 1 and I / O boards 2 respectively.

[0046] The system main control board 6 receives commands from the host computer 7 and initializes the entire system; specifically, the system main control board 6 receives commands issued by the host computer 7 through the GbE control bus 11 on the chassis backplane 8 , including initialization, machine parameter delivery, distribution of motion control board 1 operating firmware, etc. After the system main control board 6 interprets the command, it sends the command to each of the system through the GbE control bus 11 on the chassis backplane 8 Boards, including motion control board 1, I / ...

Embodiment 2

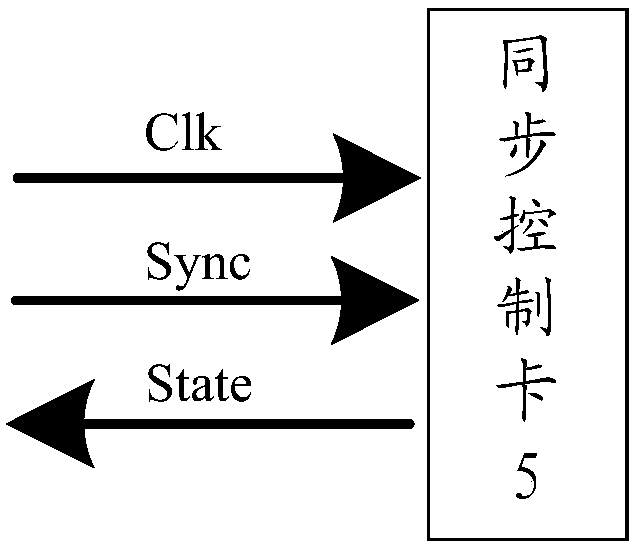

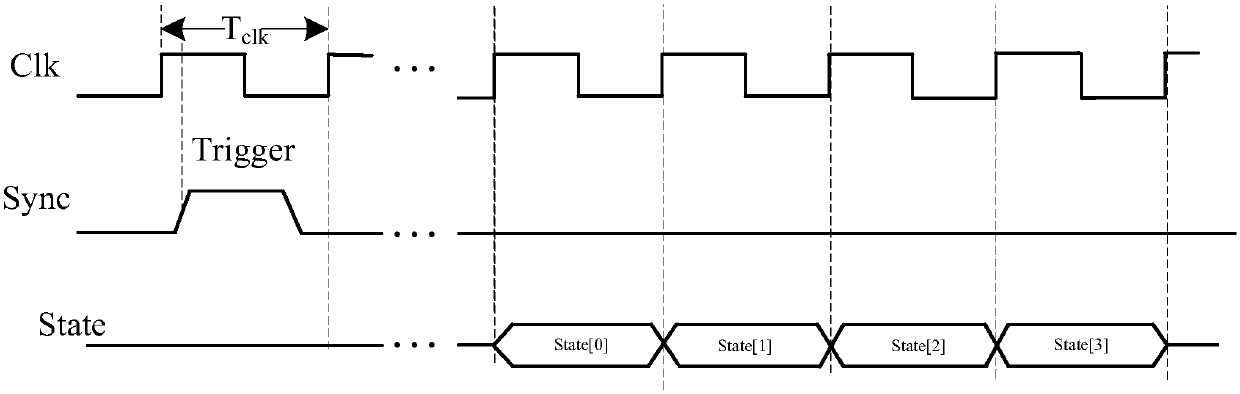

[0066] Such as Image 6 As shown, the difference from Embodiment 1 is that in this embodiment, the synchronous switching board 9 replaces the synchronous control board 5, and there is no GbE switching board 3 and SRIO switching board 4 in the synchronous control framework, which simplifies the control Architecture, when there is no redundant synchronous bus 13 on the chassis backplane 8, the synchronous control board 5 provides the system clock for the synchronous system, the clock bus is connected to the timing / counter in each board, and the timing / counter in the board The counter performs clock timing. When the set value is reached, an interrupt signal is generated and broadcast to the CPU of each board to start a new servo cycle.

[0067] Sometimes in order to save hardware resources and increase the realizability of the system, the servo interrupt information and system synchronization status information are directly transmitted through the SRIO data bus 12: the system agr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com