Erasing method and device of memory unit

A memory cell and erasing voltage technology, applied in the storage field, can solve problems such as slowing down the erasing speed, achieve the effect of reducing the impact and improving the erasing performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

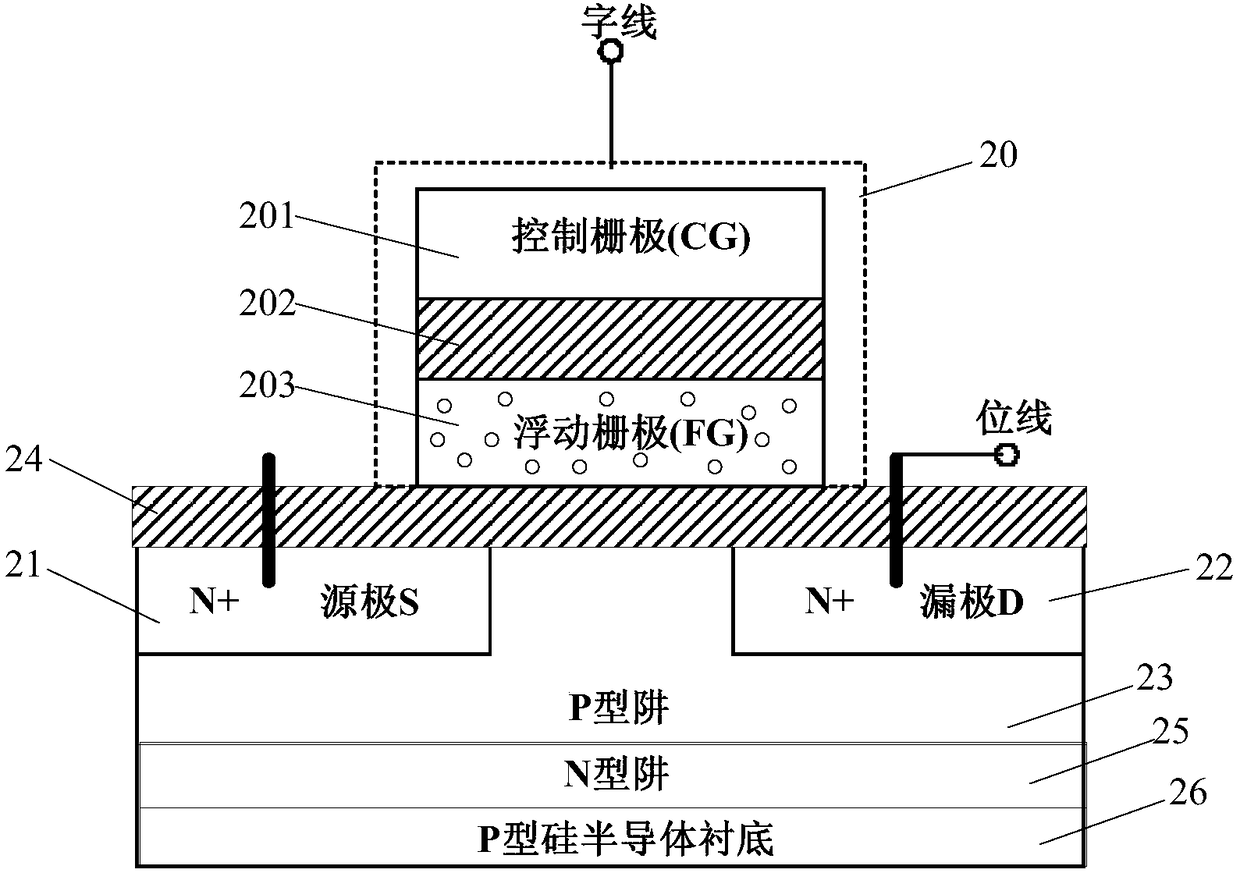

Image

Examples

Embodiment 1

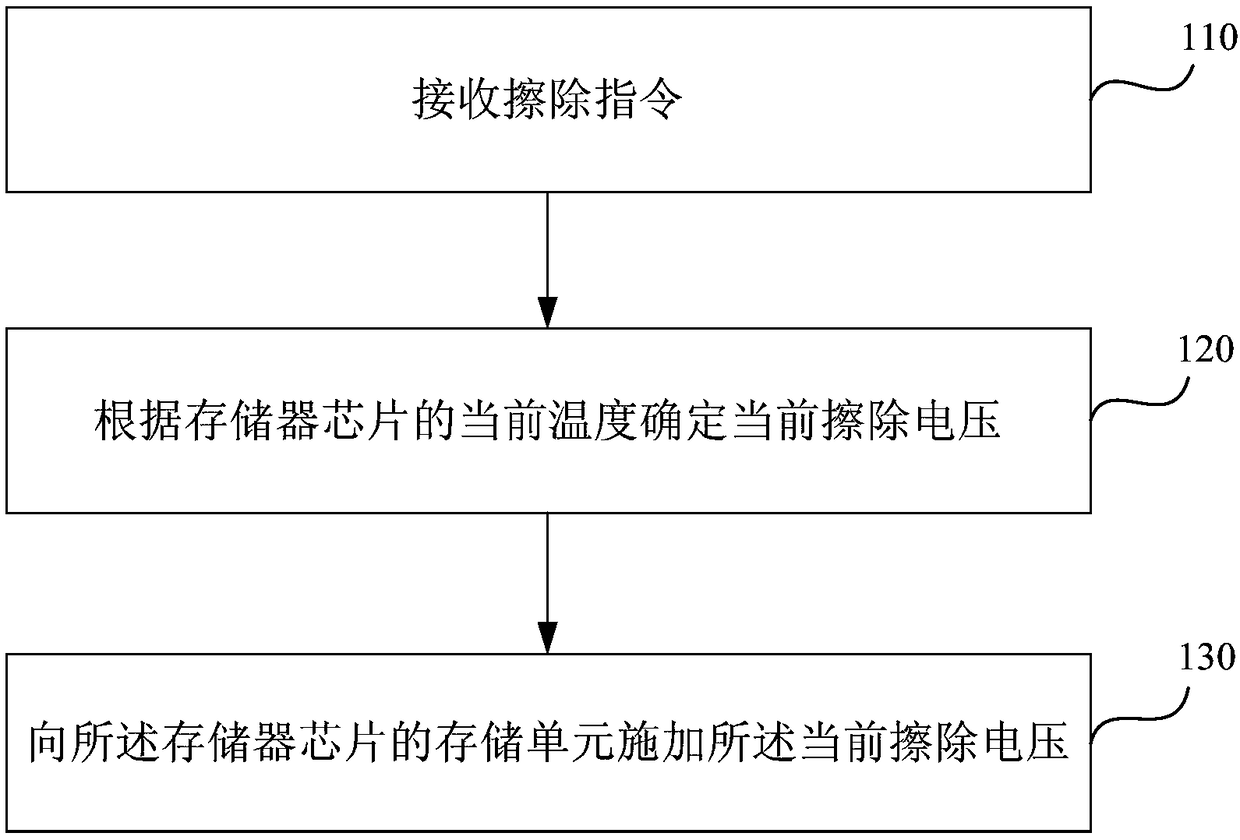

[0042] figure 2 It is a schematic flowchart of a method for erasing a memory cell provided by Embodiment 1 of the present invention. This embodiment is applicable to the case where memory cells are erased at different temperatures. see figure 2 The erasing method of the storage unit provided in this embodiment specifically includes the following steps:

[0043] 110. Receive an erase instruction.

[0044] The flash chip is composed of thousands of internal storage units, each storage unit stores one bit of data, multiple storage units form a page, multiple pages form a block, and multiple blocks form a storage unit array. Special physical structure, in nor flash / nand flash, the erase operation is performed in units of blocks; the storage unit array is composed of a plurality of storage unit blocks, and the storage unit block is composed of a plurality of storage unit pages, and the storage unit A cell page consists of multiple memory cells connected in rows and columns. I...

Embodiment 2

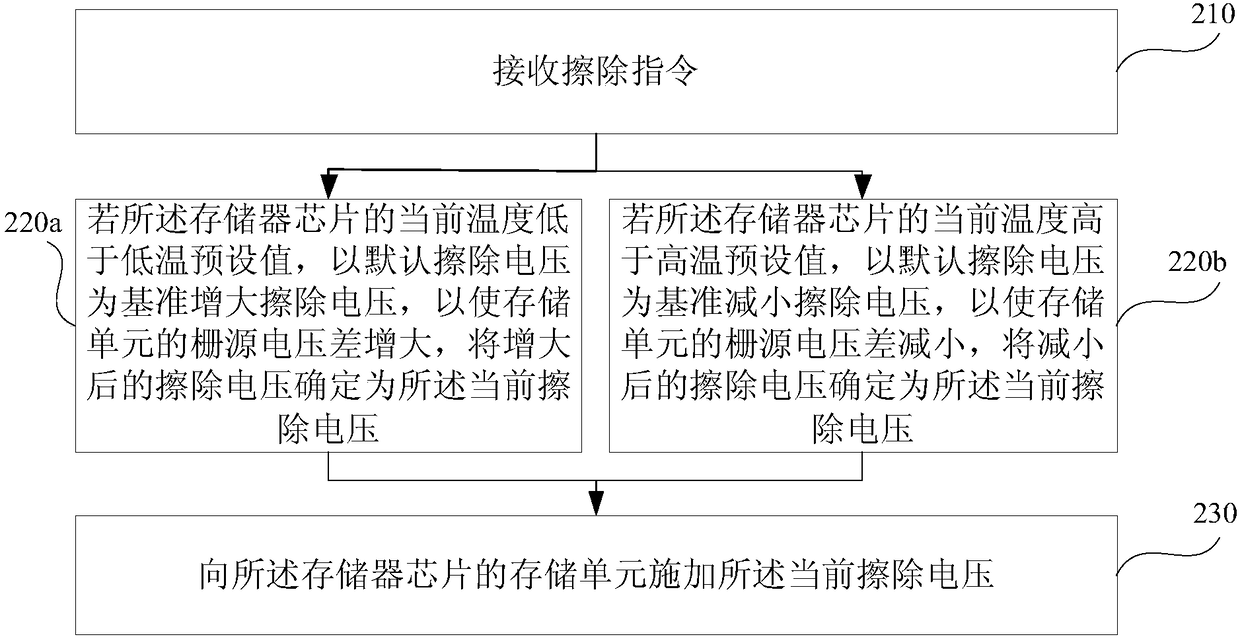

[0056] image 3 It is a schematic flow chart of a memory cell erasing method provided by Embodiment 2 of the present invention. This embodiment is further optimized on the basis of Embodiment 1, and is especially applicable when the temperature change of the memory chip causes the erasing speed to become slow or slow down. In the fast case, the advantage of optimization is that when the temperature of the memory chip is lower than the low temperature preset value or higher than the high temperature preset value, the erasing voltage matching the temperature is determined to ensure the erasing speed and improve over-erase erase phenomenon and improve erase performance. For details, please refer to image 3 , the method specifically includes the following steps:

[0057] 210. Receive an erase instruction.

[0058] 220a. If the current temperature of the memory chip is lower than the low temperature preset value, increase the erasing voltage based on the default erasing voltage...

Embodiment 3

[0066] Figure 4 It is a schematic structural diagram of an erasing device for a storage unit provided in Embodiment 3 of the present invention, and the device specifically includes:

[0067] receiving module 410, determining module 420 and applying module 430;

[0068] Wherein, the receiving module 410 is used to receive the erasing instruction; the determining module 420 is used to determine the current erasing voltage according to the current temperature of the memory chip; the applying module 430 is used to apply the current erasing voltage to the storage unit of the memory chip. In addition to voltage.

[0069] Further, the device may further include a detection module, configured to detect the current temperature of the memory chip through a temperature sensor before the current erasing voltage is determined according to the current temperature of the memory chip.

[0070] Further, the determining module 420 may include:

[0071] An increasing unit, configured to incr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More