Thin film transistor and manufacturing method thereof, array substrate and display device

A technology of a thin film transistor and a manufacturing method, which is applied in the field of array substrates and display devices, thin film transistors and manufacturing methods thereof, and can solve the problems of large ohmic contact resistance and large parasitic resistance of the source and drain terminals of top-gate thin film transistors, etc., and achieve reduction Small parasitic resistance and total source-drain resistance, improved device performance, and improved display quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

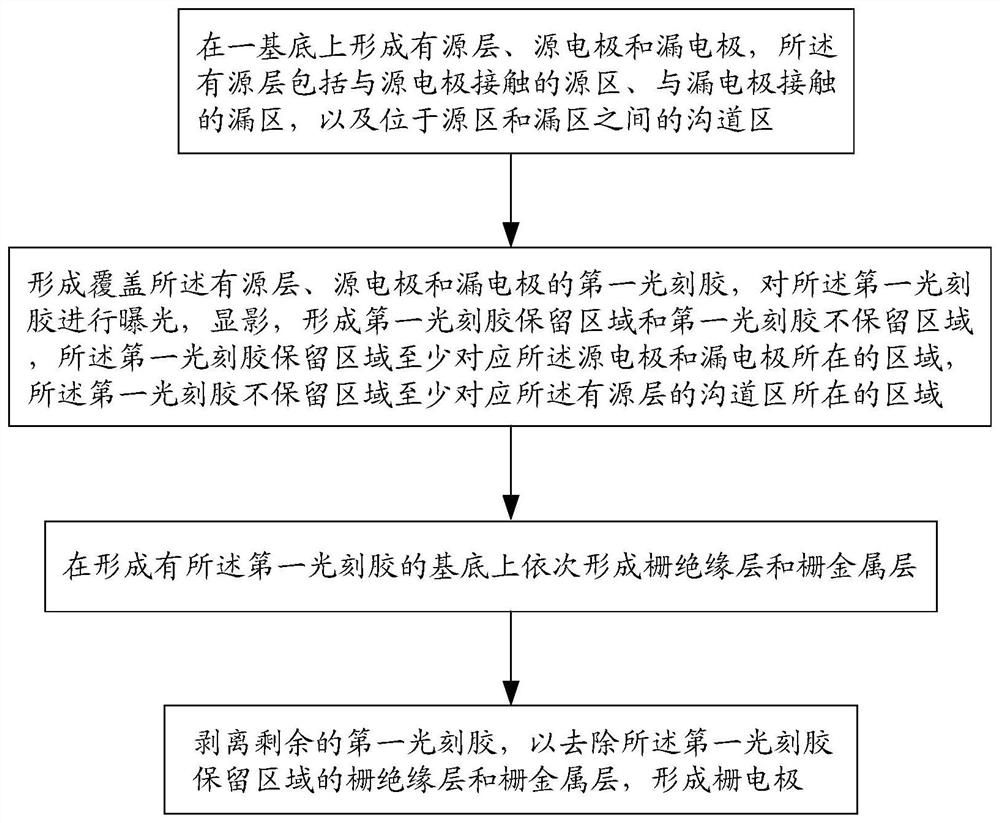

[0023] Such as figure 1 As shown, a method for manufacturing a thin film transistor is provided in this embodiment, specifically a method for manufacturing a top-gate thin film transistor, and the method includes:

[0024] Forming an active layer, a source electrode and a drain electrode on a substrate, the active layer including a source region in contact with the source electrode, a drain region in contact with the drain electrode, and a channel region between the source region and the drain region ;

[0025] Forming a first photoresist covering the active layer, source electrode and drain electrode, exposing and developing the first photoresist to form a first photoresist remaining area and a first photoresist non-retaining area , the first photoresist-retained region at least corresponds to the region where the source electrode and the drain electrode are located, and the first photoresist-free region corresponds to at least the region where the channel region of the acti...

Embodiment 2

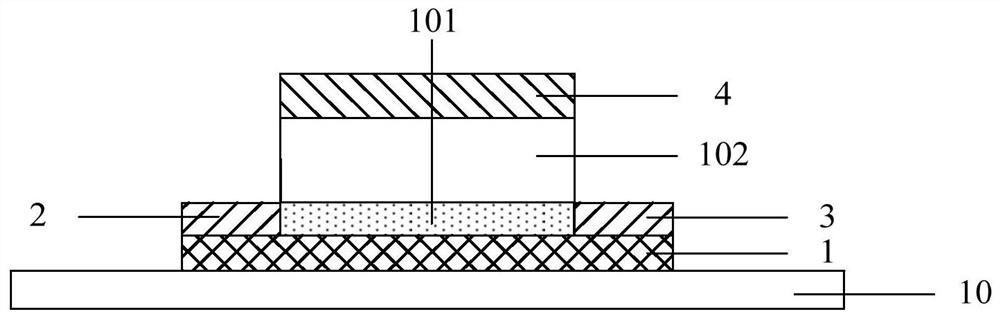

[0065] Such as figure 2 As shown, this embodiment provides a thin film transistor manufactured by the manufacturing method in Embodiment 1, including:

[0066] An active layer 1, a source electrode 2 and a drain electrode 3 arranged on a substrate 10, the active layer 1 includes a source region in contact with the source electrode 2, a drain region in contact with the drain electrode 3, and a region located in the source region and the drain region channel region between

[0067] A gate insulating layer disposed on the active layer 1 and a gate electrode 4 disposed on the gate insulating layer, wherein the patterns of the gate insulating layer and the gate electrode 4 are consistent, and the gate insulating layer includes The first part between the electrode and the drain electrode, the orthographic projection of the first part on the substrate coincides with the orthographic projection of the channel region of the active layer on the substrate.

[0068] The source electrod...

Embodiment 3

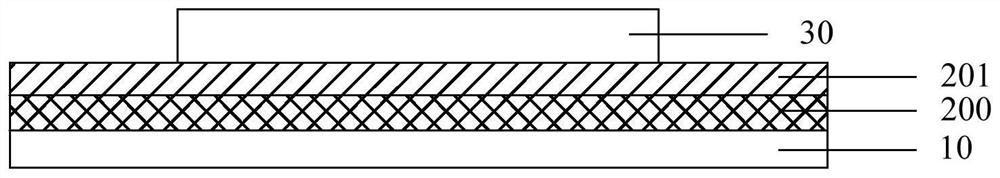

[0078] This embodiment provides an array substrate and a display device, the array substrate adopts the thin film transistor in Embodiment 2, and the display device includes the thin film transistor. The thin film transistor is specifically a top-gate thin film transistor. Since the gate electrode is self-aligned with the source electrode and the drain electrode, the alignment is strict and accurate, which reduces the parasitic resistance of the device and the total resistance of the source and drain, improves the performance of the device, and improves In order to display the display quality of the product. At the same time, it saves the process steps of separately making the gate, saves the process, and also saves the process of conducting the active layer, saves time and energy consumption, and overcomes the limitations of the material selection of the source electrode and the drain electrode. The problem of limiting the ohmic contact resistance of the source layer reduces ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More