Flash memory

A technology of flash memory and flash memory unit, which is applied in the direction of electrical components, electric solid-state devices, circuits, etc. It can solve the problems of increasing polysilicon floating gate mutual interference, information error, and reducing the spacing of polysilicon floating gates, etc., to achieve size reduction and lower gate voltage. , the effect of increasing the coupling rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The flash memory in the embodiment of the present invention is formed on the basis of analyzing the existing technology. Therefore, before describing the flash memory in the embodiment of the present invention in detail, the existing flash memory is introduced as follows:

[0037] Existing Flash:

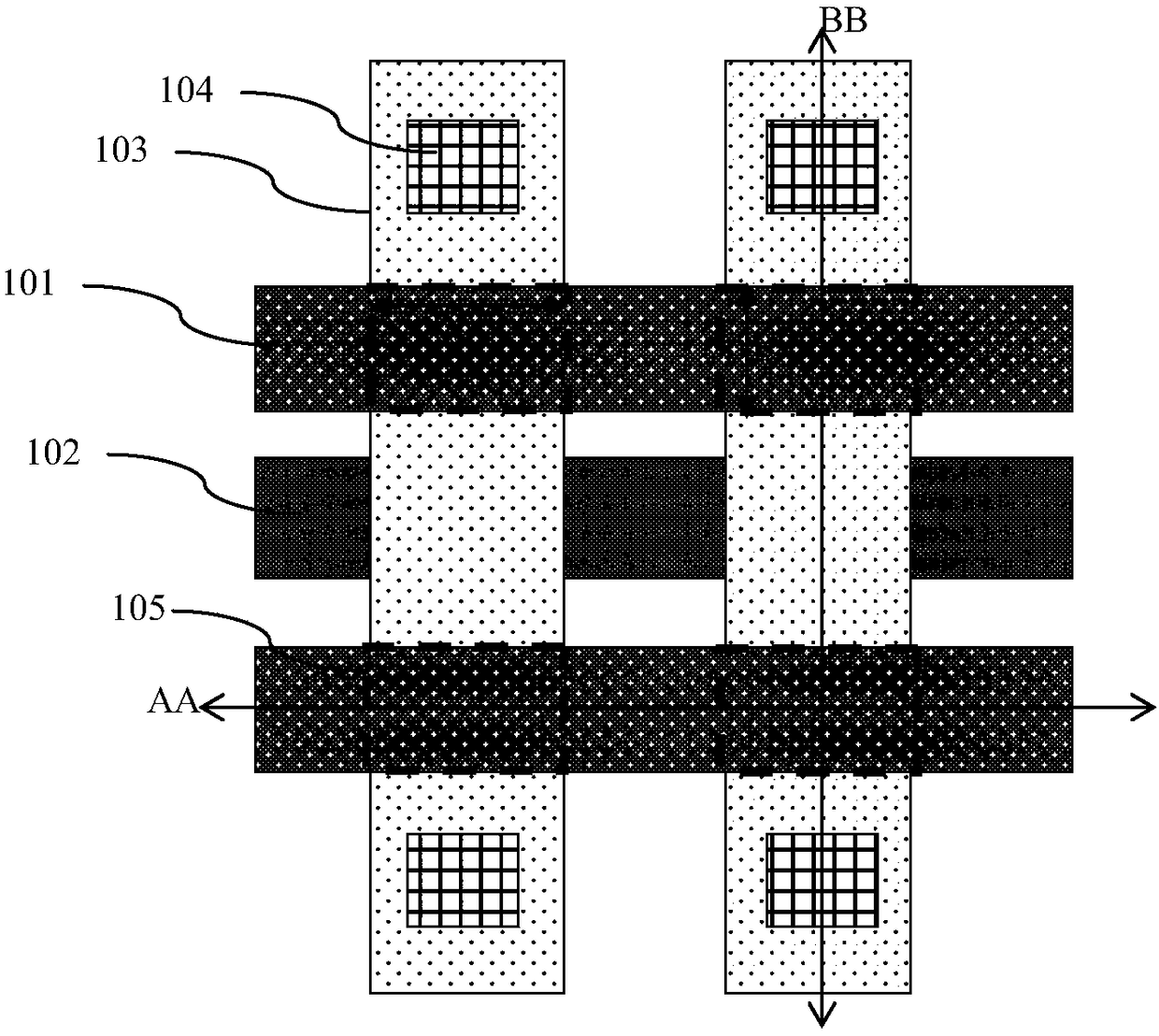

[0038] like figure 1 As shown, is the layout structure of the storage area 202 of the flash memory; figure 2 shown, is the edge of the existing flash figure 1 Sectional view of the middle AA line; such as image 3 shown, is the edge of the existing flash figure 1 Sectional drawing of the middle BB line; such as Figure 4A Shown is the top-view layout of the polysilicon floating gate of the existing flash memory; Figure 4B shown is a perspective view of a single polysilicon floating gate of an existing flash memory; as Figure 4C Shown is a perspective view of two adjacent polysilicon floating gates of an existing flash memory; the flash memory in the existing flash me...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More