Semiconductor structure and forming method thereof

A semiconductor and gate structure technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problem that the surface of the wafer cannot provide enough area interconnection lines, etc., to reduce metal-induced Effects of gap state phenomenon, performance improvement, and contact resistance reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] It can be seen from the background art that there is a problem of excessive contact resistance in the semiconductor structure with plugs introduced in the prior art. Combining with a method of forming a semiconductor structure, the reason for the excessive contact resistance is analyzed:

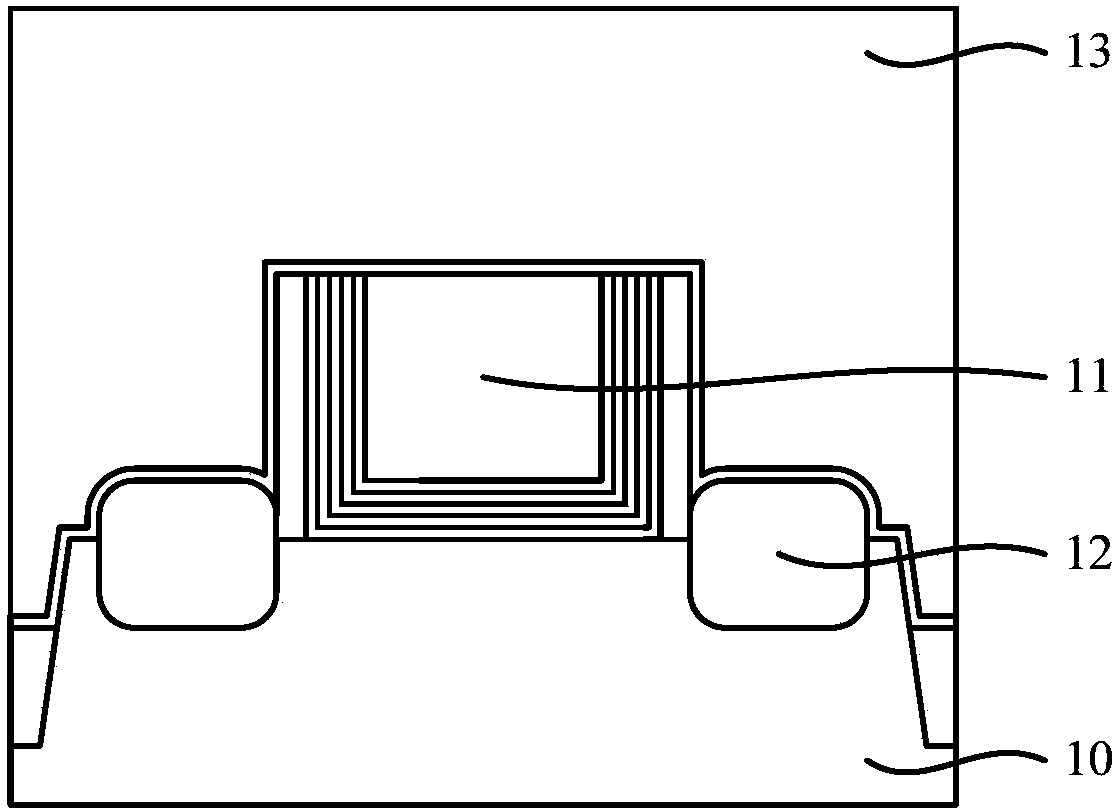

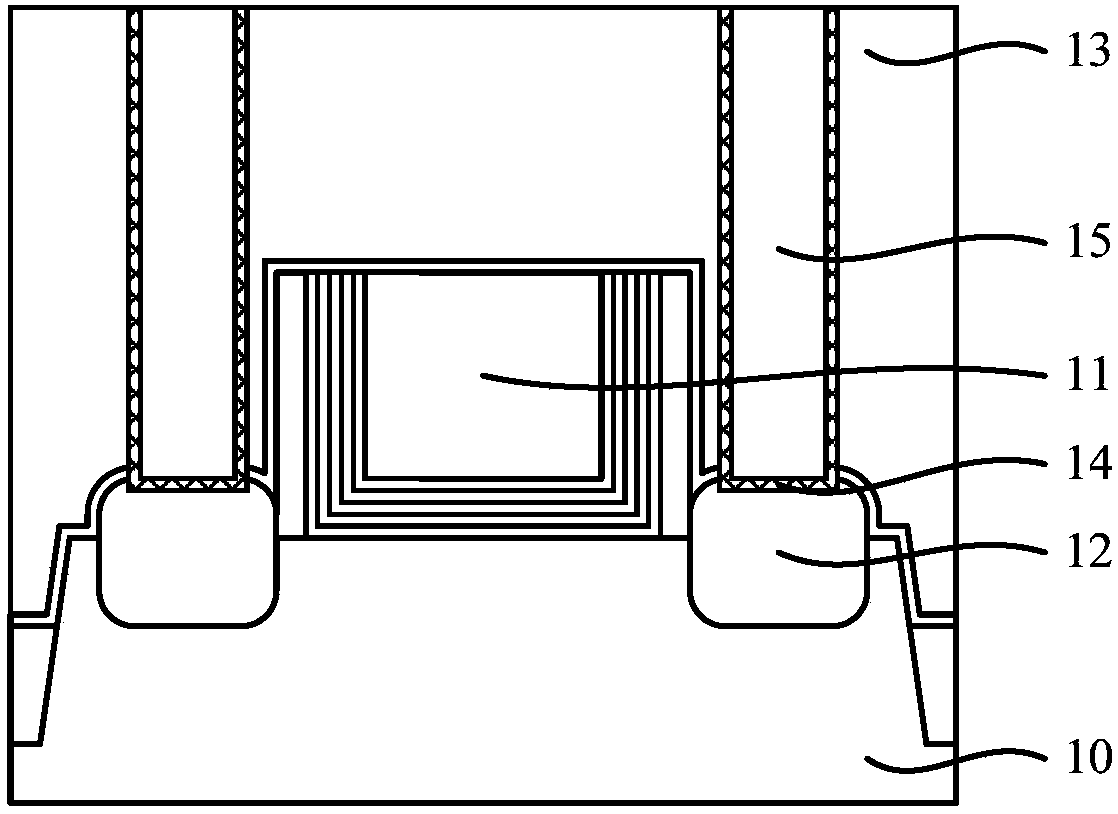

[0035] refer to figure 1 and figure 2 , shows a schematic cross-sectional structure corresponding to each step of a method for forming a semiconductor structure.

[0036] Such as figure 1 As shown, a substrate 10 is provided; a gate structure 11 located on the substrate 10 is formed; a stress layer 12 located on both sides of the gate structure is formed, and the stress layer 12 is doped to form a source and drain A doped region: a dielectric layer 13 is formed on the substrate 10 exposed by the gate structure 11 , and the dielectric layer 13 covers the stress layer 12 .

[0037] Such as figure 2 As shown, a plug 15 is formed in the dielectric layer 13 on the stress layer 12 , ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com