Method for optimizing the impedance continuity of PCB high-speed link

A high-speed link and continuity technology, applied in the server field, can solve problems such as reducing the integrity of the reference plane, affecting the quality of signal transmission, and affecting the distribution of current flow, so as to optimize the placement of capacitors, improve the quality of signal transmission, and optimize impedance. The effect of continuity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

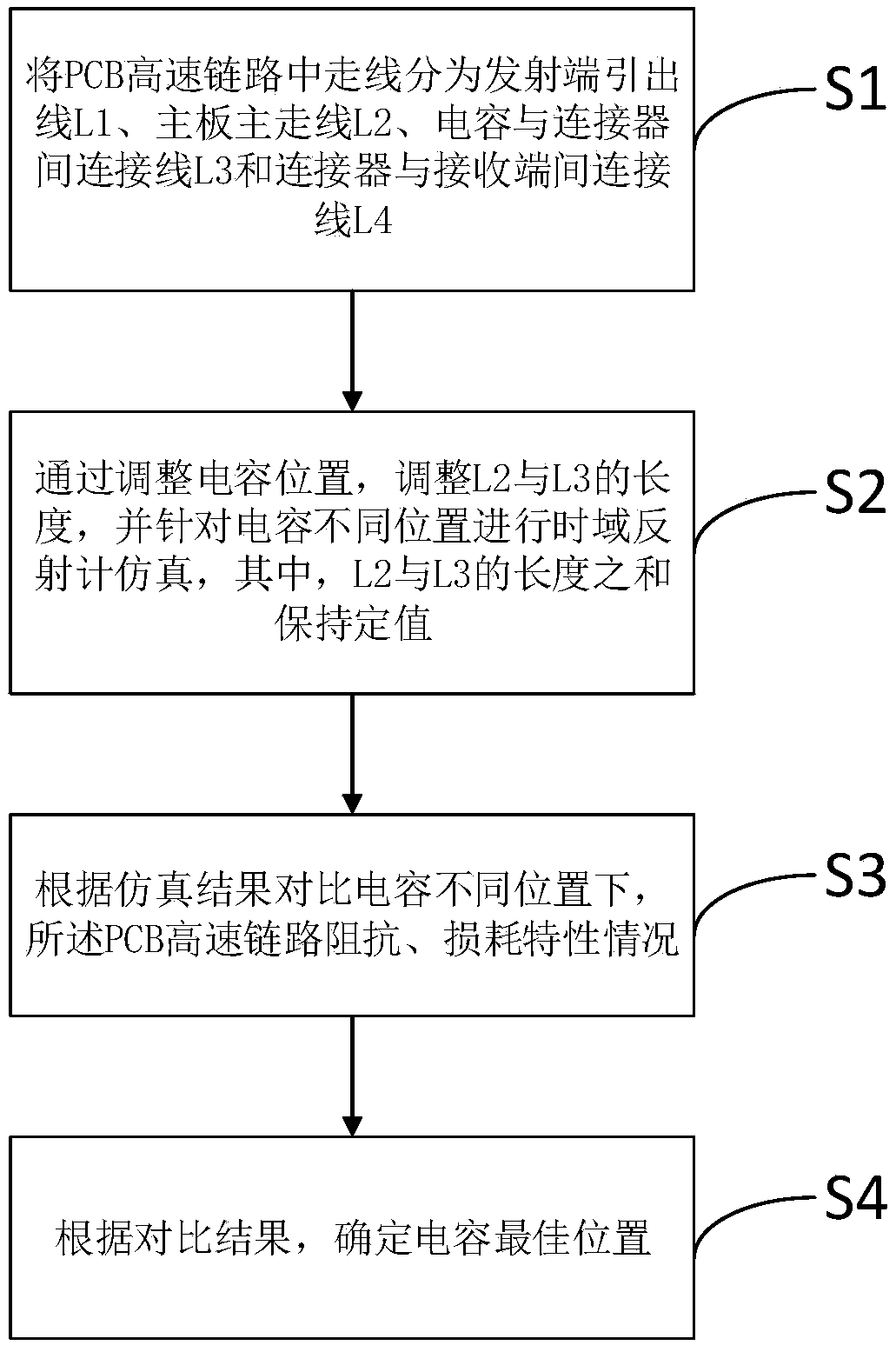

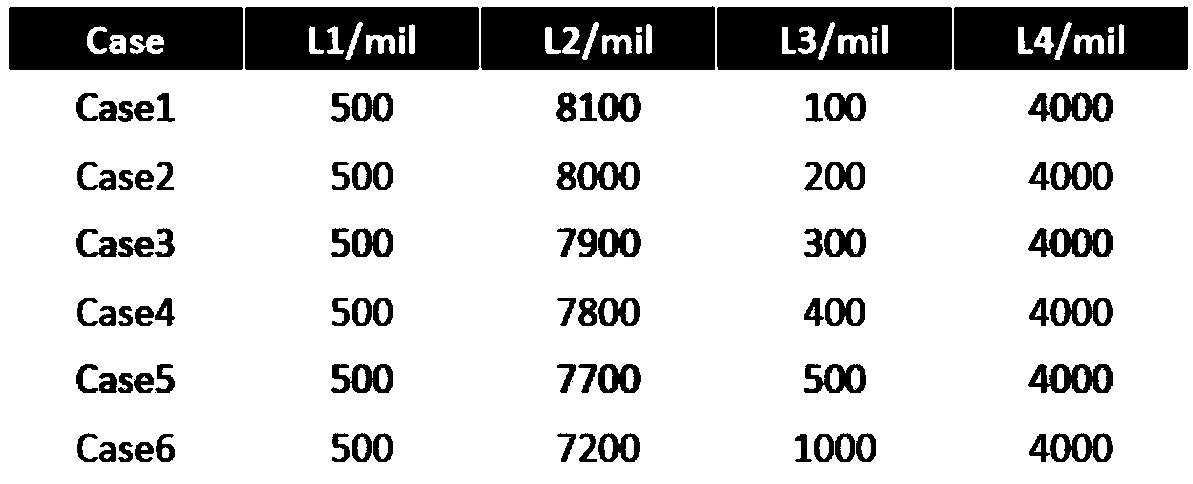

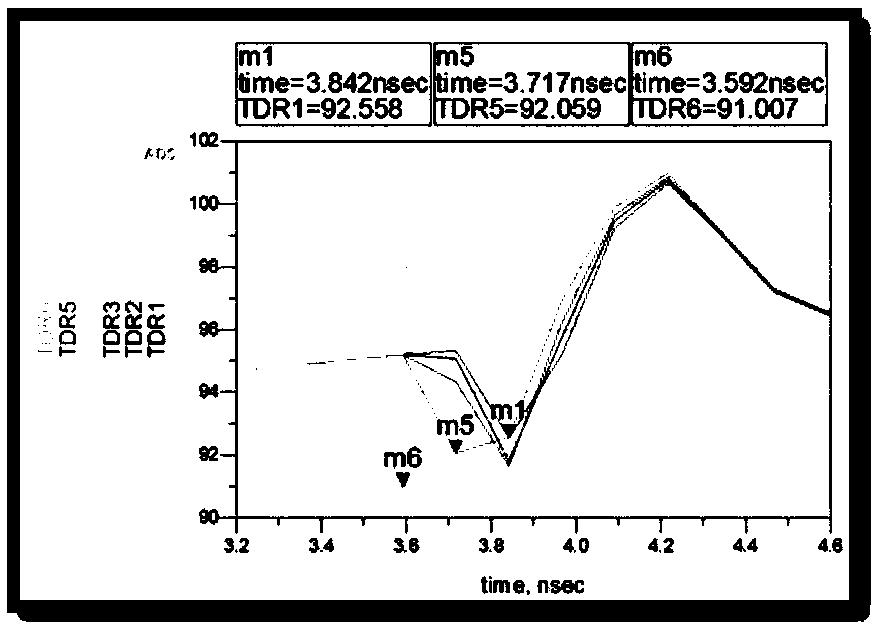

[0021] Such as Figure 1-5 as shown, figure 1 A flow chart of a method for optimizing PCB high-speed link impedance continuity proposed by the present invention; figure 2 It is a diagram of simulation items for different placement positions of capacitors; image 3 It is the simulation diagram of the link time domain reflectometer at different positions of the capacitor; Figure 4 It is the simulation diagram of the link insertion loss at different positions of the capacitor; Figure 5 It is the simulation diagram of the return loss of the link at different positions of the capacitor.

[0022] The present invention will be described in detail below in conjunction with the accompanying drawings and embodiments.

[0023] A method for optimizing PCB high-speed link impedance continuity, comprising the following steps:

[0024] S1: Divide the wiring in the PCB high-speed link into the lead-out line L1 of the transmitter, the main wiring L2 of the main board, the connecting li...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More