A chemical mechanical polishing process modeling method and device for a high-k metal gate

A technology of chemical mechanics and grinding technology, applied in design optimization/simulation, special data processing applications, CAD circuit design, etc., can solve problems such as circuit short circuit, dummy gate etching removal attack, metal not removed clean, etc., to achieve accurate surface The effect of defects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0059] DETAILED DESCRIPTION Hereinafter, embodiments of the present application will be described in detail in conjunction with the accompanying drawings.

[0060] In the device structure HKMG manufacturing process comprising two CMP process, an inter-dielectric layer (interlevel dielectric, ILD) a CMP process, a CMP process a further metal gate.

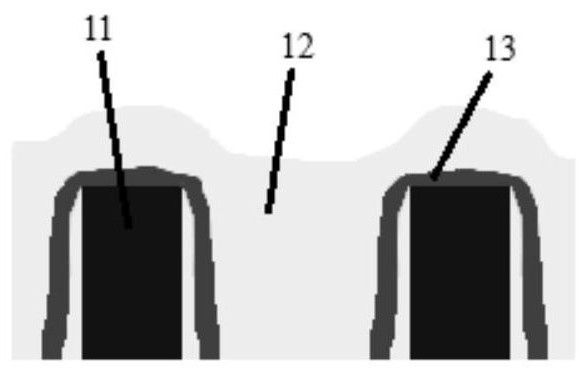

[0061] Wherein the interlevel dielectric layer CMP process requires polishing chip structures such as figure 1 Indicated. like figure 1 Shown, the chip comprises a dummy gate structure (dummy polysilicon gate material is generally i.e. polysilicon) 11, oxide layer 12 and the silicon nitride layer 13.

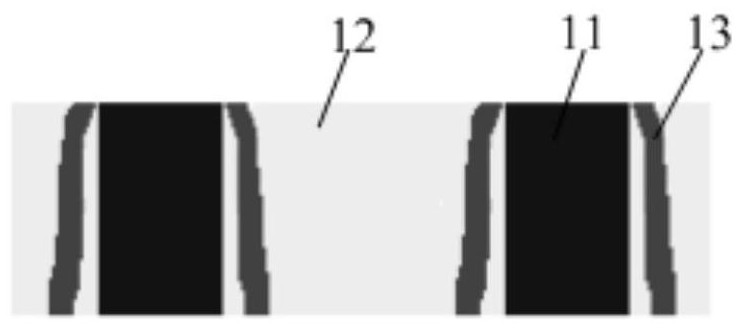

[0062] In the ideal case, inter-layer dielectric layer is set to produce a CMP process without dishing and erosion of the disk surface defects such as erosion, the dielectric layer of the chip structure after a CMP process terminates as interlayer figure 2 , The surface of the chip corresponding to a flat surface.

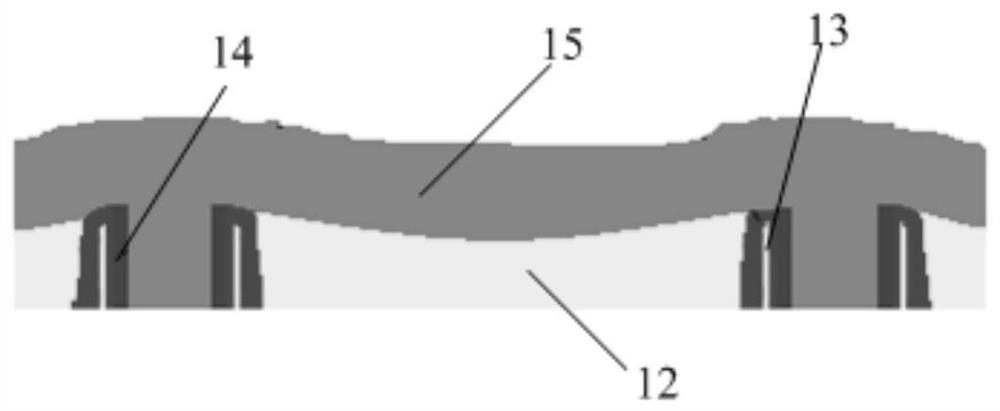

[0063] However, under ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More