A vdmos device and its manufacturing method

A manufacturing method and device technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems affecting the overall resistance of the body region, the source region occupies a large proportion of the body region, and the loss of control, so as to improve the overall performance and Reliability, improving the ultimate EAS capability, reducing the effect of body resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

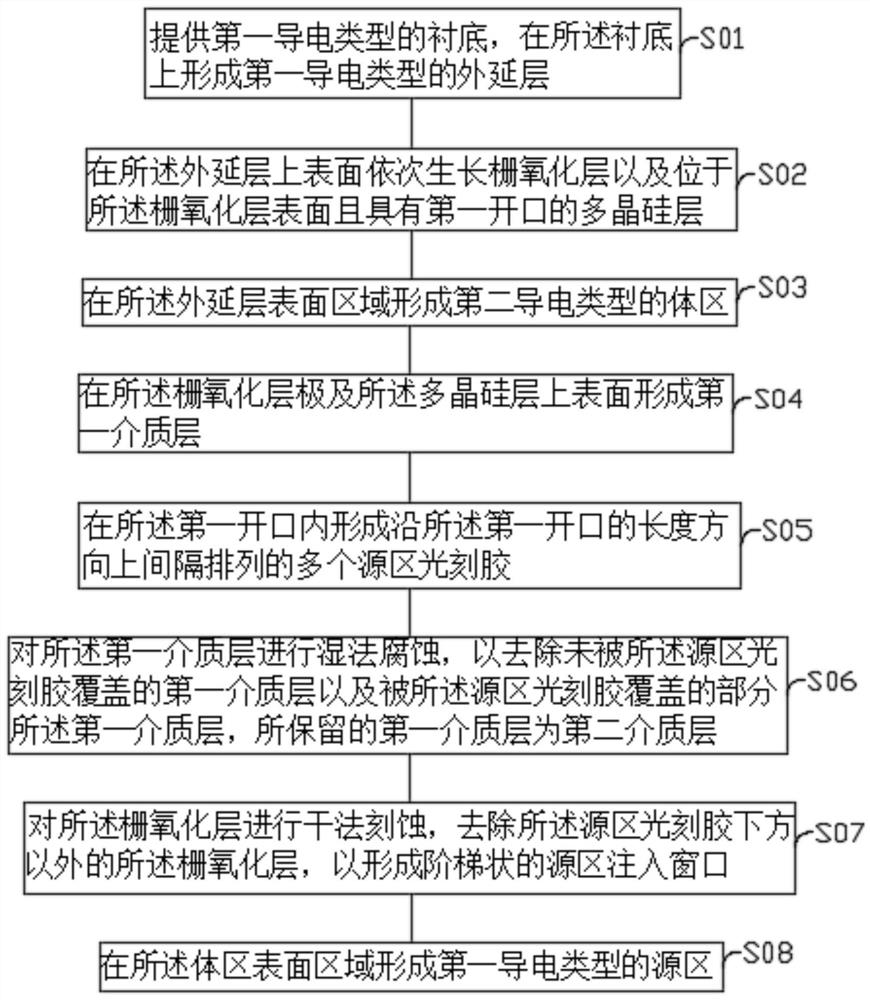

Method used

Image

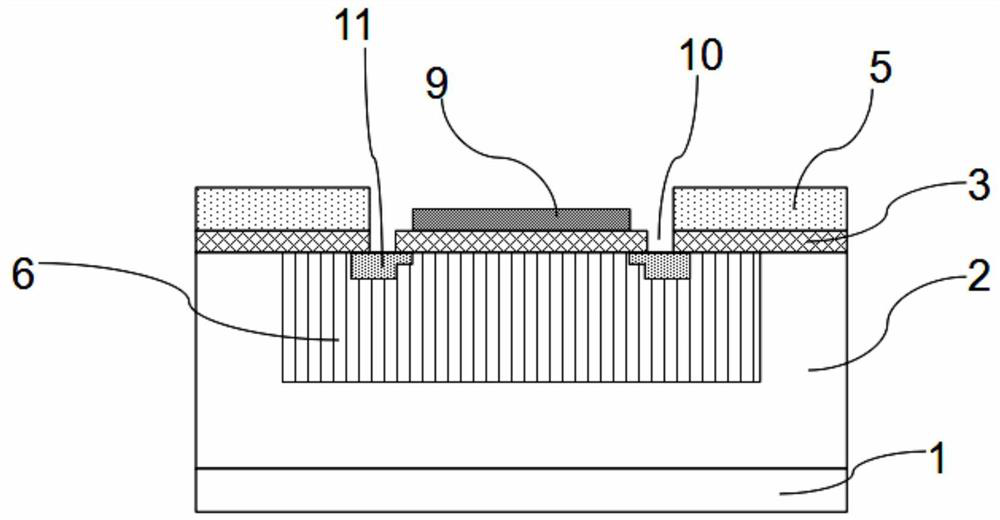

Examples

Embodiment Construction

[0016] In order to make the objects, technical solutions, and beneficial techniques of the present invention, the technical solutions in the embodiments of the present invention will be apparent from the drawings in the embodiments of the present invention, and Example is only a part of the embodiments of the invention, not all of the embodiments. Based on the embodiments of the present invention, all other embodiments obtained by those of ordinary skill in the art are in the range of the present invention without making creative labor premise.

[0017] In the description of the present invention, it is to be noted that the terms "center", "upper", "lower", "left", "right", "vertical", "horizontal", "within", "outside", etc. The orientation or positional relationship indicated is based on the orientation or positional relationship shown in the drawings, or the orientation or positional relationship that is typically placed in the use of the invention, is intended to describe the p...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More