System and method for detecting good product of integrated circuit

An integrated circuit and detection system technology, applied in the field of chip testing, can solve the problems of reducing the inconvenience of test items, occupying circuit area, and high ATE test cost, and achieve the effect of shortening test time and improving test efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The present invention will be further described below in conjunction with the accompanying drawings.

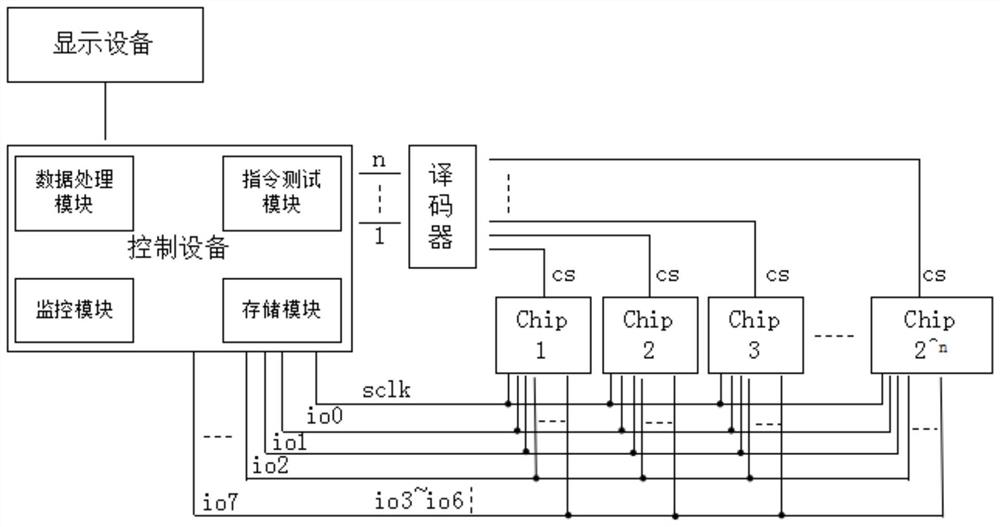

[0030] This embodiment provides an integrated circuit good product detection system, taking Octal SPI nor flash as an example, the system block diagram is as follows figure 1 As shown, it includes a control device, a display device, a decoder and several chips to be tested; the display device is connected to control transposition for displaying test results; the CS ports of several chips to be tested are connected to the control device through the decoder, and The clock interface sclk and data transmission interface io0~io7 of several chips to be tested adopt port multiplexing, that is, the clock interface sclk of each chip to be tested is connected to the same interface of the control device, and the data transmission interface of each chip to be tested io0~io7 respectively correspond to the same interface connected to the control device, such as figure 1 shown.

[...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More