Memory formation method

A memory and semiconductor technology, which is used in the manufacture of electrical solid-state devices, semiconductor devices, and semiconductor/solid-state devices. possibility, strain reduction, effect of grain size reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] A memory and its forming method proposed by the present invention will be described in detail below with reference to the drawings and specific embodiments.

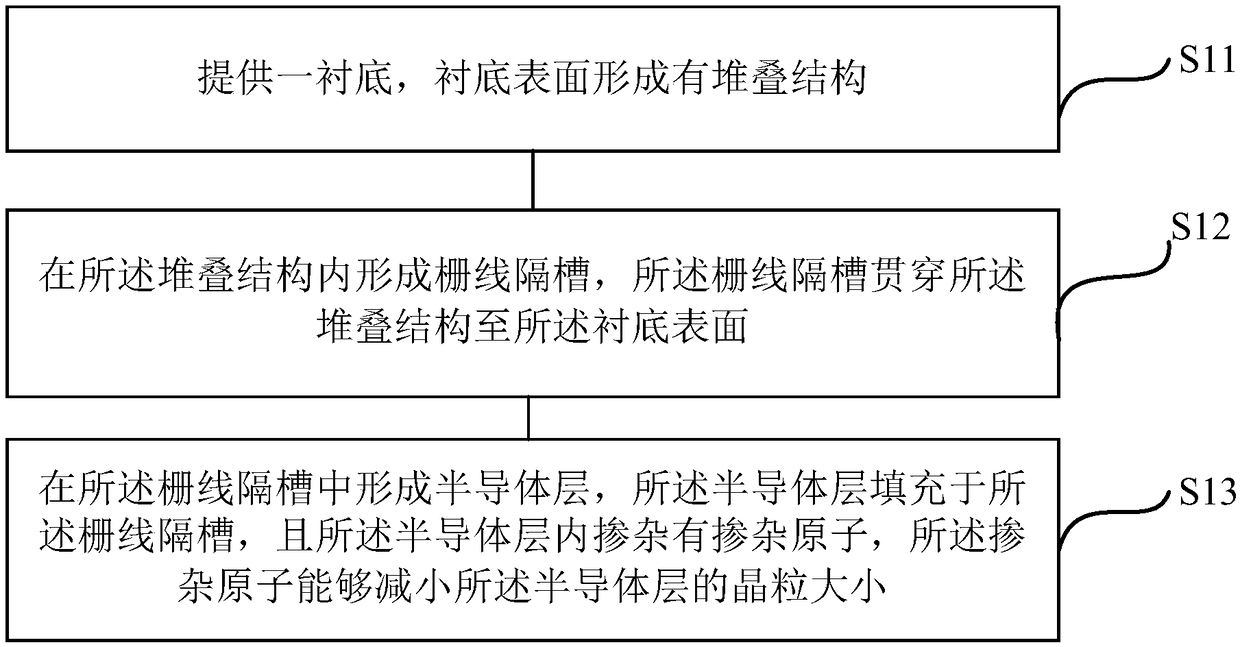

[0023] see figure 1 , is a flow chart of the method for forming the memory in a specific implementation manner. The forming method of the memory includes the following steps: S11: Provide a substrate, and a stack structure is formed on the surface of the substrate. S12: Forming a gate line spacer in the stack structure, the gate line spacer penetrating through the stack structure to the surface of the substrate. S13: forming a semiconductor layer in the gate line spacer, the semiconductor layer is filled in the gate line spacer, and the semiconductor layer is doped with dopant atoms, and the dopant atoms can reduce the The grain size of the semiconductor layer.

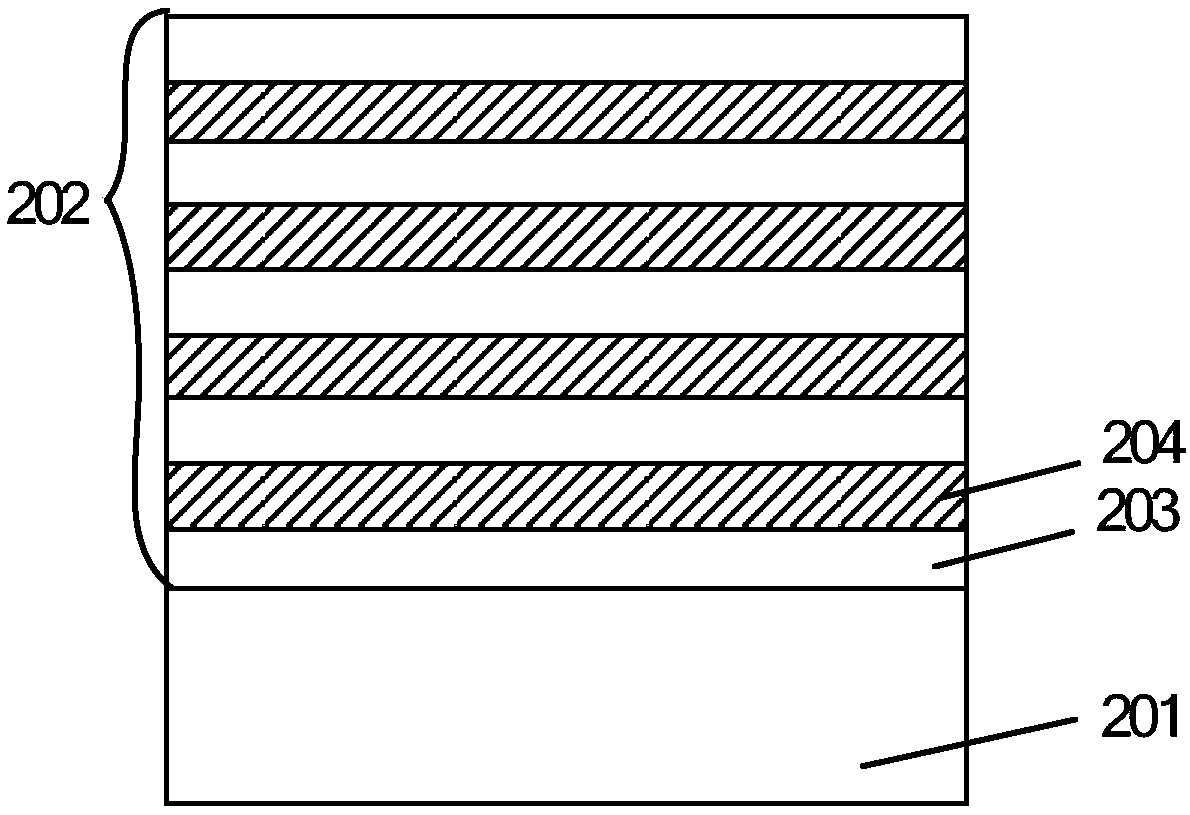

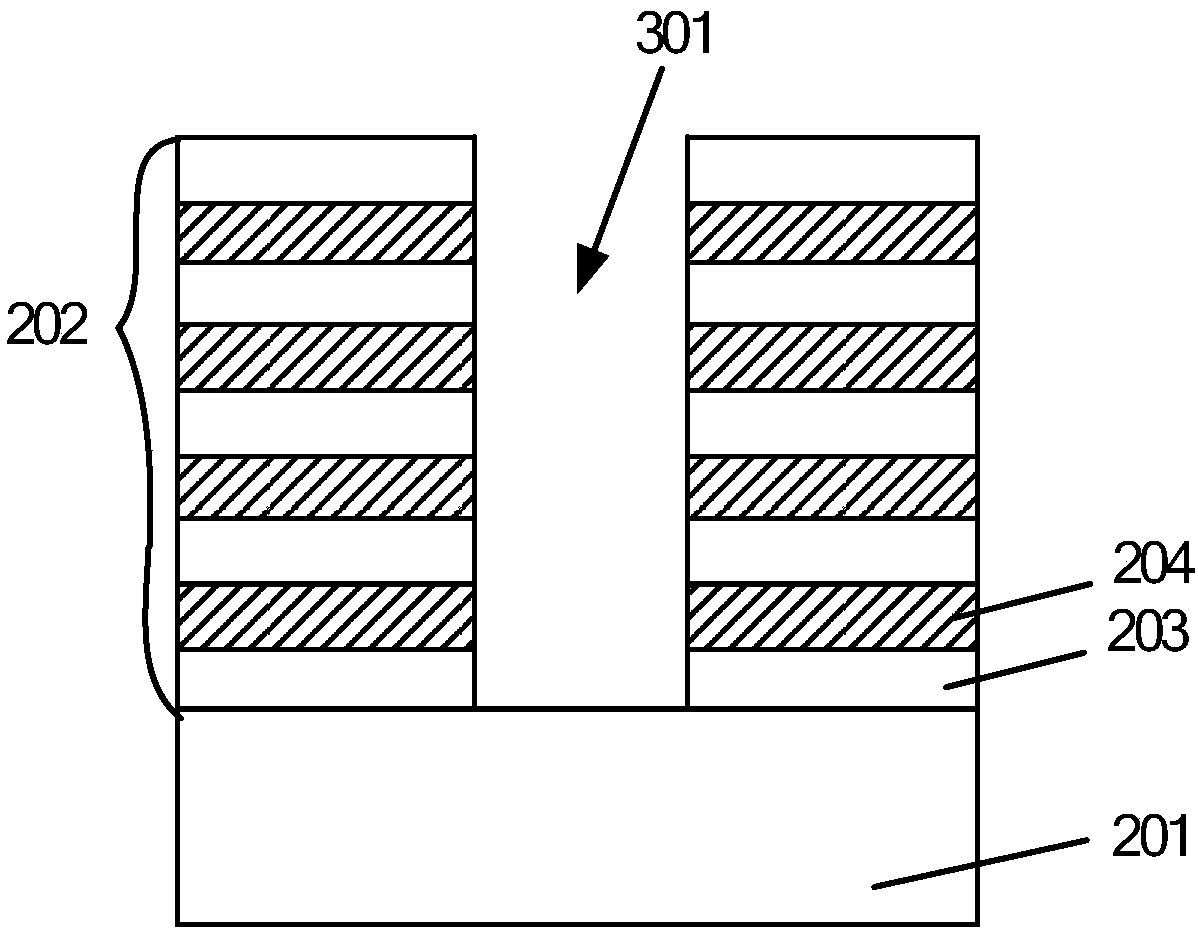

[0024] see Figure 2 to Figure 6 , is a schematic structural diagram of a memory forming process according to a specific embodiment of the present in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More