Semiconductor device and manufacturing method thereof

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, transistors, electrical components, etc., can solve the problem of high contact resistivity of PMOS

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0048] A method of fabricating a semiconductor device includes:

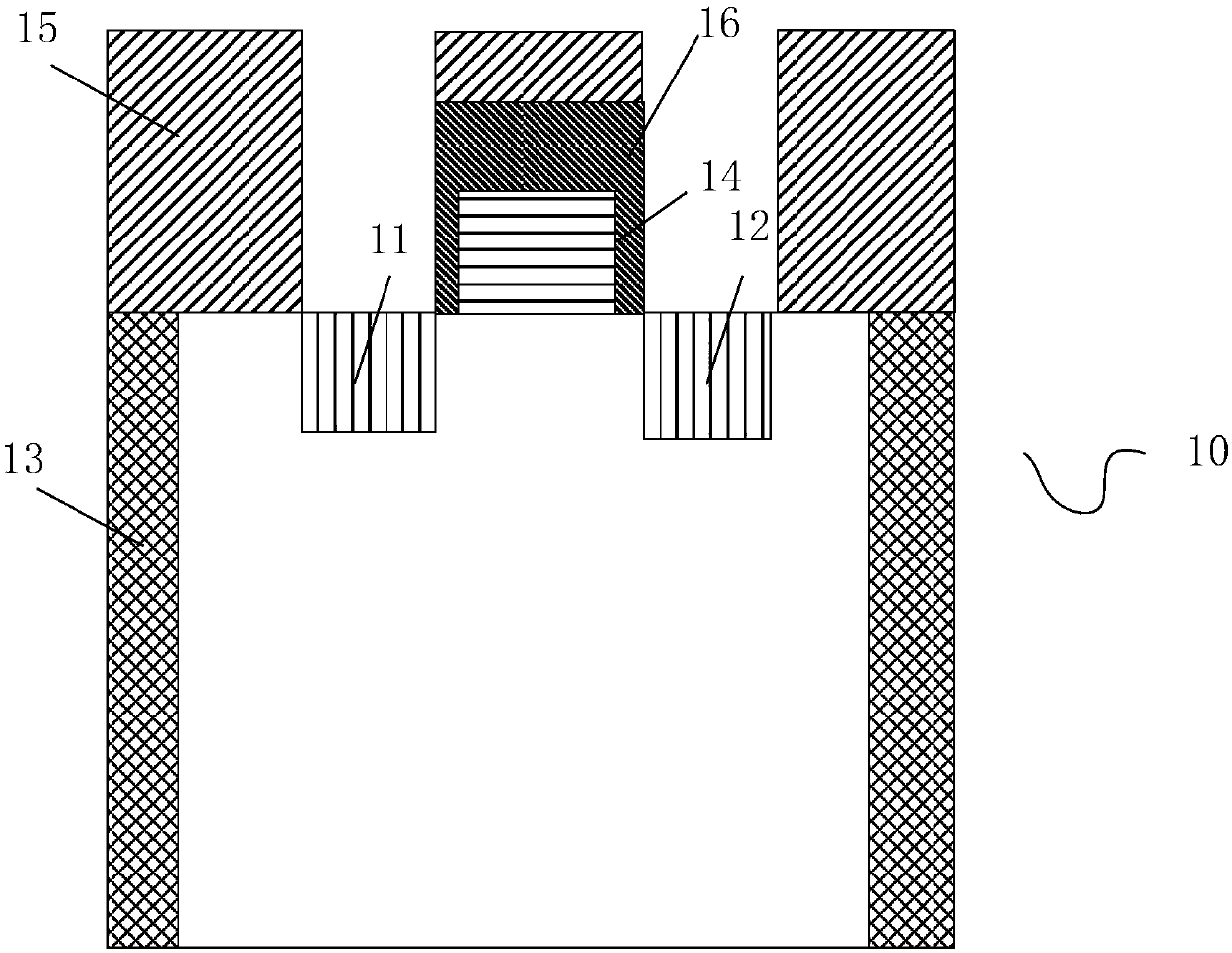

[0049] Such as figure 1 As shown, a semiconductor preparation 10 is provided, and the semiconductor preparation 10 includes a substrate, a shallow trench isolation 13 located in the substrate, a source region 11 and a drain region 12 located in the substrate, above and between the source and drain regions Between the gate 14, the sidewall layer 16 on the surface of the gate 14, and the isolation dielectric layer 15 above the substrate and on both sides of the source and drain regions and on the sidewall layer 16. Wherein, a through hole is formed between the isolation dielectric layer 15 and the side wall layer 16 . The substrate is a Si substrate, the source and drain regions are GeSi source and drain regions doped with B, the gate 14 is a high-K gate, the sidewall layer 16 is a silicon dioxide layer, and the isolation dielectric layer 15 is a silicon dioxide layer. It should be noted, figure 1 For the con...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electron work function | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More