Multi-chip stacked packaging method and multi-chip stacked package body

A technology of stacking packages and packaging methods, which is applied in the manufacture of semiconductor devices, electrical solid devices, semiconductor/solid devices, etc., can solve problems such as increased impedance, poor heat dissipation mechanism, poor heat conduction, etc., and achieves improved thermal conductivity and packaging Thin thickness, good electrical conductivity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The specific implementation manners of the multi-chip stack packaging method and the multi-chip stack package body provided by the present invention will be described in detail below with reference to the accompanying drawings.

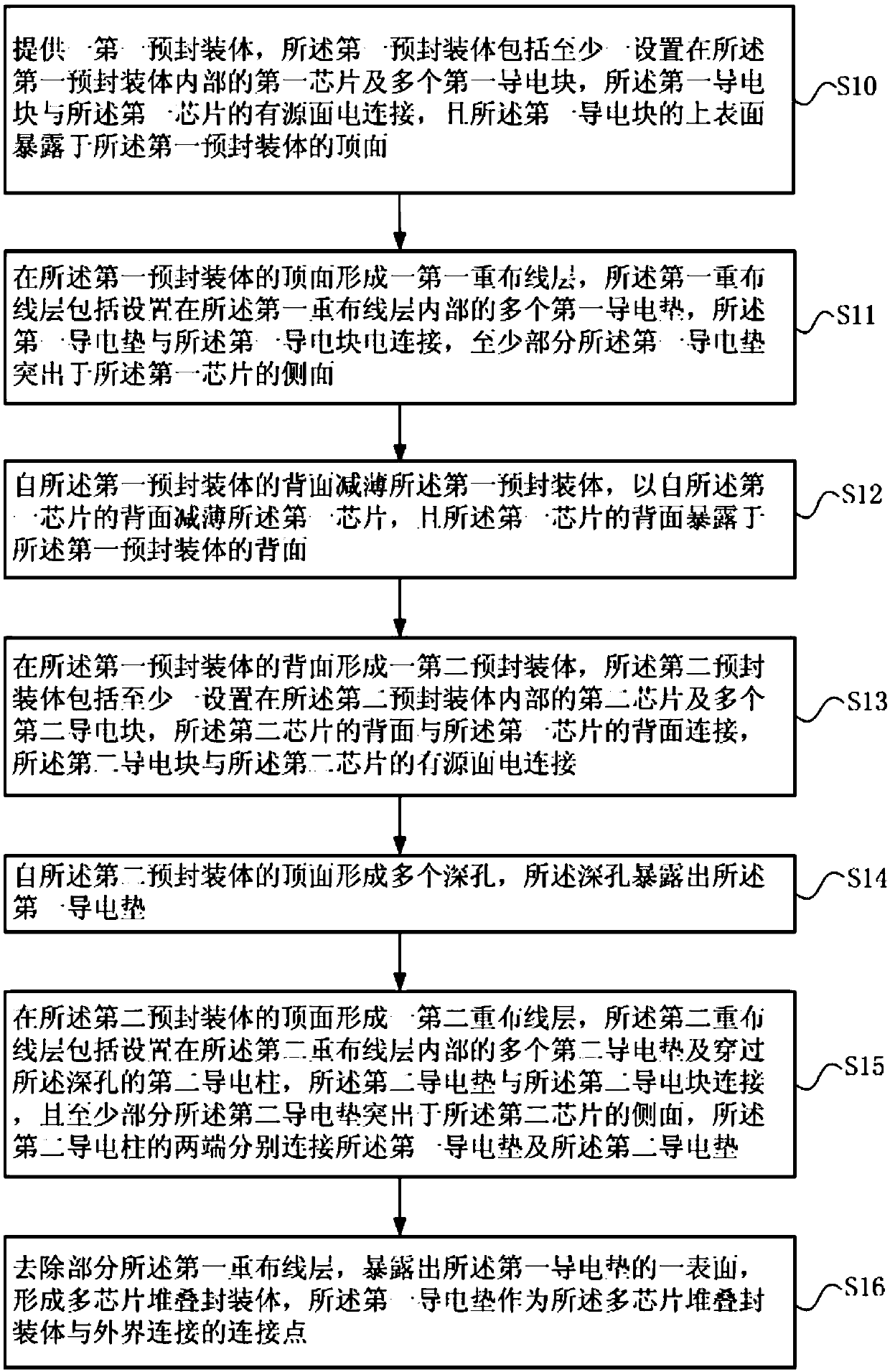

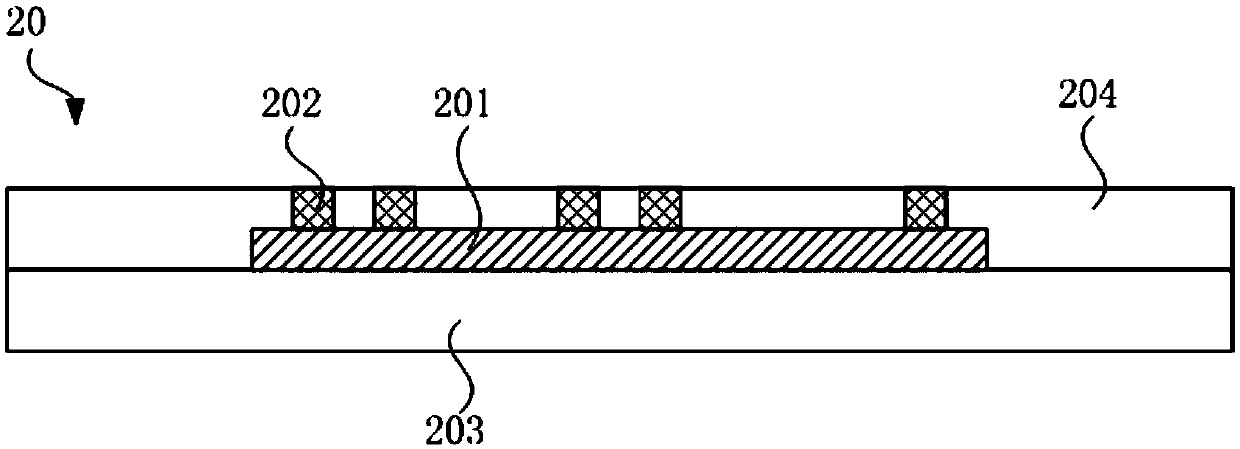

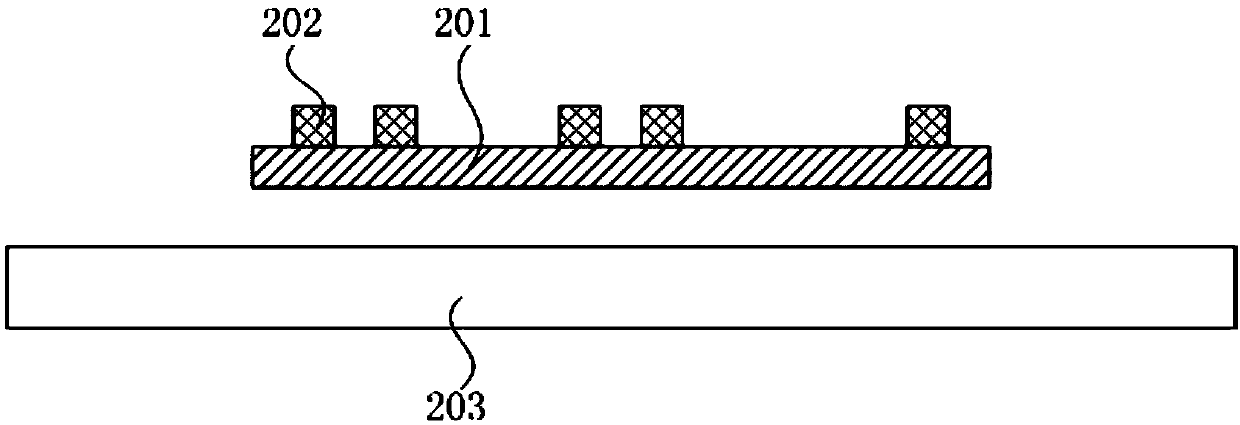

[0021] figure 1 It is a schematic diagram of the steps of the multi-chip stack packaging method of the present invention. see figure 1The multi-chip stack packaging method of the present invention includes the following steps: step S10, providing a first pre-package body, the first pre-package body including at least one first chip disposed inside the first pre-package body and a plurality of A first conductive block, the first conductive block is electrically connected to the active surface of the first chip, and the upper surface of the first conductive block is exposed to the top surface of the first prepackage body; step S11, A first redistribution layer is formed on the top surface of the first prepackage, the first redistribution layer ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More