A 6T & 6TPPNN unit layout method based on minimum width constraint

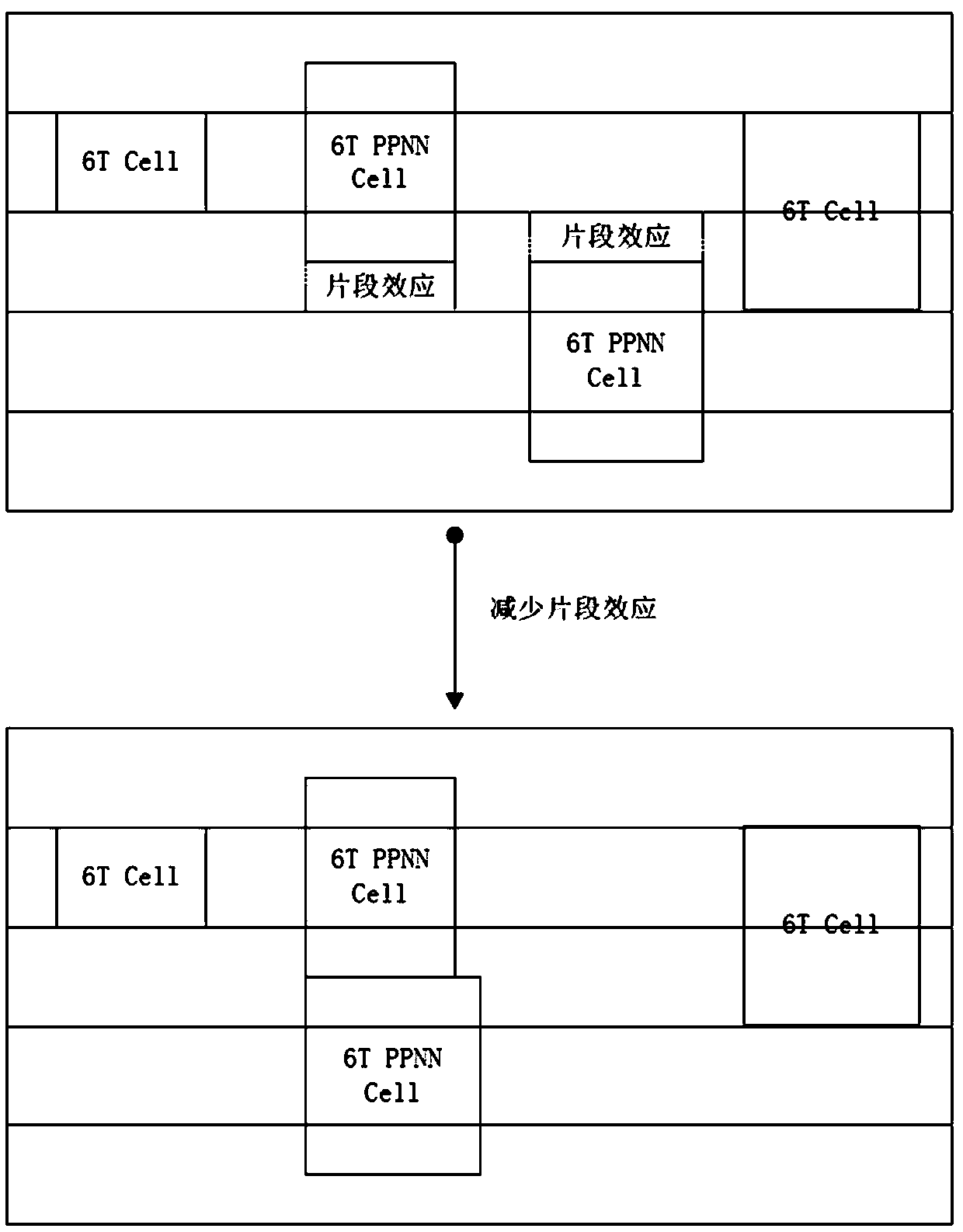

A layout method and width technology, applied in the field of VLSI physical design automation, can solve problems such as the impact of circuit layout performance, achieve the effect of reducing fragment effects and improving circuit performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0061] The preferred embodiments of the present invention will be described below in conjunction with the accompanying drawings. It should be understood that the preferred embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

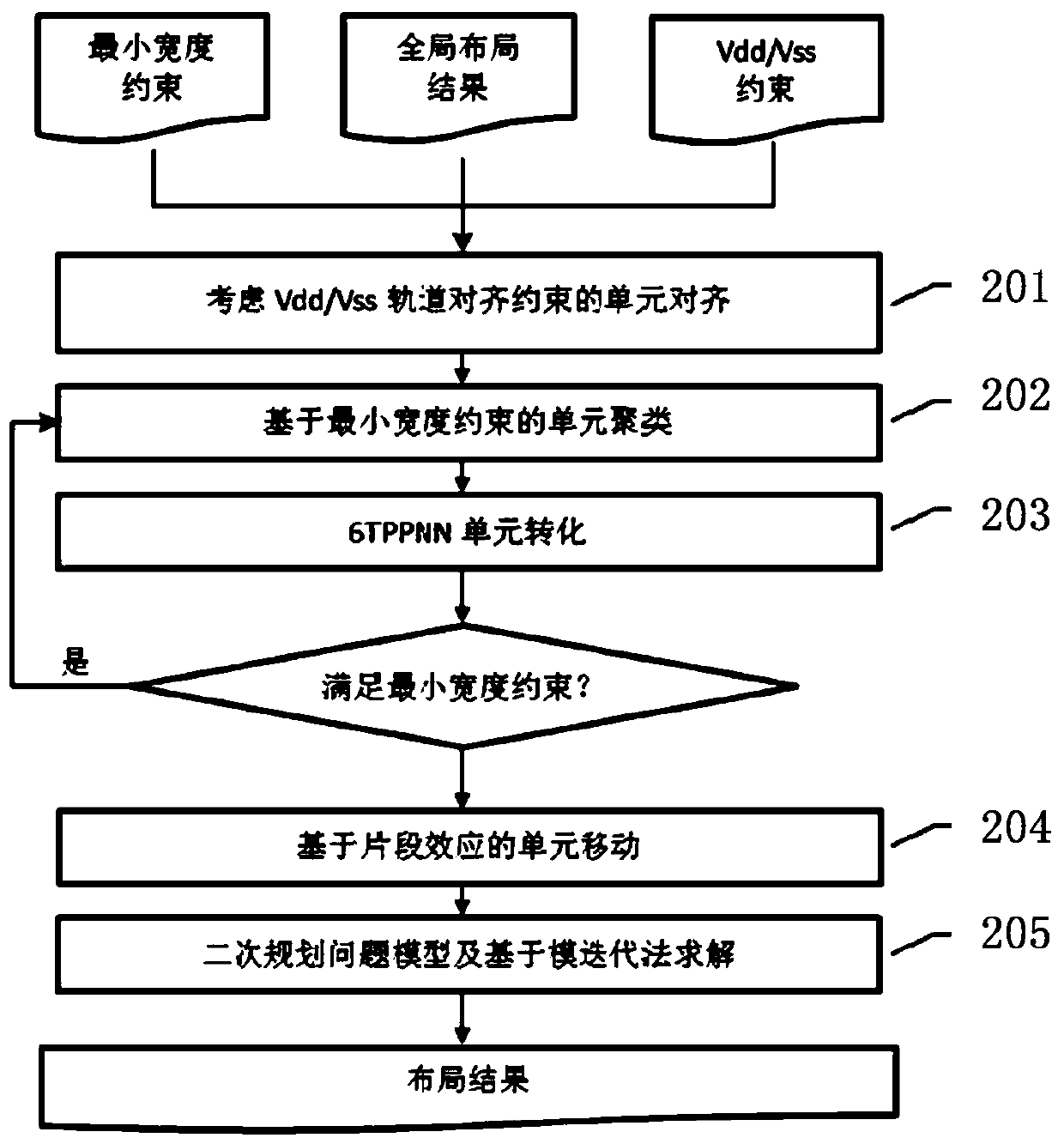

[0062] figure 2 It is a flow chart of the 6T&6TPPNN unit layout method based on the minimum width constraint according to the present invention, which will be referred to below figure 2 , the 6T&6TPPNN cell layout method based on the minimum width constraint of the present invention is described in detail.

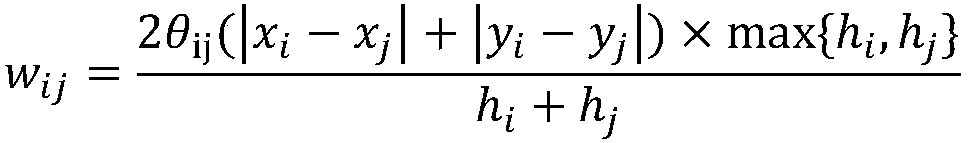

[0063] The mathematical model of the 6T&6TPPNN unit layout method based on the minimum width constraint of the present invention is described as follows:

[0064] Firstly, given a C={c with n standard units 1 ,c 2 ,...,c n} and m lines E={e 1 ,e 2 ,...,e m}'s 6T&6TPPNN cell global layout. The layout area is a rectangular frame, where (0,0) and (W,H) ar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More