Method for correcting a mask layout and method of fabricating a semiconductor device using the same

A mask and layout technology, applied in the field of correcting mask layout and using it to manufacture semiconductor devices, to achieve the effect of compensating for deformation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] Hereinafter, embodiments of the inventive concept will be described in detail with reference to the accompanying drawings.

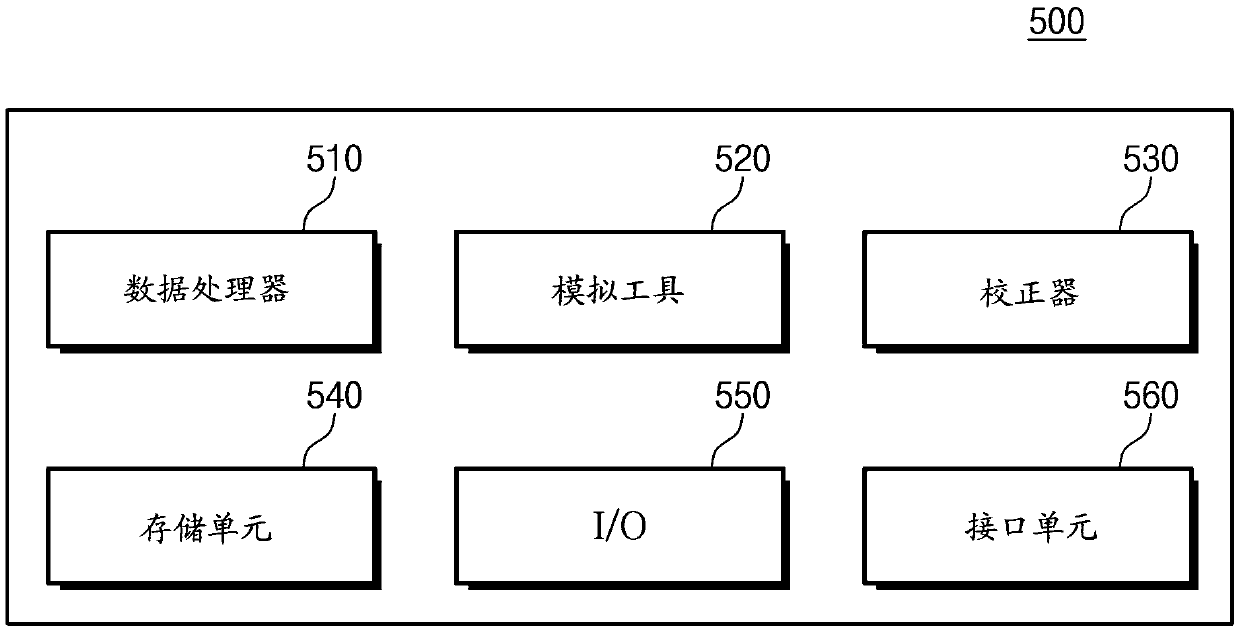

[0019] figure 1 is a schematic block diagram illustrating a computer system for performing a method of correcting a mask layout according to some embodiments of the inventive concepts.

[0020] refer to figure 1 , the computer system 500 may include a data processor 510 for processing various data, a simulation tool 520 for performing lithography simulations on the designed mask layout, and a corrector 530 that compares The generated data is compared with the expected data and the mask layout is corrected when the difference between the generated data and the expected data exceeds the allowable range. The computer system 500 may also include a storage unit 540 capable of storing various data. The storage unit 540 may include a hard disk and / or a nonvolatile semiconductor memory device (eg, a flash memory device, a phase change memory device, an...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap