soi LIGBT device with diode-clamped carrier storage layer

A carrier storage and diode clamping technology, applied in semiconductor devices, electrical components, circuits, etc., to achieve the effects of excellent short-circuit resistance, reduced conduction voltage drop, and low saturation current density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

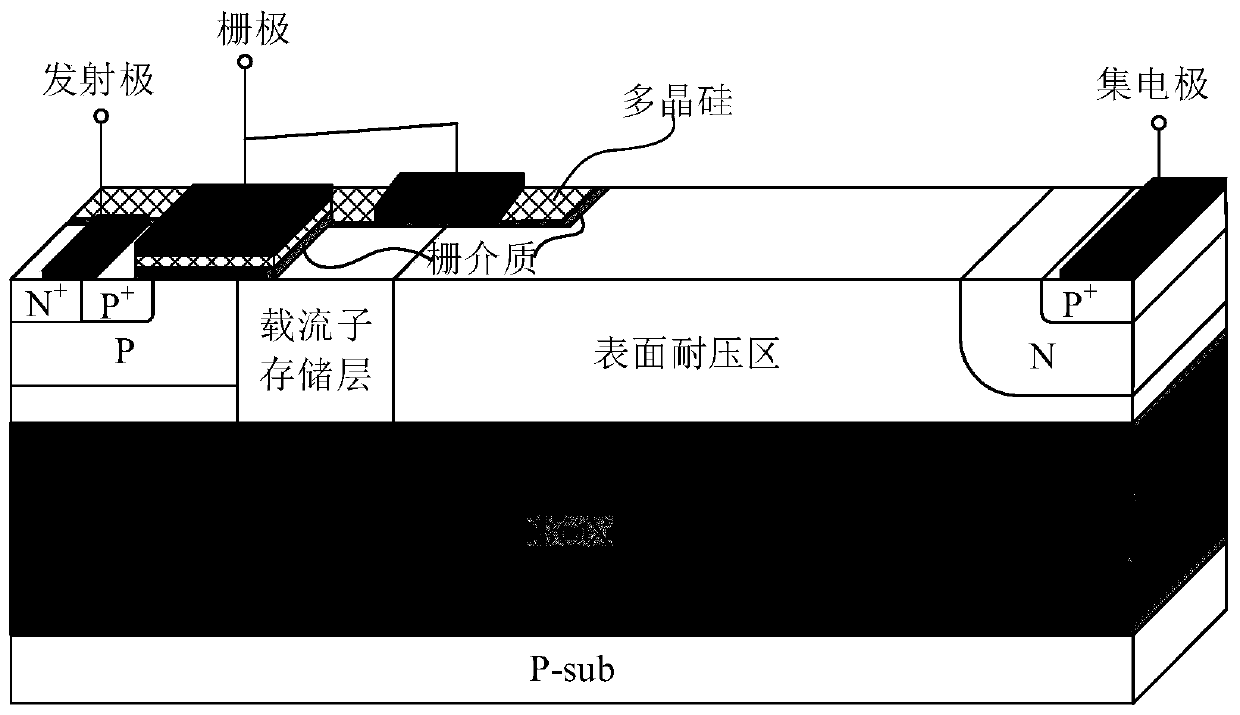

Problems solved by technology

Method used

Image

Examples

Embodiment 1

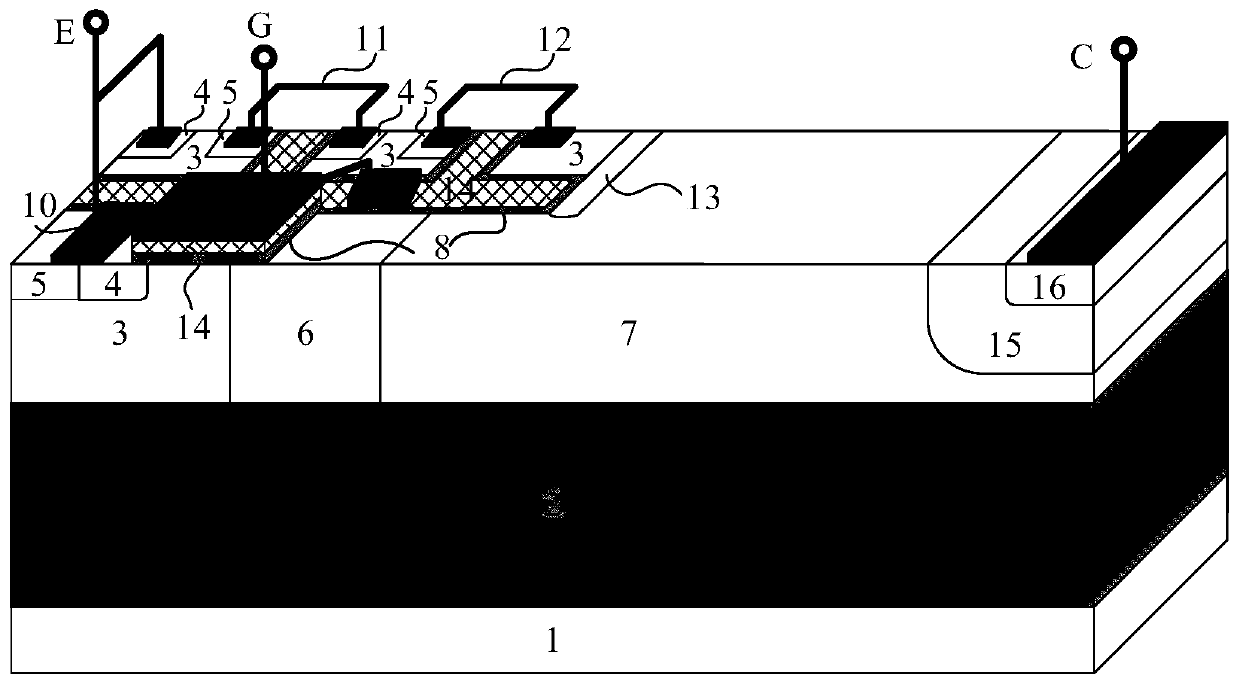

[0036] An embodiment of the present invention provides an SOI LIGBT device with two diode clamps, such as Figure 2 ~ Figure 3 Commonly shown, it includes a semiconductor substrate 1 , a buried oxide layer region 2 on the semiconductor substrate 1 , and a semiconductor layer (SOI layer) on the buried oxide layer region 2 . The semiconductor layer includes a P-type semiconductor base region 3, a gate region, an N-type carrier storage region 6, a surface withstand voltage region 7, a P-type electric field shielding region 13, an N-type semiconductor buffer region 15, and a P-type collector region 16, The P-type semiconductor base region 3 and the gate region are located on one side of the semiconductor layer, the N-type semiconductor buffer zone 15 is located on the other side of the semiconductor layer, and the N-type carrier storage region 6 is located next to the P-type semiconductor base region 3, and the P-type electric field shielding The region 13 is located next to the g...

Embodiment 2

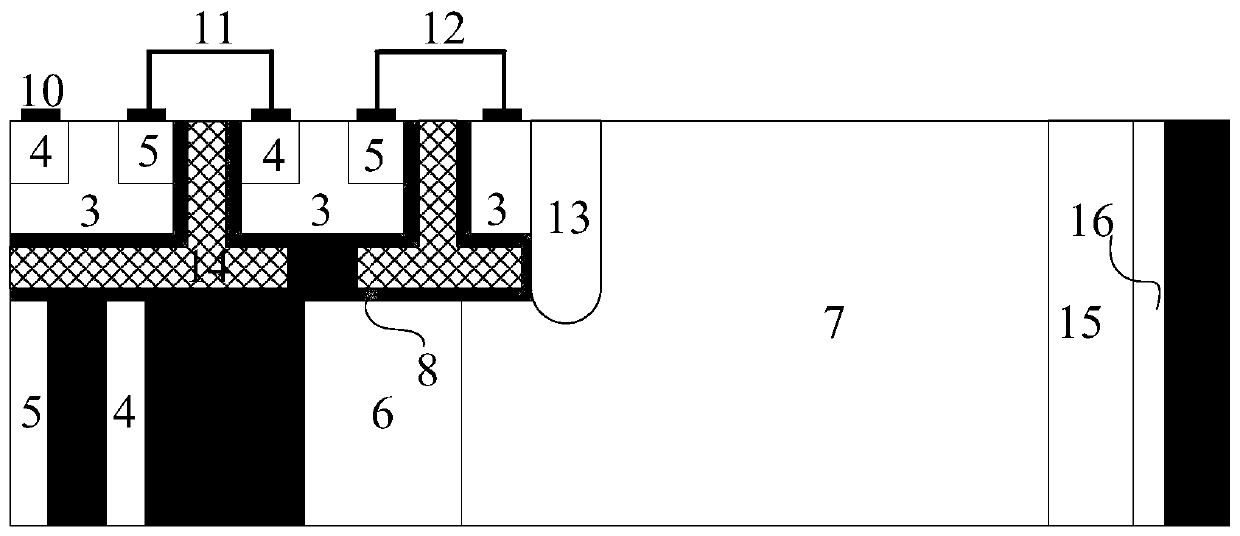

[0047] An embodiment of the present invention provides an SOI LIGBT device with three diode clamps, such as Figure 4 ~ Figure 5 Commonly shown, it includes a semiconductor substrate 1 , a buried oxide layer region 2 on the semiconductor substrate 1 , and a semiconductor layer (SOI layer) on the buried oxide layer region 2 . The semiconductor layer includes a P-type semiconductor base region 3, a gate region, an N-type carrier storage region 6, a surface withstand voltage region 7, a P-type electric field shielding region 13, an N-type semiconductor buffer region 15, and a P-type collector region 16, The P-type semiconductor base region 3 and the gate region are located on one side of the semiconductor layer, the N-type semiconductor buffer zone 15 is located on the other side of the semiconductor layer, and the N-type carrier storage region 6 is located next to the P-type semiconductor base region 3, and the P-type electric field shielding The region 13 is located beside the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More