Small-area low-power-consumption clock data recovery circuit

A clock data recovery, low-power technology, applied in the direction of electrical components, power automatic control, etc., can solve the problems of CDR performance limitation, loss of flexibility, inability to set loop parameters reasonably, etc., to reduce chip area, The effect of reducing area, balancing build speed and noise performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] Embodiments of the present invention will be described below in conjunction with the accompanying drawings.

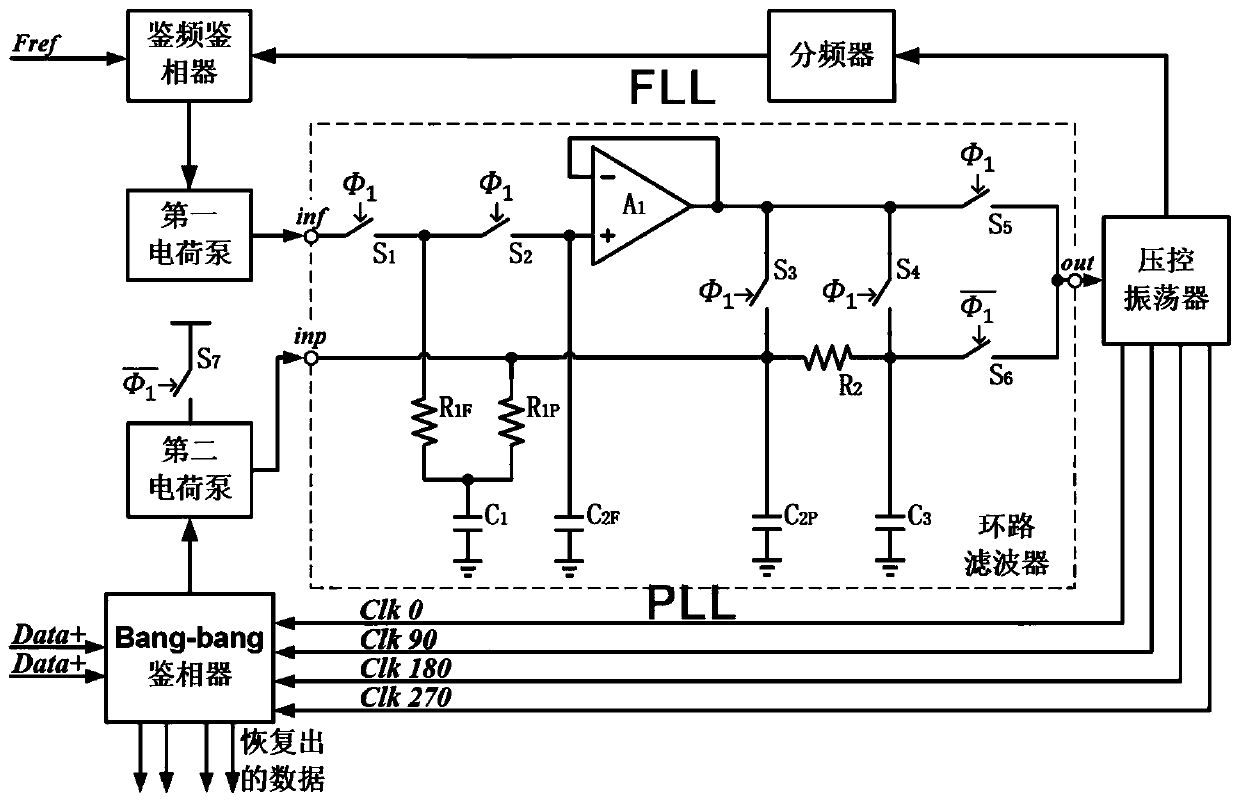

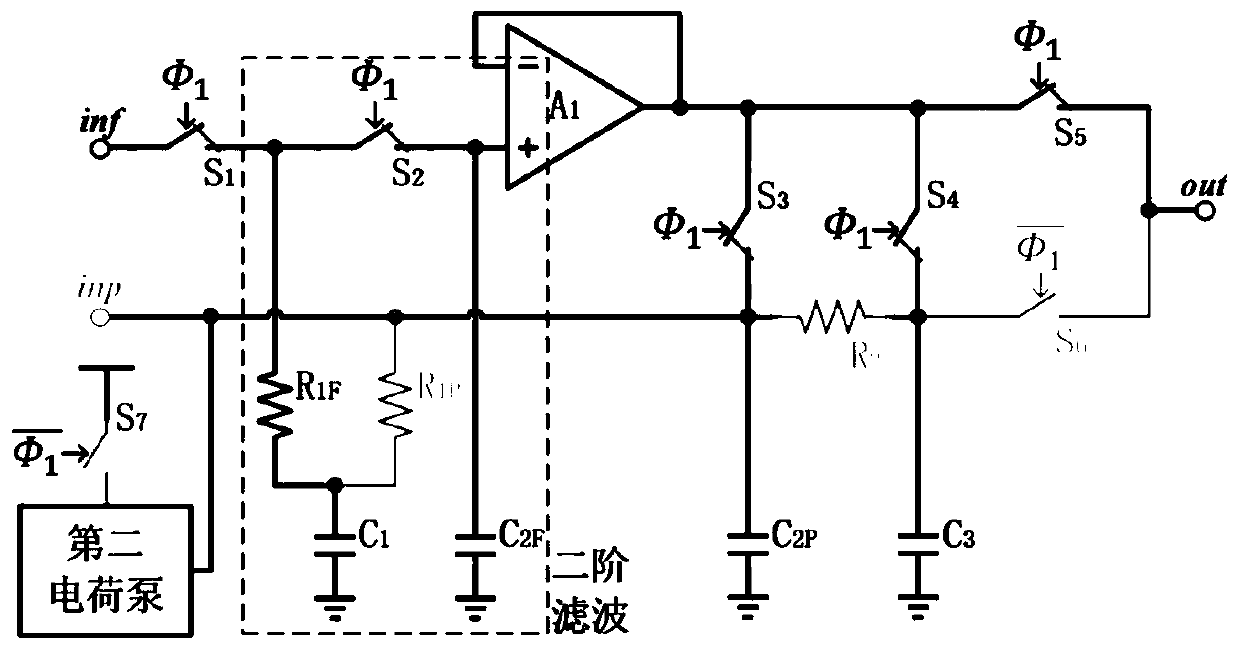

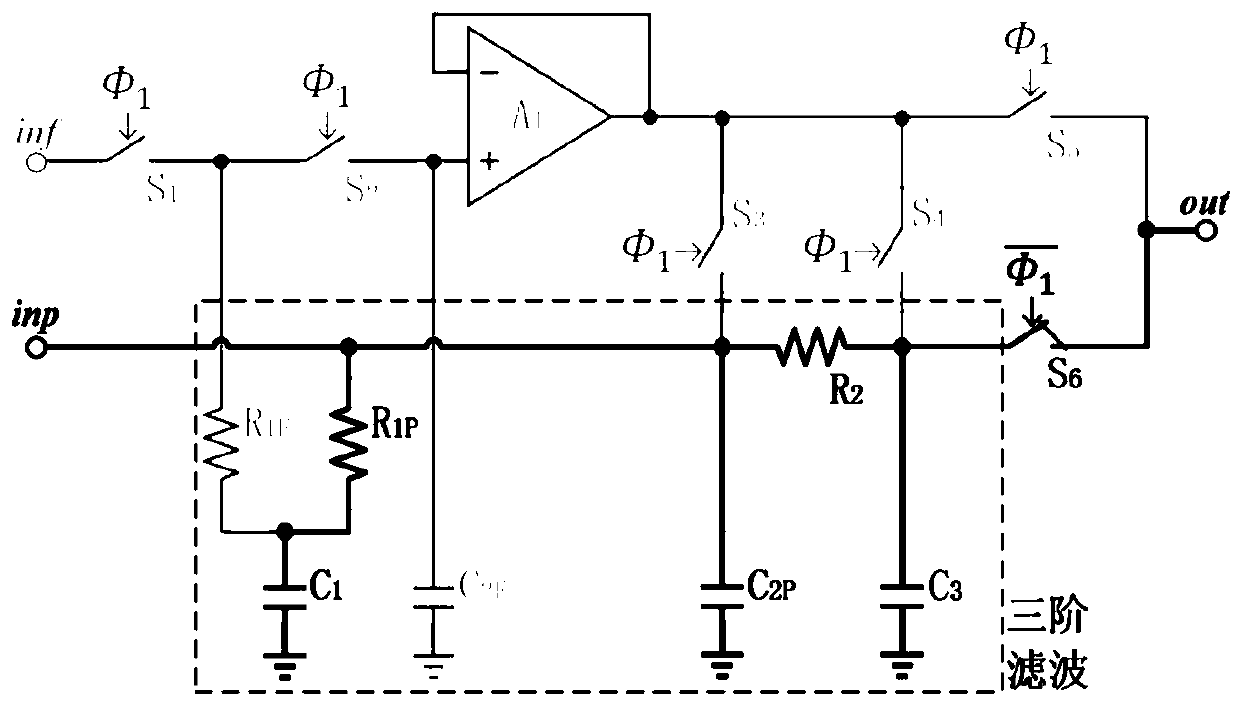

[0021] Such as figure 1 As shown, the present invention provides a clock data recovery circuit with small area and low power consumption, including frequency and phase detector, frequency divider, first charge pump, second charge pump, Bang-bang phase detector, loop filter device, voltage controlled oscillator, seventh switch S 7 . Wherein, the first input terminal of the frequency and phase detector is connected to the input signal Fref, the second input terminal of the frequency and phase detector is connected to the output terminal of the frequency divider, and the input terminal of the frequency divider is connected to the first input terminal of the voltage controlled oscillator. One output terminal is connected; The input terminal of described voltage-controlled oscillator is connected with the output terminal of loop filter, and the second, third, fourt...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More