Silicon wafer surface treatment method

A silicon wafer surface and treatment method technology, applied in the field of silicon wafer processing, can solve problems affecting the electrical performance of integrated circuits, device life reduction, device failure, etc., and achieve the effect of monitoring the metal level on the silicon wafer surface

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

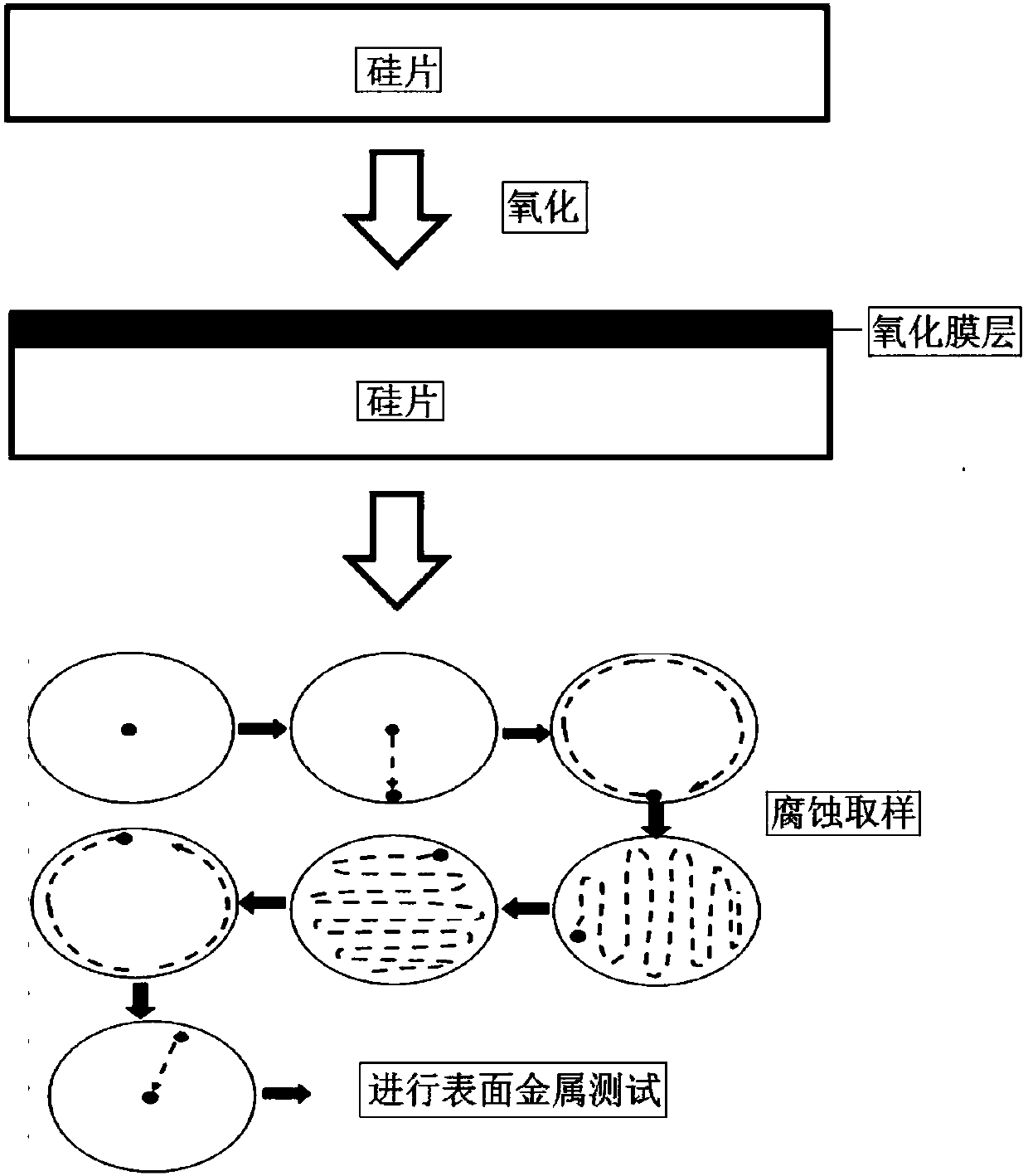

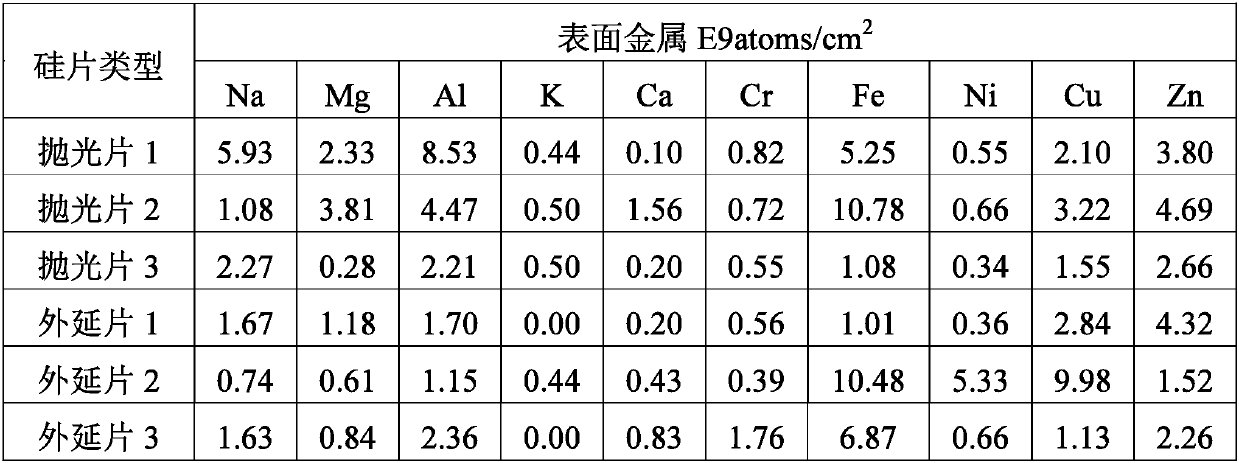

[0022] This embodiment is described by taking a 12-inch polished silicon wafer and an epitaxial silicon wafer as examples.

[0023] 1. Take 6 pieces of polished wafers from the same batch, and take 3 pieces for epitaxial growth, and then conduct metal analysis tests on the remaining 3 pieces of 12-inch polished silicon wafers and 3 pieces of 12-inch epitaxial silicon wafers;

[0024] 2. Use the surface particle tester KLA Tencor SP1 to test the surface particles of 6 pieces of 12-inch silicon wafers to ensure that the surface is not contaminated by large areas of particles;

[0025] 3. Put three 12-inch polished silicon wafers and three 12-inch epitaxial wafers into a high-temperature oxidation furnace respectively, inject high-purity oxygen and argon, and carry out high-temperature oxidation at 1100 ° C, and grow an oxide film of 1000 angstroms on the surface.

[0026] 4. To prepare sampling solution, use TAMA-AA10-H 2 o 2 Specification, 35%H 2 o 2 (impurity content less ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More