A low-power-consumption switching algorithm applied to an SAR ADC

A low-power, switching technology, applied in the field of low-power switching algorithms, can solve problems such as comparator dynamic offset and ADC reduction, and achieve the effects of reducing offset, improving performance, and saving capacitor area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] Embodiments of the present invention will be described below in conjunction with the accompanying drawings.

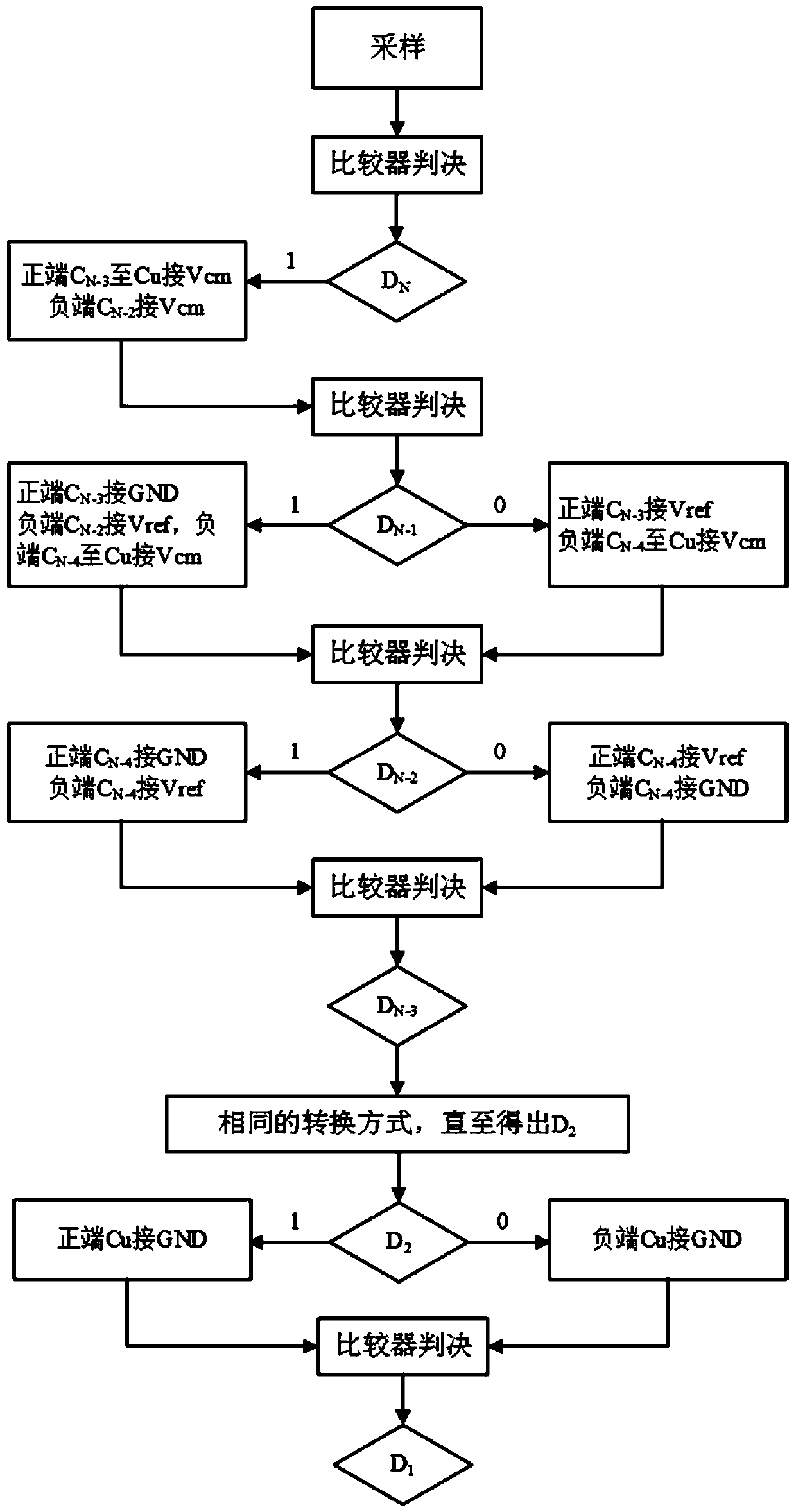

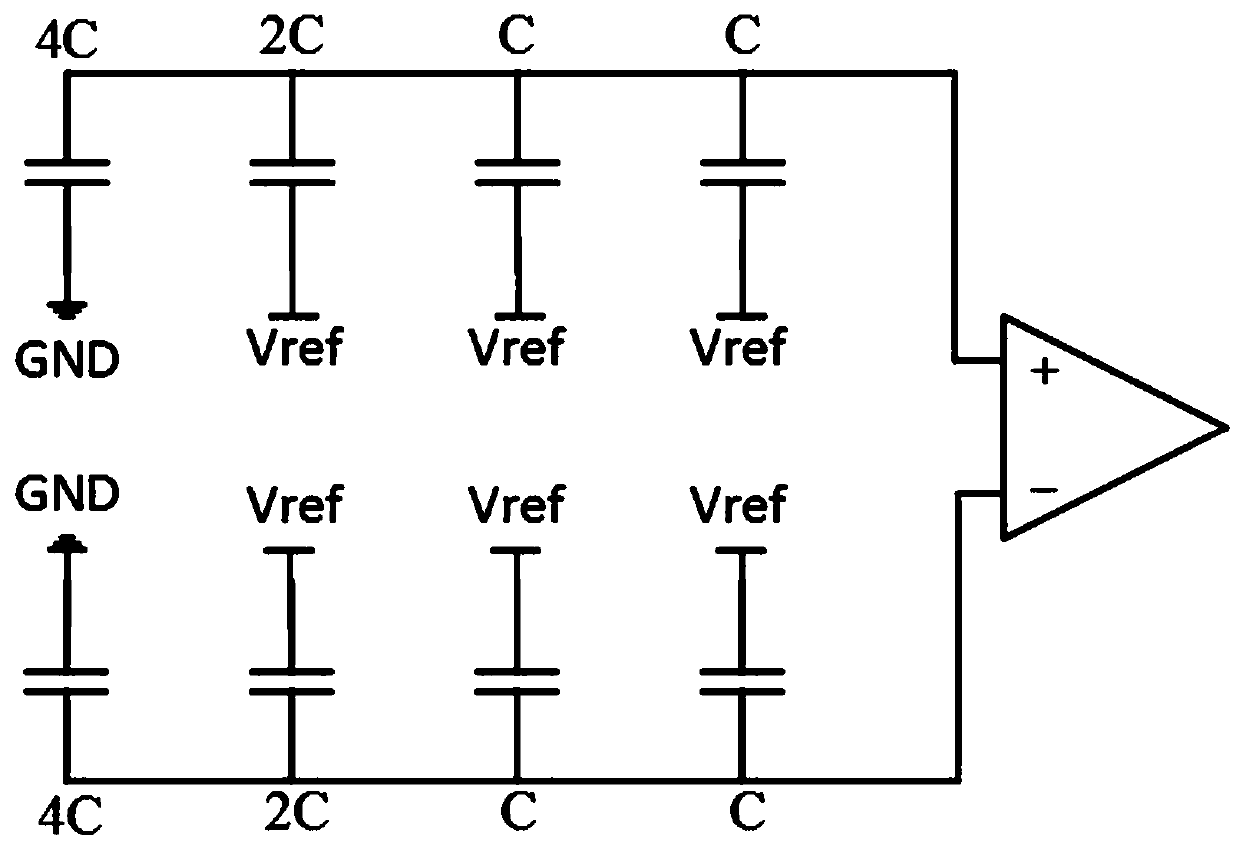

[0047] The invention provides a low power consumption capacitive switching algorithm applied to SAR ADC, so that the power consumption of the capacitive DAC in the conversion process is as small as possible. The working process of the proposed low-power switching algorithm will be further described below in conjunction with the capacitor array.

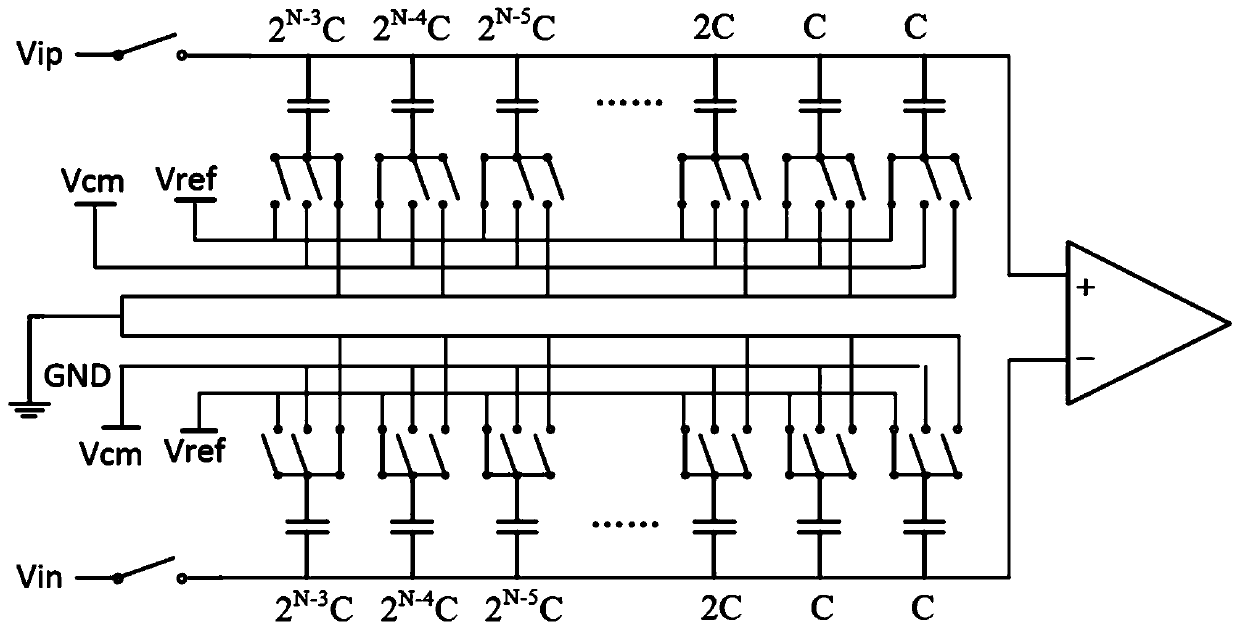

[0048] Such as figure 1 As shown, it is a capacitor array diagram of an N bit SAR ADC used in the switching algorithm proposed by the present invention, and the DAC capacitor array used is a common common binary capacitor array. From figure 1 It can be seen from the figure that for an N-bit SARADC, the entire capacitor array is divided into two positive and negative capacitor arrays with equal positive and negative ends, and each capacitor array includes N-2 capacitors C that conform to the binary relationship i and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More