Patents

Literature

37results about How to "Capacitor area is small" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

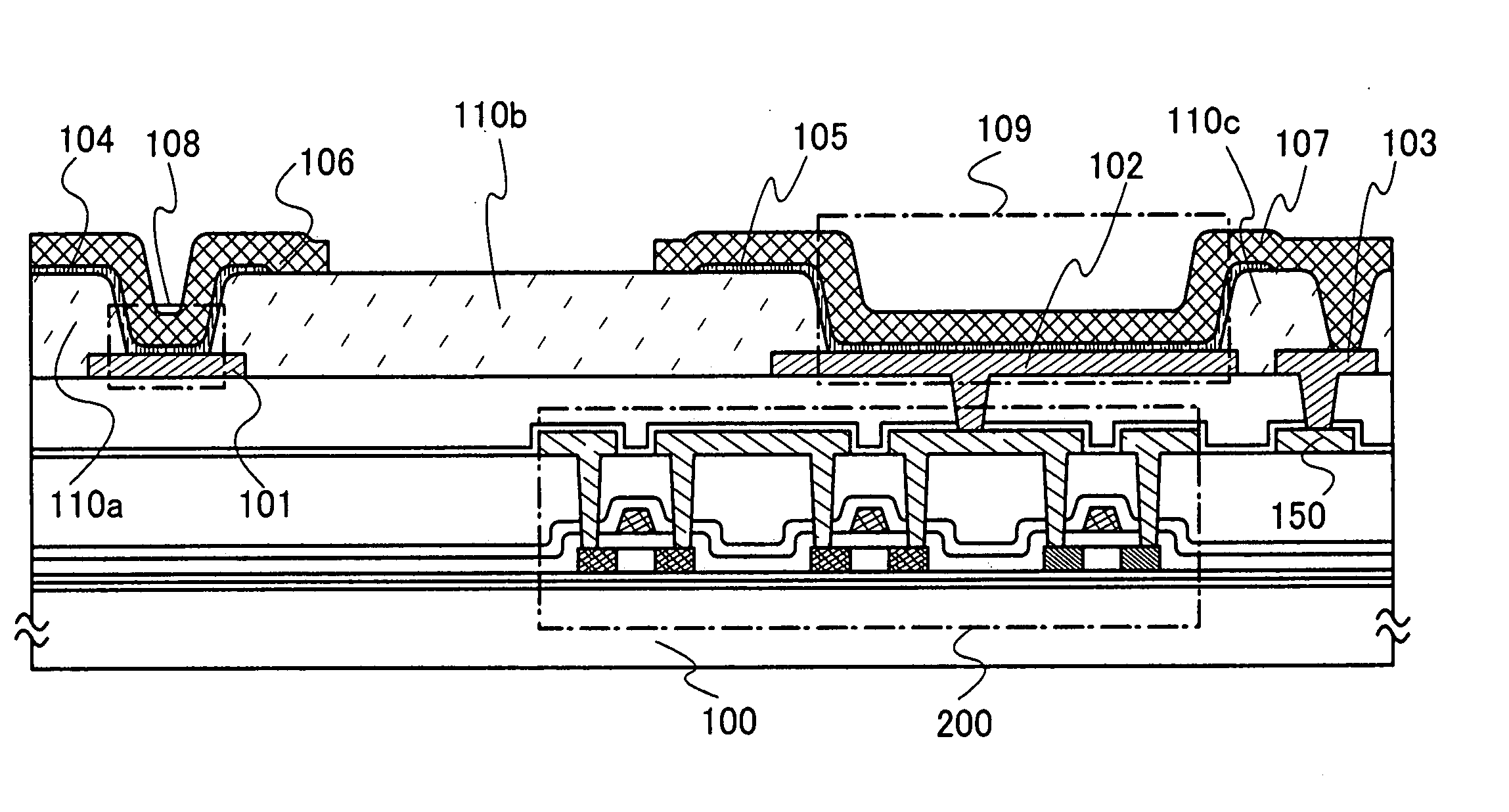

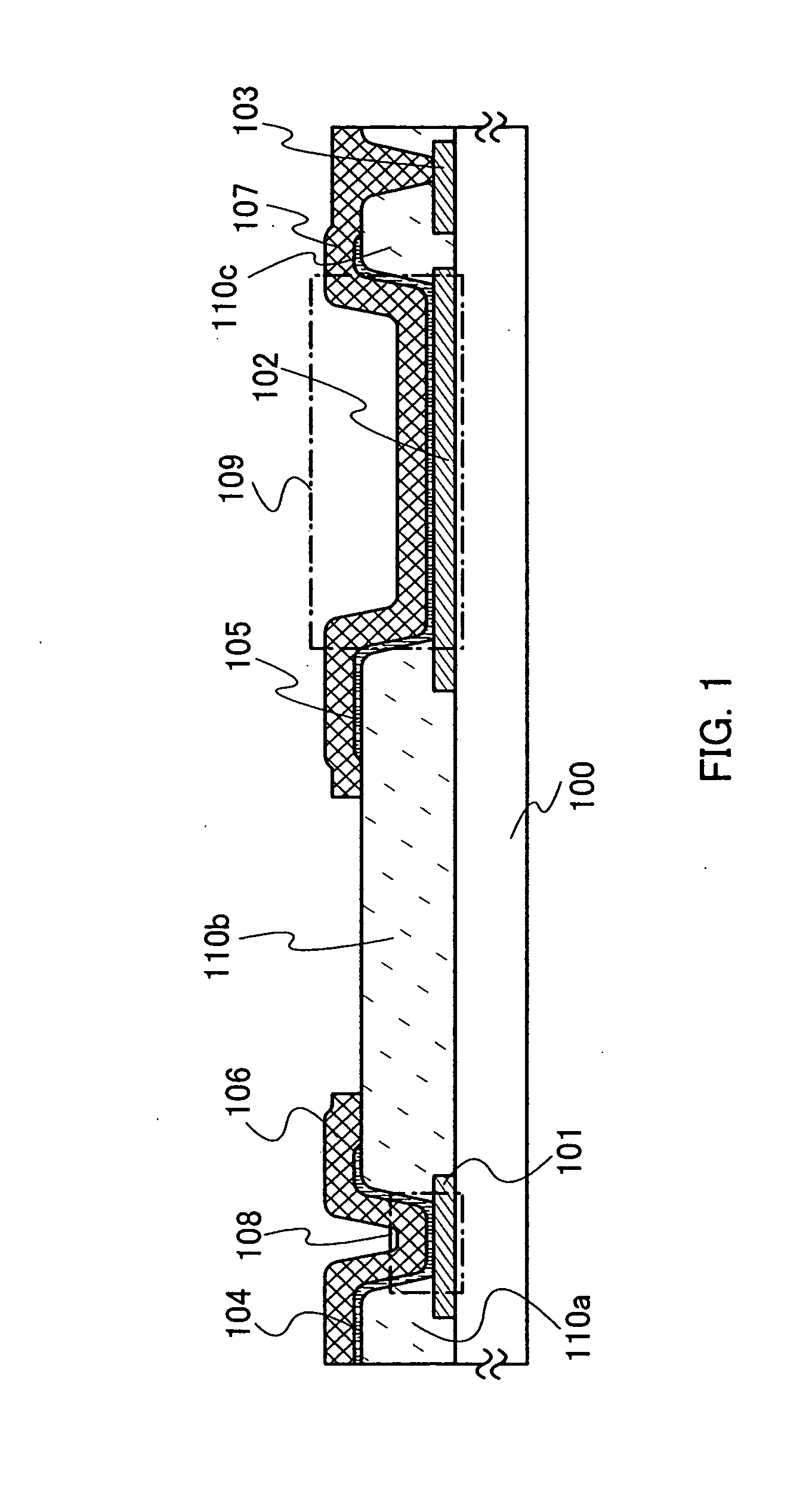

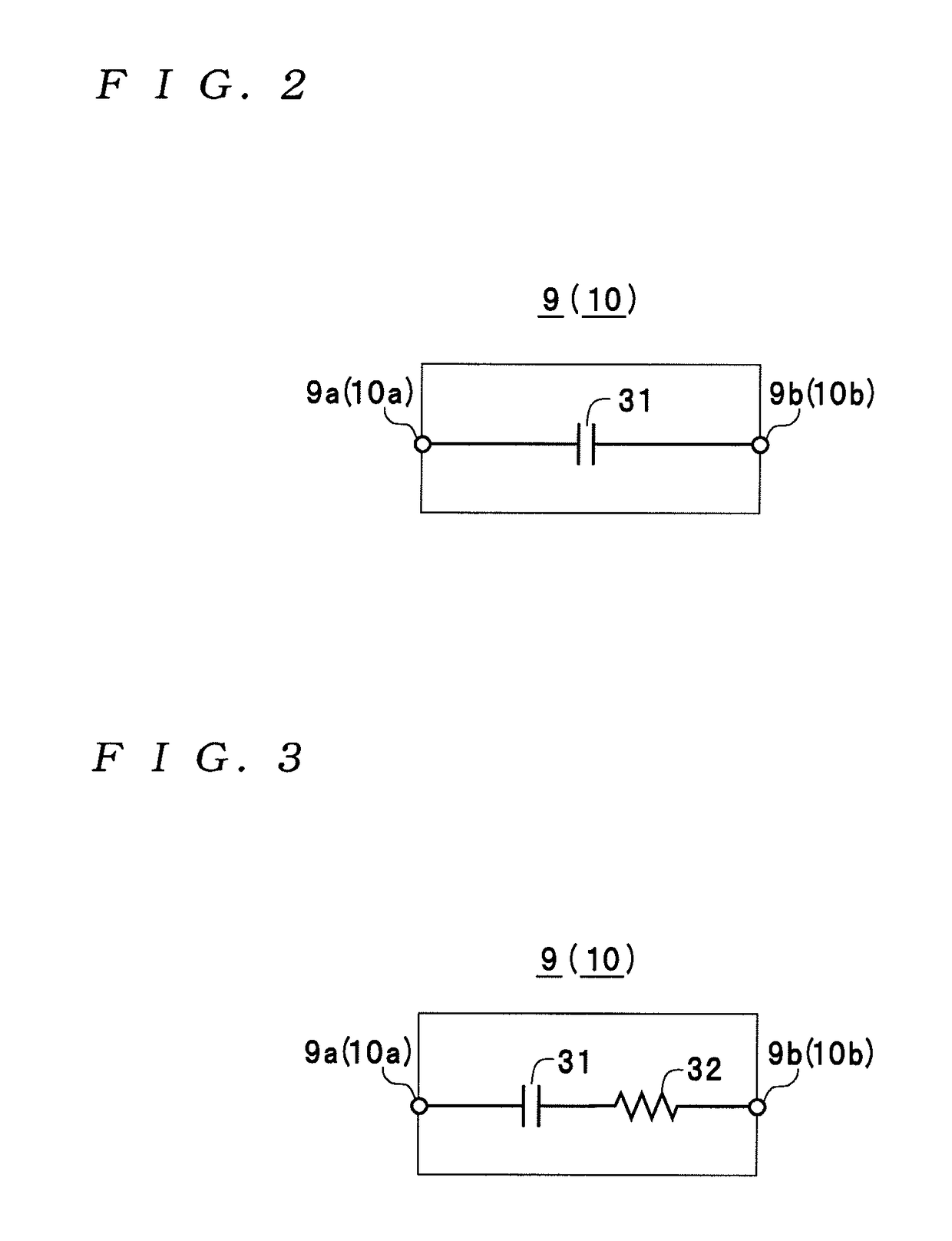

Semiconductor device and manufacturing method thereof

InactiveUS20060267141A1Effective capacityCapacitor area is smallSolid-state devicesSemiconductor/solid-state device manufacturingDielectricOrganic memory

An object of the invention is to reduce an area occupied by a capacitor in a circuit in a semiconductor device, and to downsize a semiconductor device on which the capacitor and an organic memory are mounted. The organic memory and the capacitor, included in a peripheral circuit, in which the same material as the layer containing the organic compound used for the organic memory is used as a dielectric, are used. The peripheral circuit here means a circuit having at least a capacitor such as a resonance circuit, a power supply circuit, a boosting circuit, a DA converter, or a protective circuit. Further, a capacitor in which a semiconductor is used as a dielectric may be provided over the same substrate as well as the capacitor in which the same material as the layer containing the organic compound is used as a dielectric. In this case, it is desirable that the capacitor in which the same material as the layer containing the organic compound is used as a dielectric and the capacitor in which the semiconductor is used as a dielectric are connected to each other in parallel.

Owner:SEMICON ENERGY LAB CO LTD

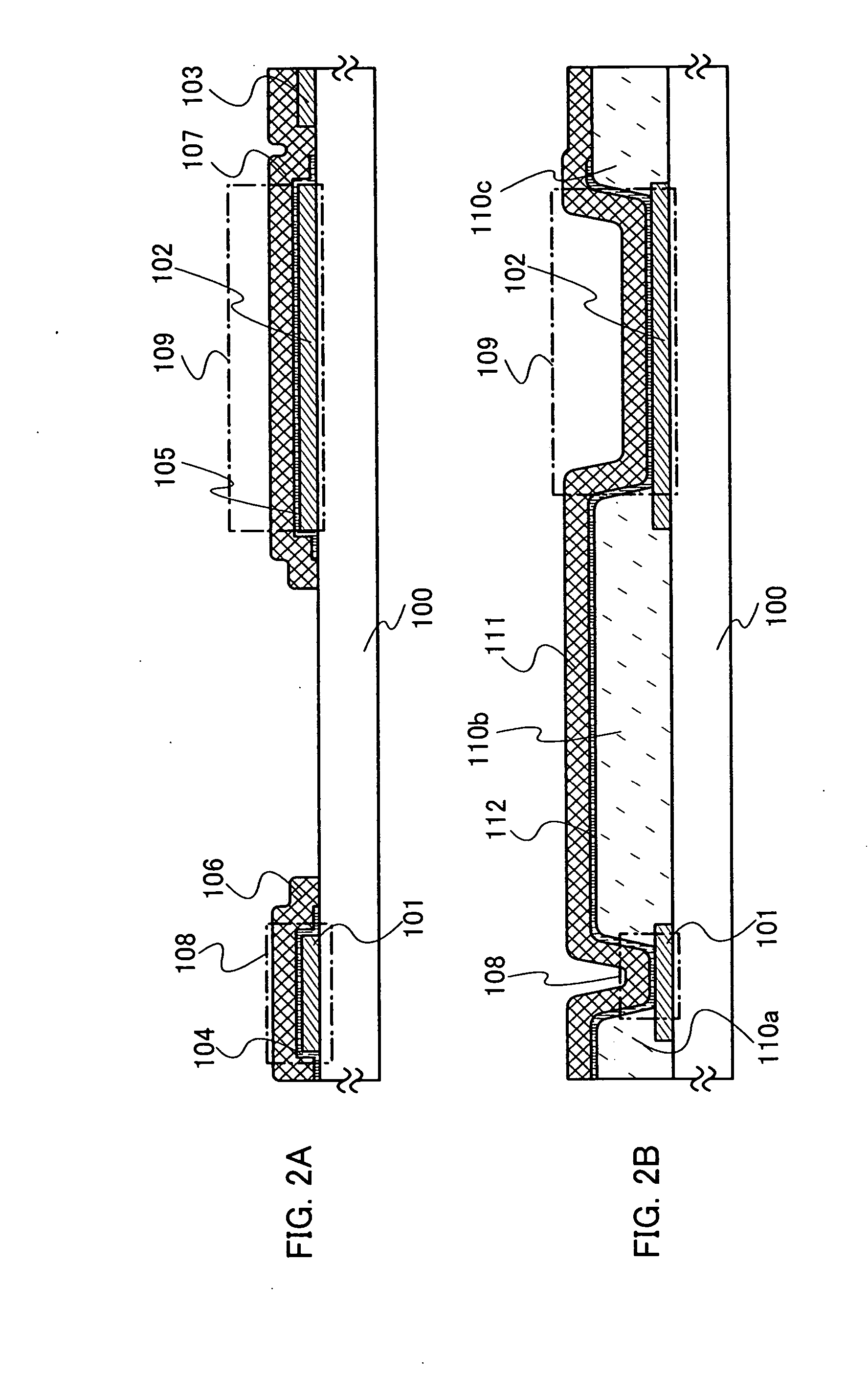

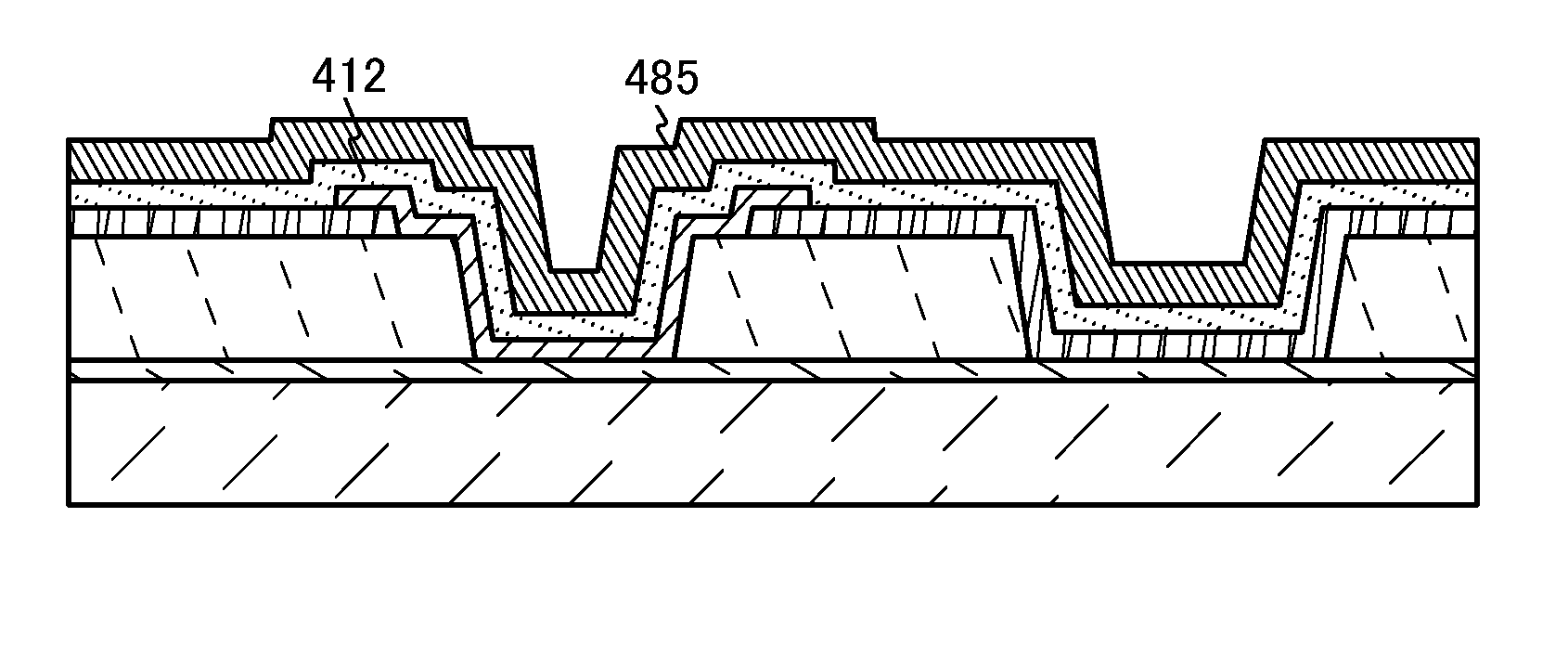

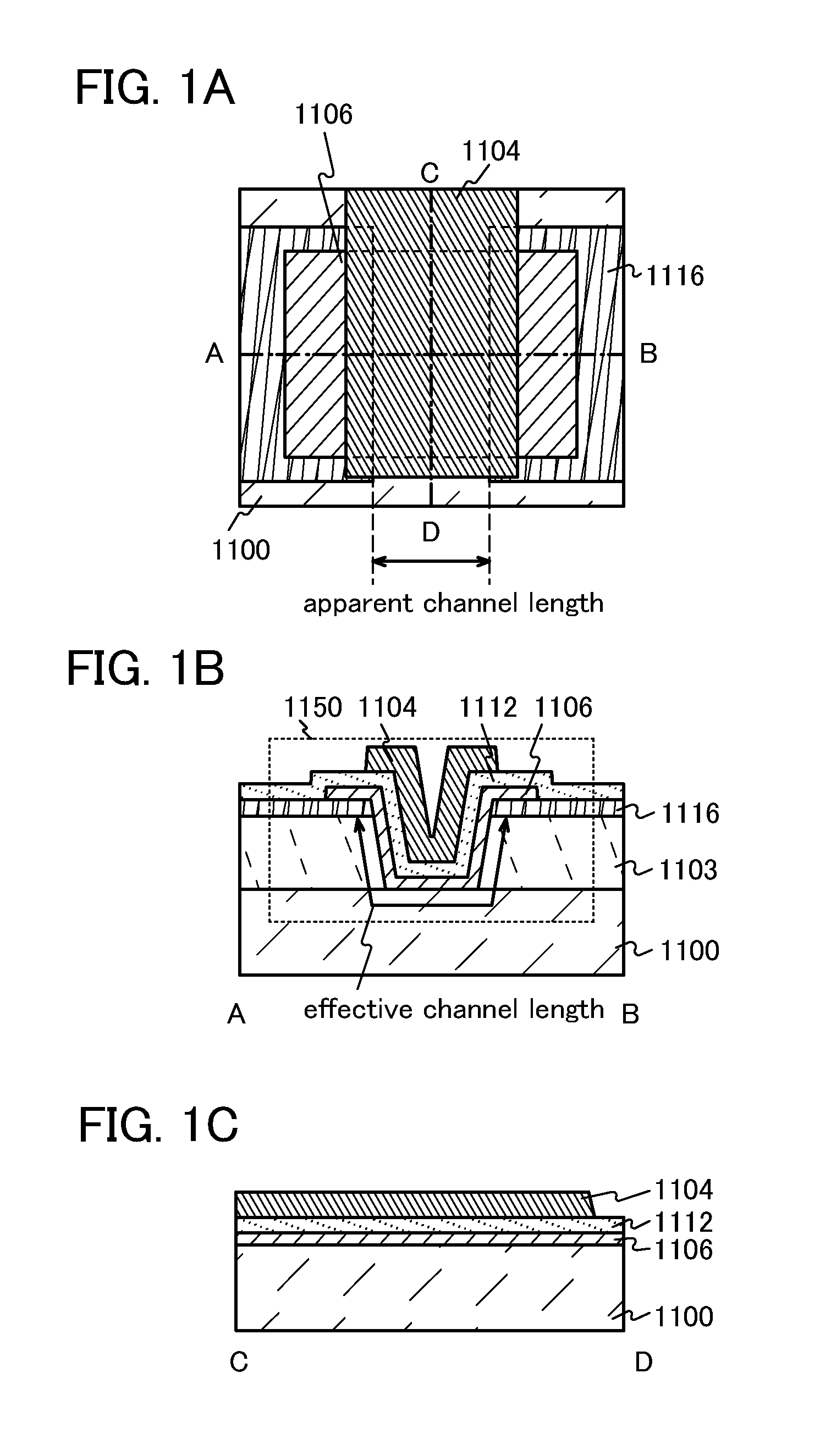

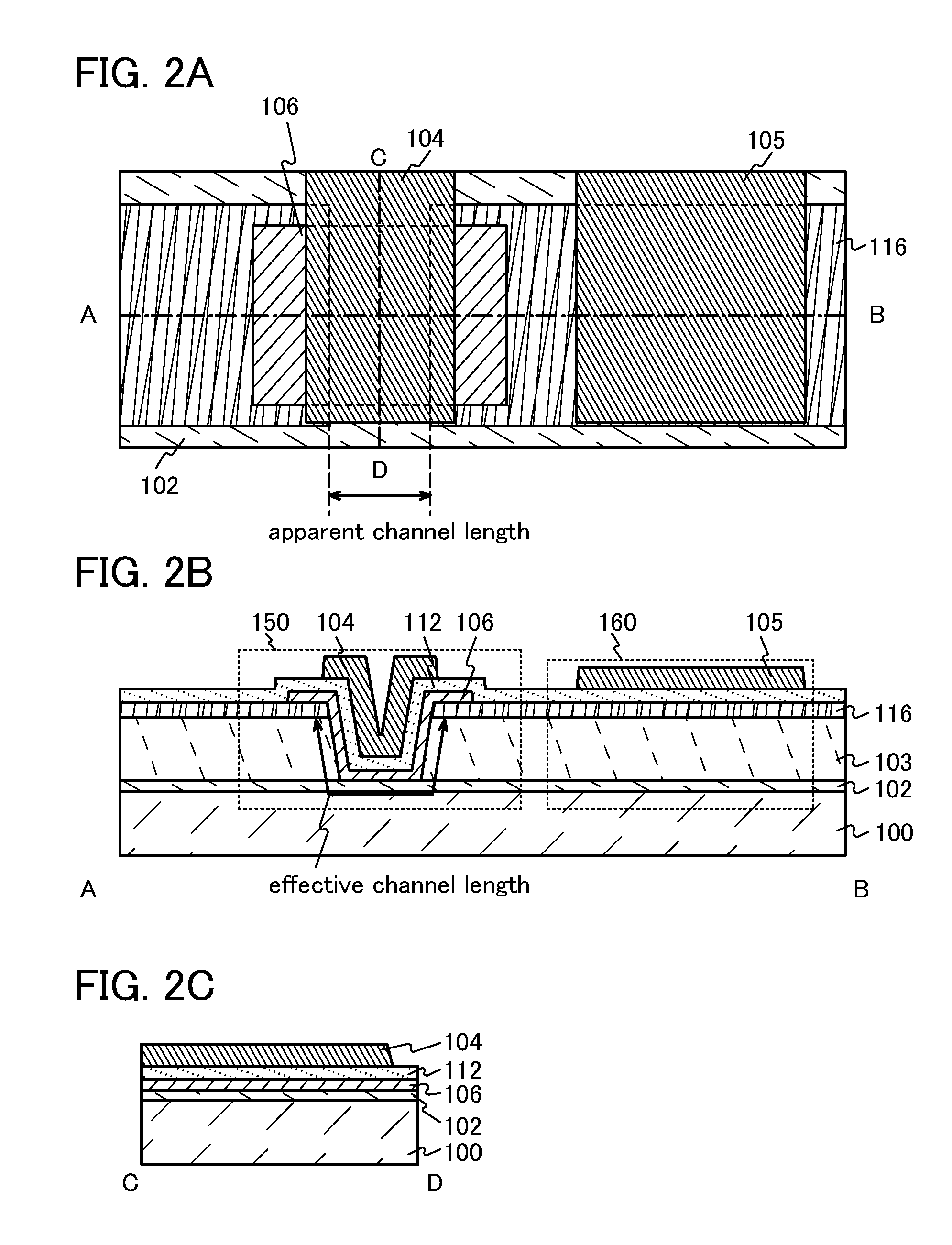

Semiconductor memory device and method for manufacturing the same

InactiveUS20120223310A1Total current dropReduce oxygen vacancyTransistorSolid-state devicesEngineeringCapacitor

A semiconductor memory device includes a transistor and a capacitor. The transistor includes: an insulating film in which a groove portion is provided; a pair of electrodes separated so that the groove portion is sandwiched therebetween; an oxide semiconductor film which is in contact with the pair of electrodes and side surfaces and a bottom surface of the groove portion and has a thickness value smaller than a depth value of the groove portion; a gate insulating film covering the oxide semiconductor film; and a gate electrode provided to overlap with the oxide semiconductor film with the gate insulating film positioned therebetween.

Owner:SEMICON ENERGY LAB CO LTD

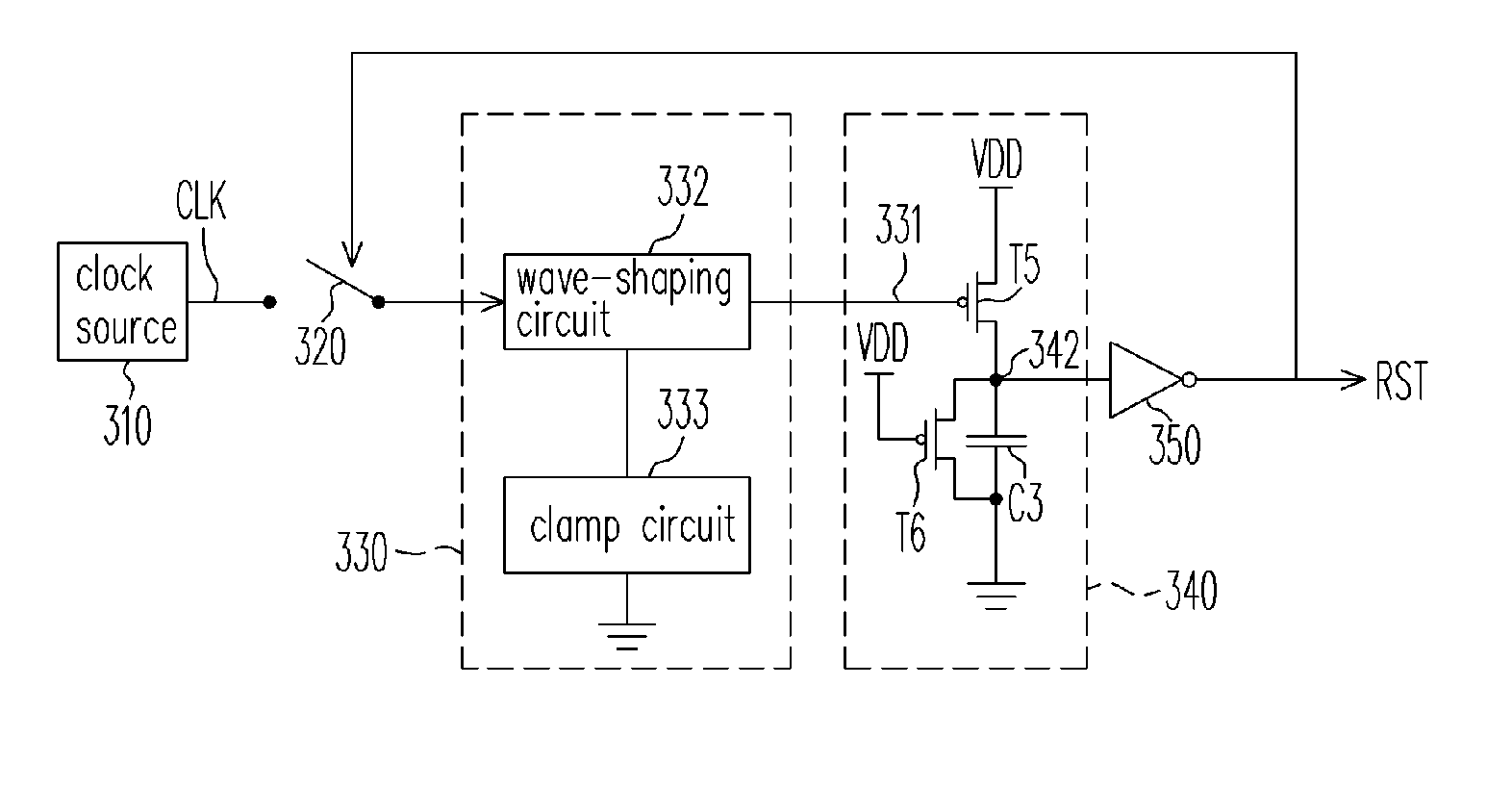

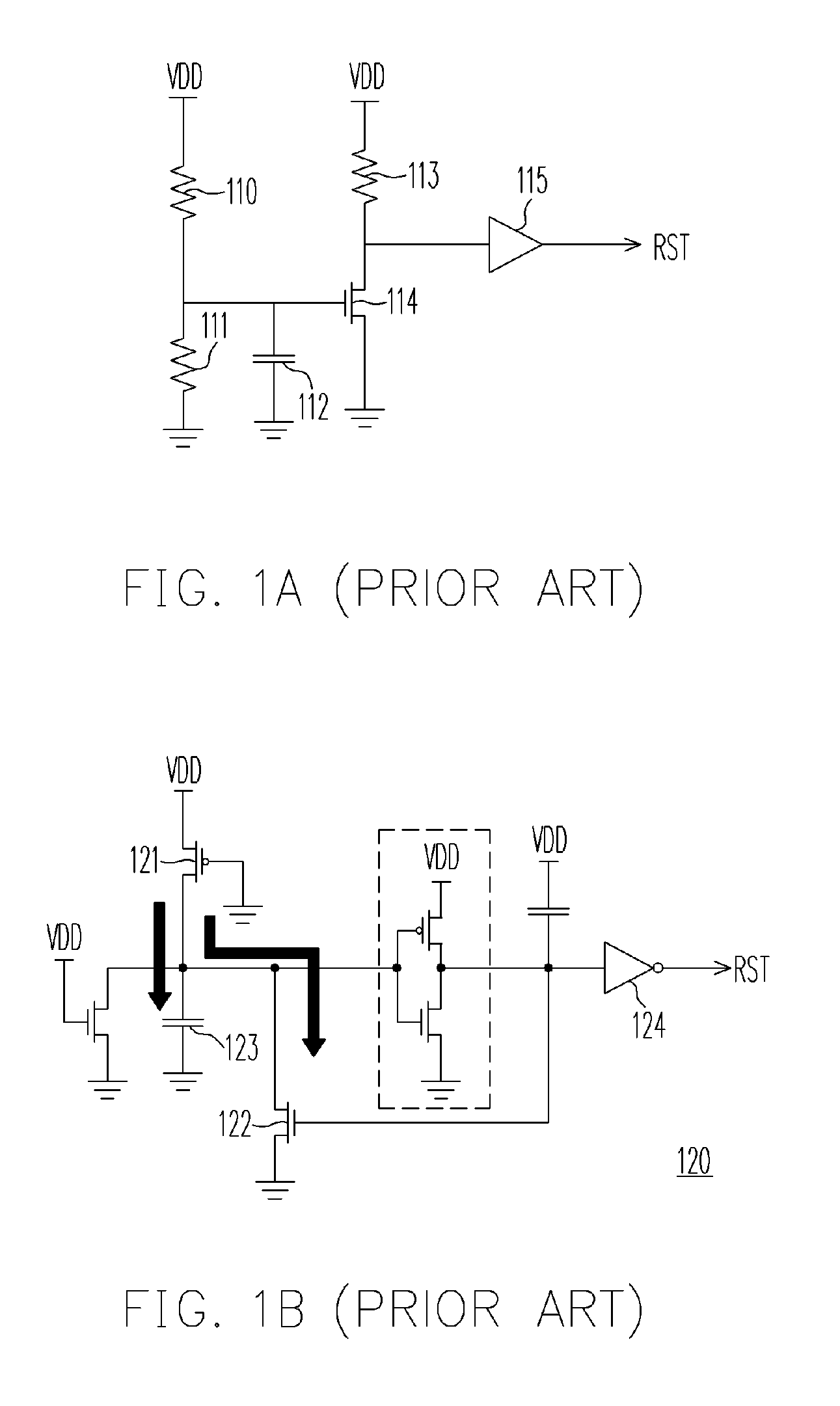

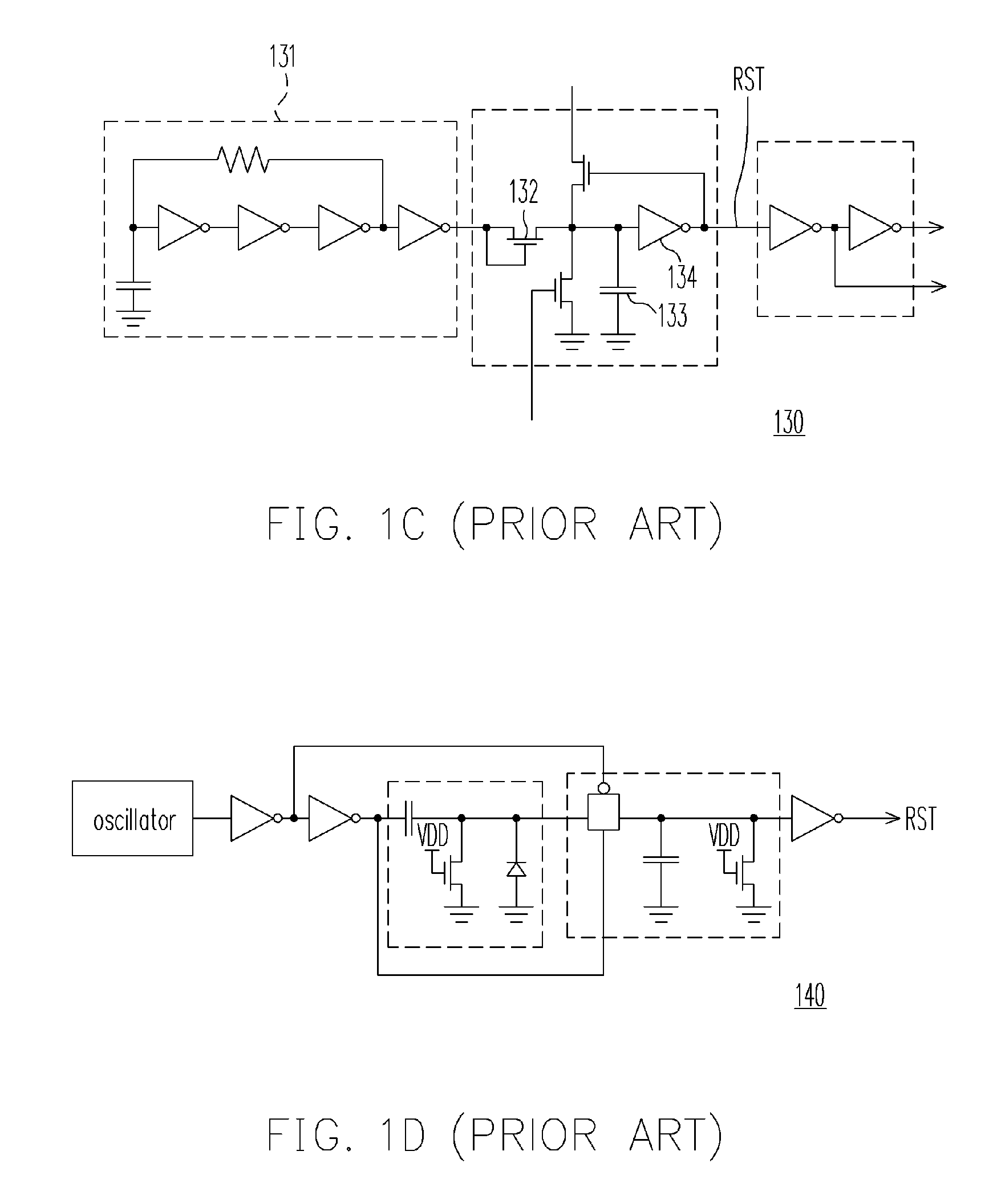

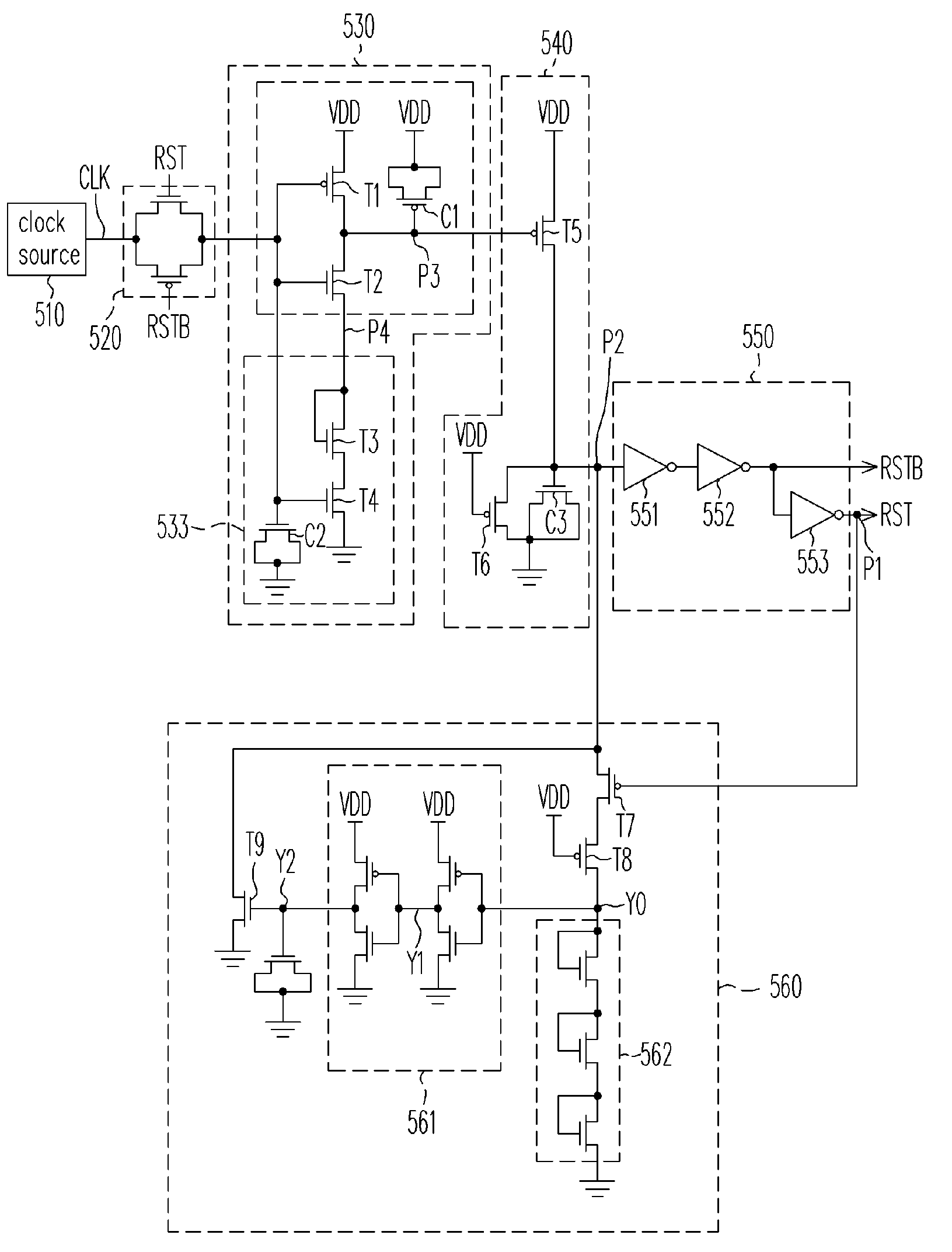

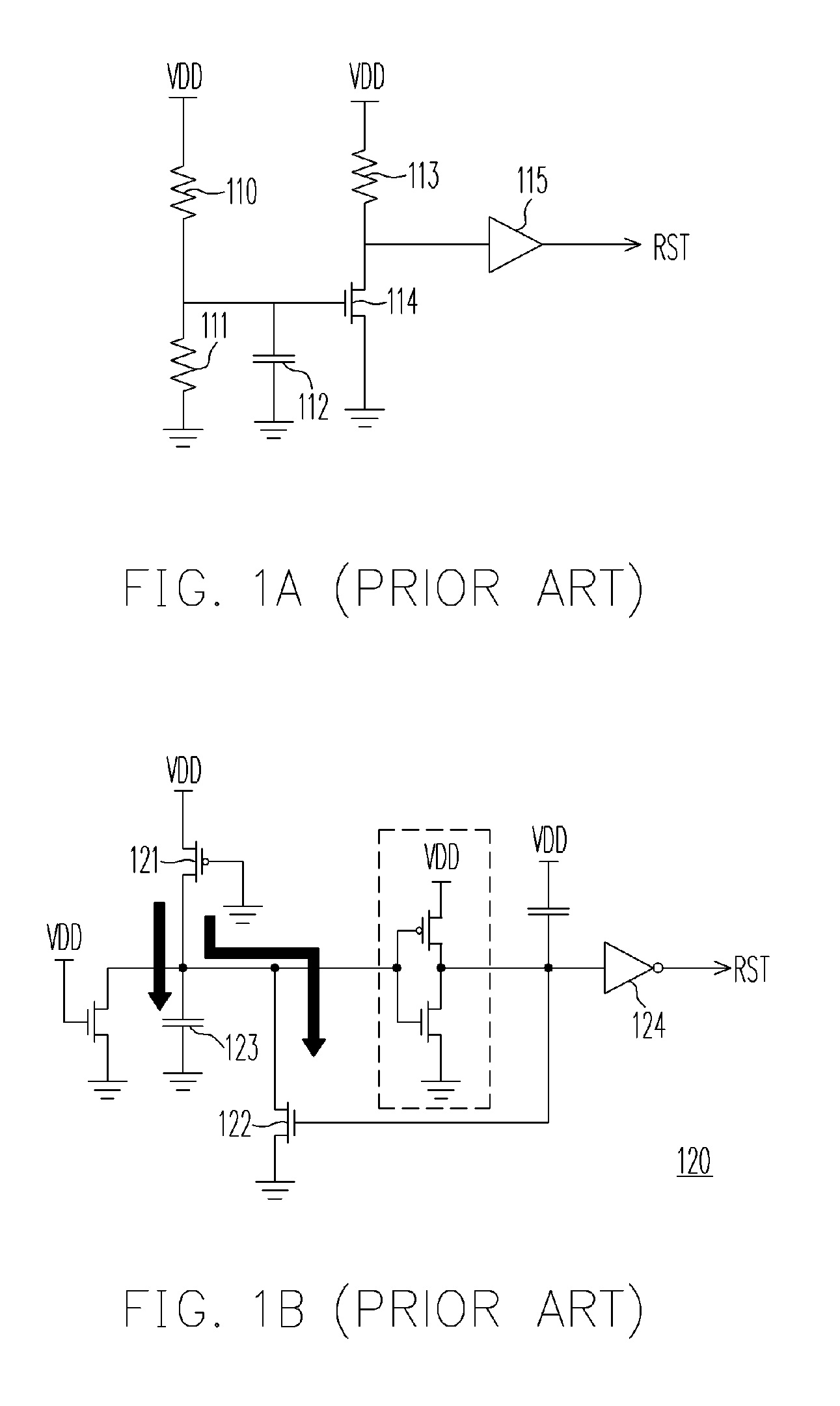

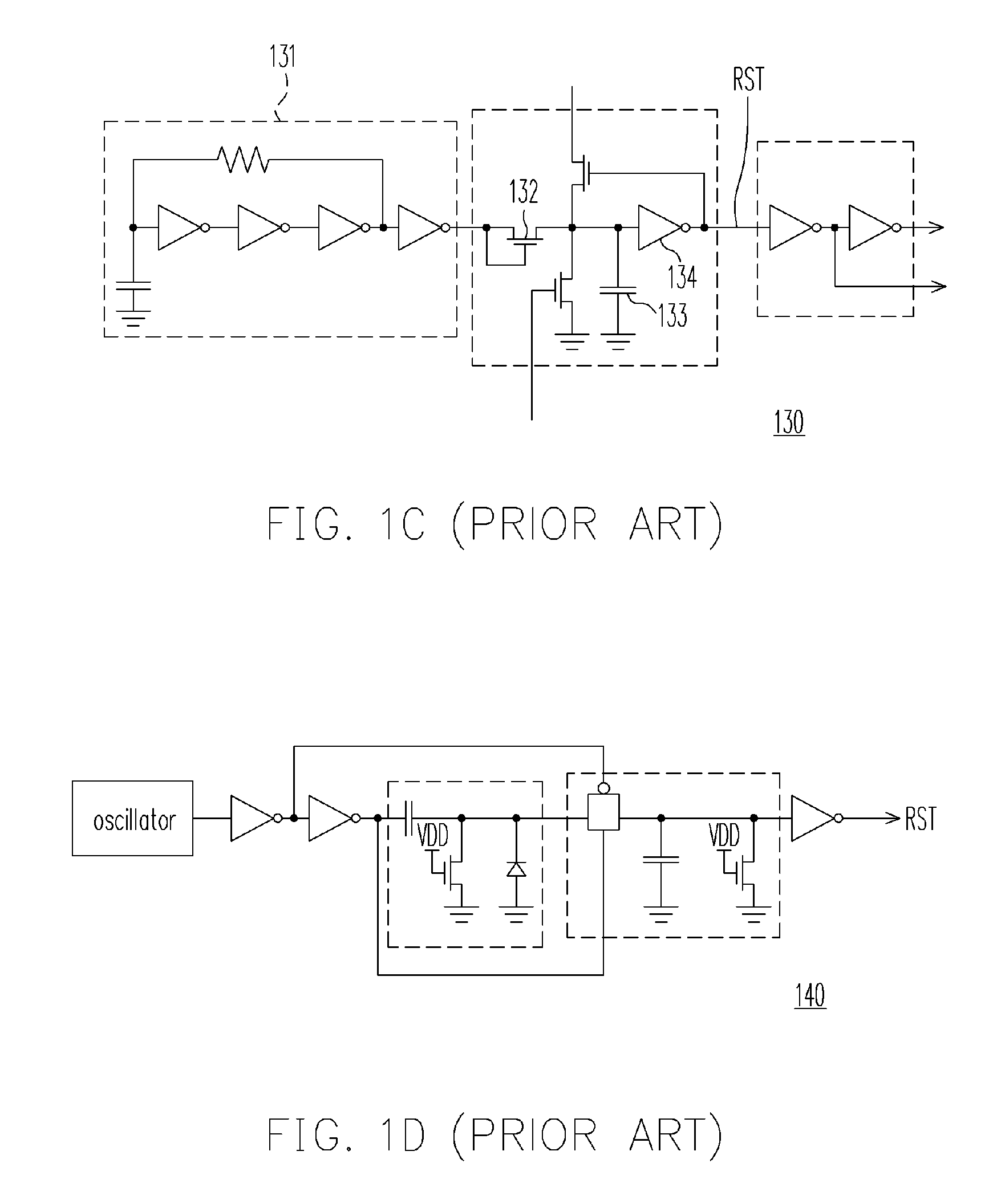

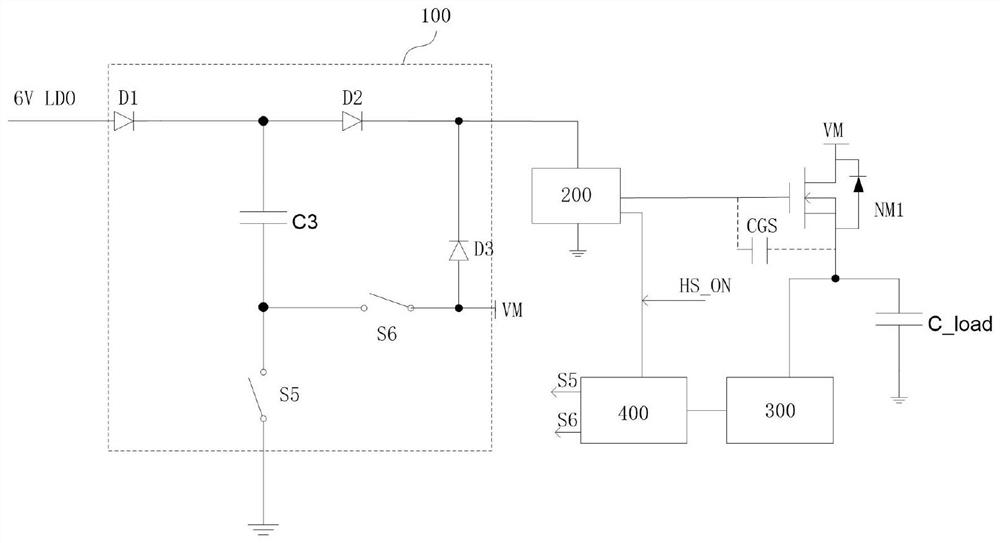

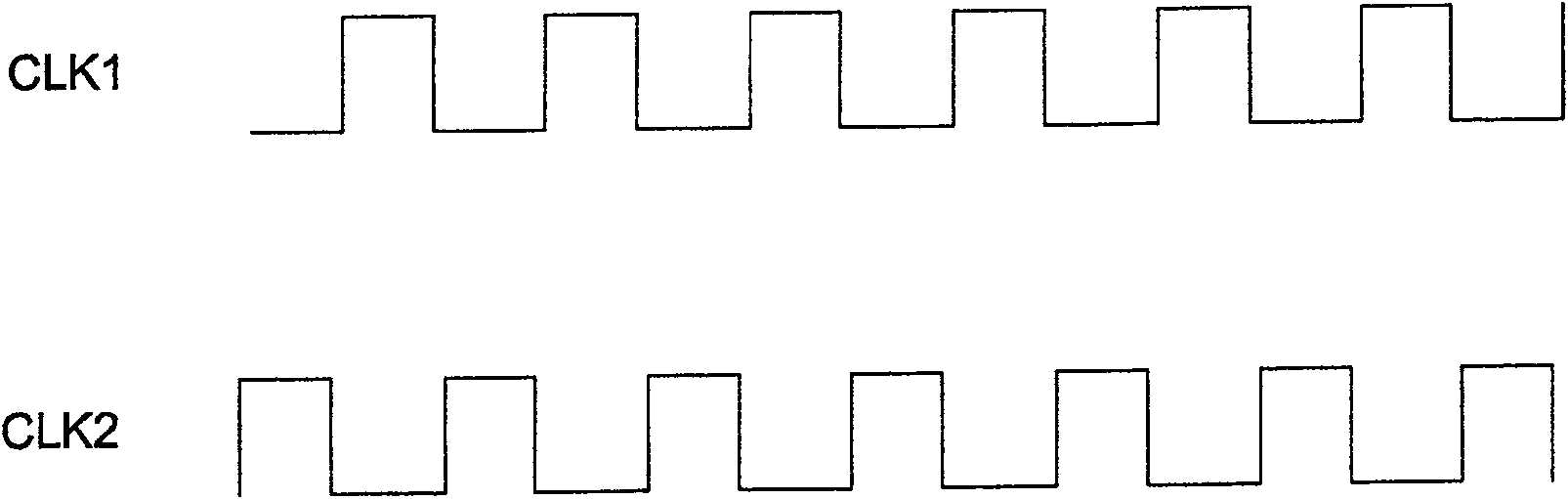

Power-on reset circuit

ActiveUS20060109037A1Reduce areaReduce capacitancePulse automatic controlElectronic switchingPower-on resetCapacitance

A power-on reset circuit is provided. The power-on reset circuit includes an adjusting circuit, a charging / discharging unit and an output circuit. The adjusting circuit receives and adjusts a clock signal so as to output a control signal, wherein a minimum level of the control signal is clamped to be higher than a pre-defined level. The charging / discharging unit having a capacitor apparatus receives the control signal, determines whether to charge / discharge the capacitor apparatus based on the control signal, and outputs a storage voltage of the capacitor apparatus. The output circuit receives the storage voltage and outputs the reset signal. Wherein, the adjusting circuit determines the charging / discharging duty cycle of the charging / discharging unit by adjusting the waveform and the minimum level of the control signal. The output circuit enables / disables the reset signal according to whether the storage voltage reaches the threshold voltage of the output circuit.

Owner:XIAMEN XM PLUS TECH LTD

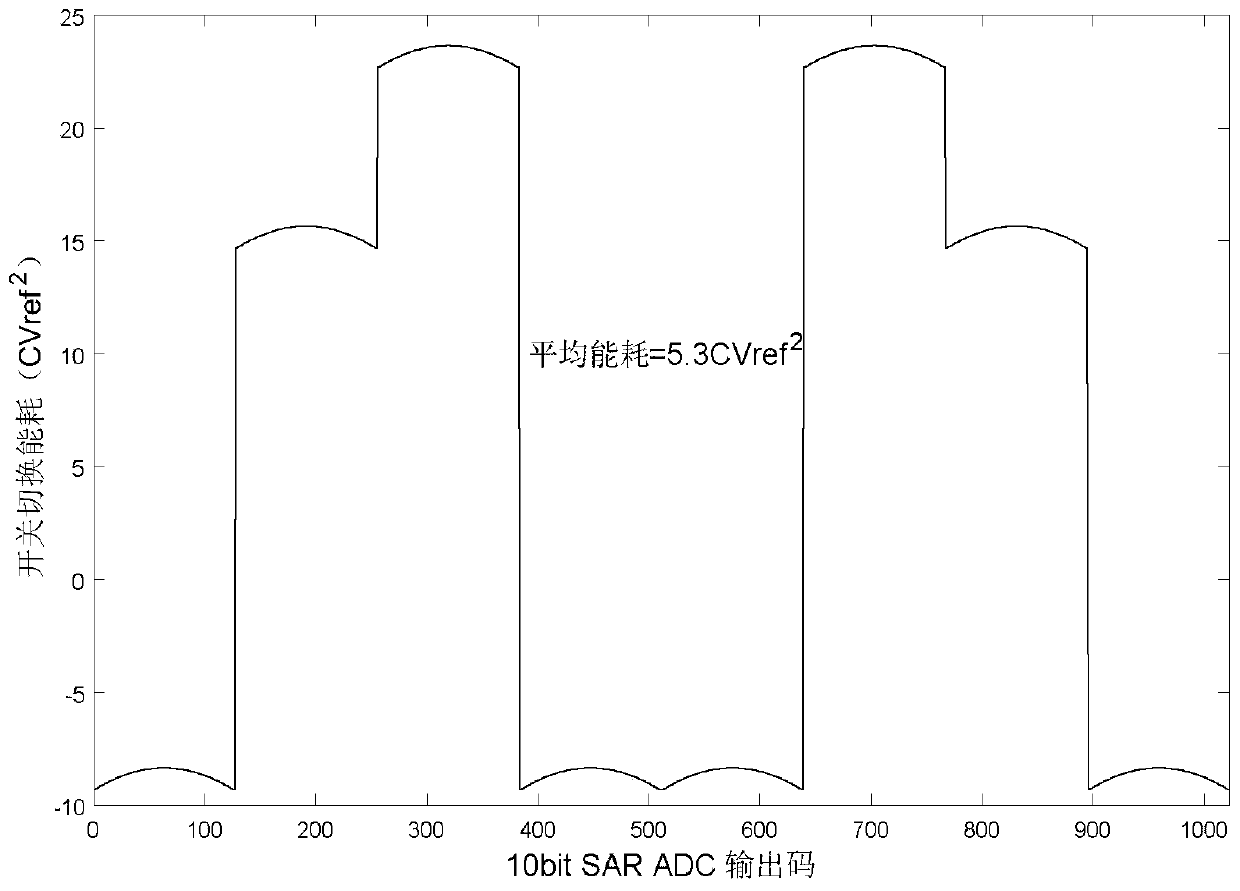

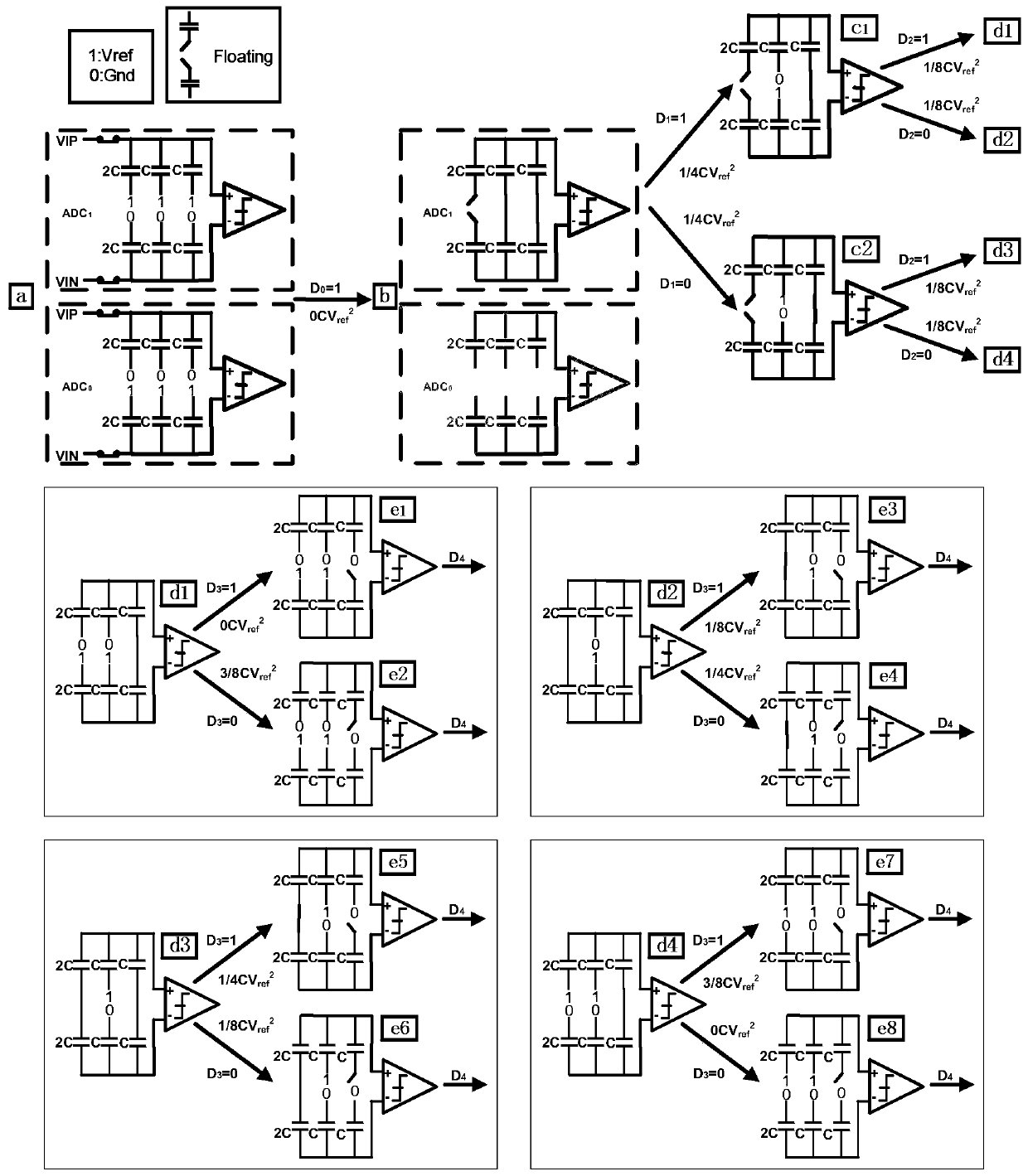

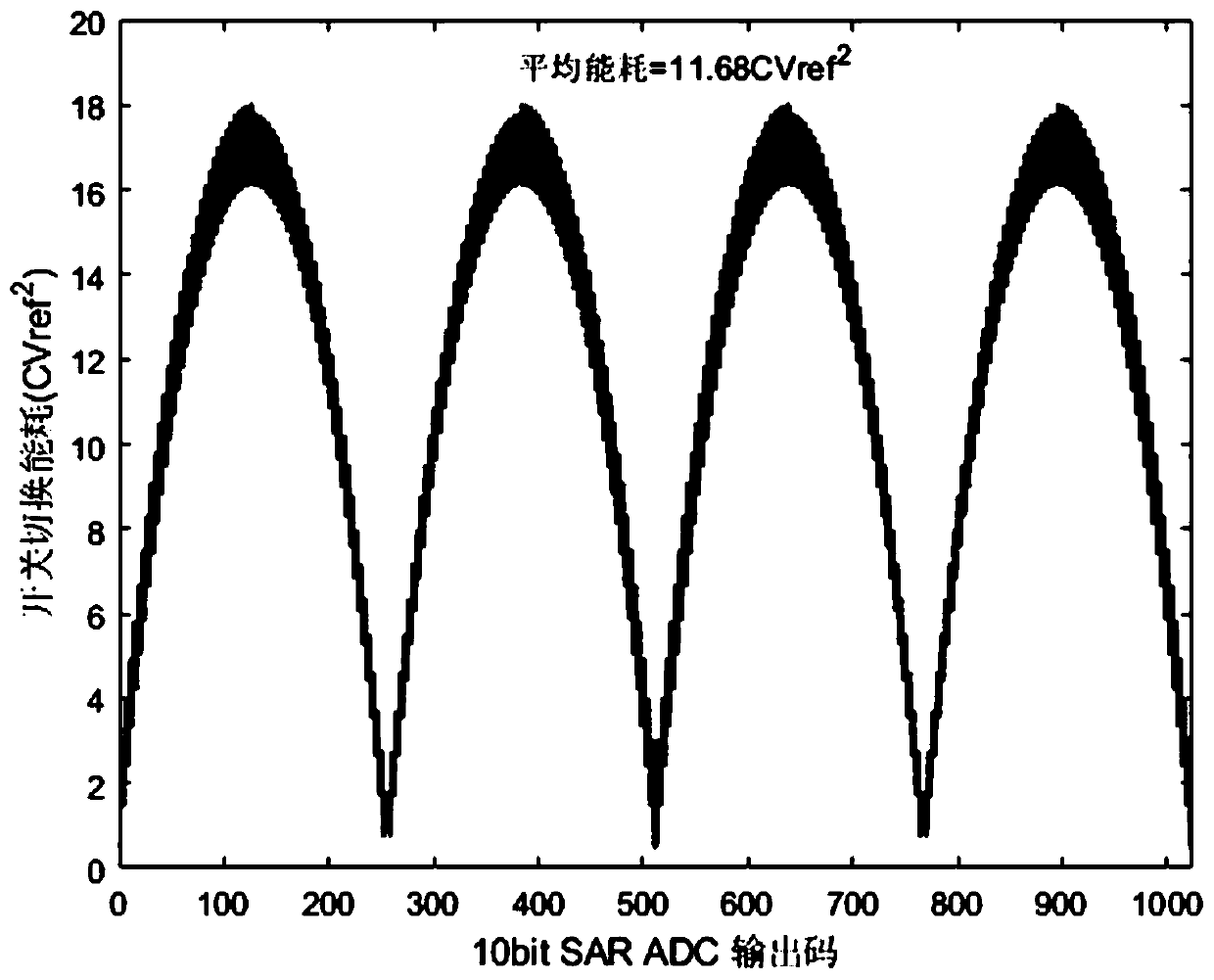

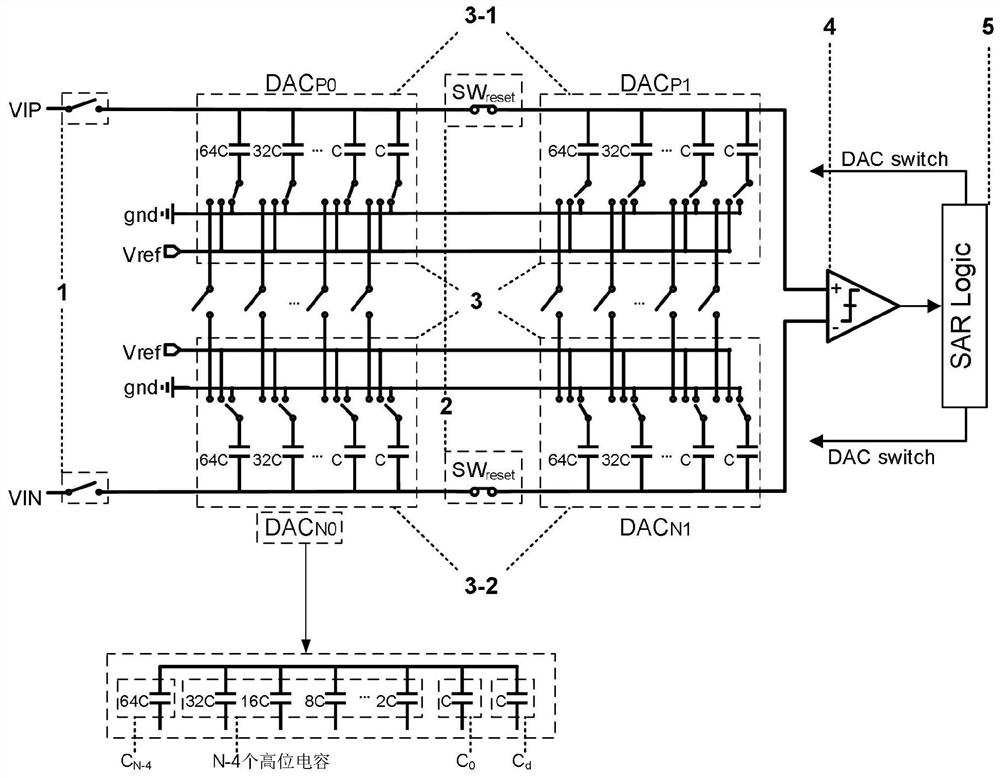

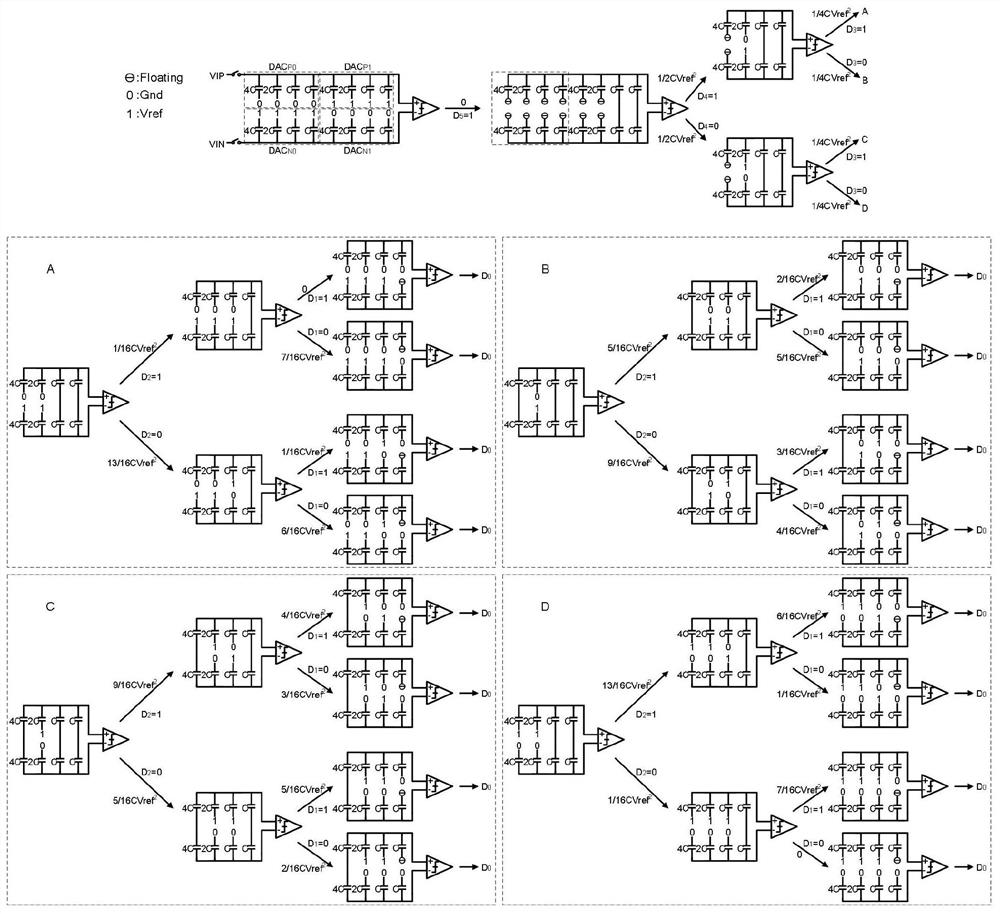

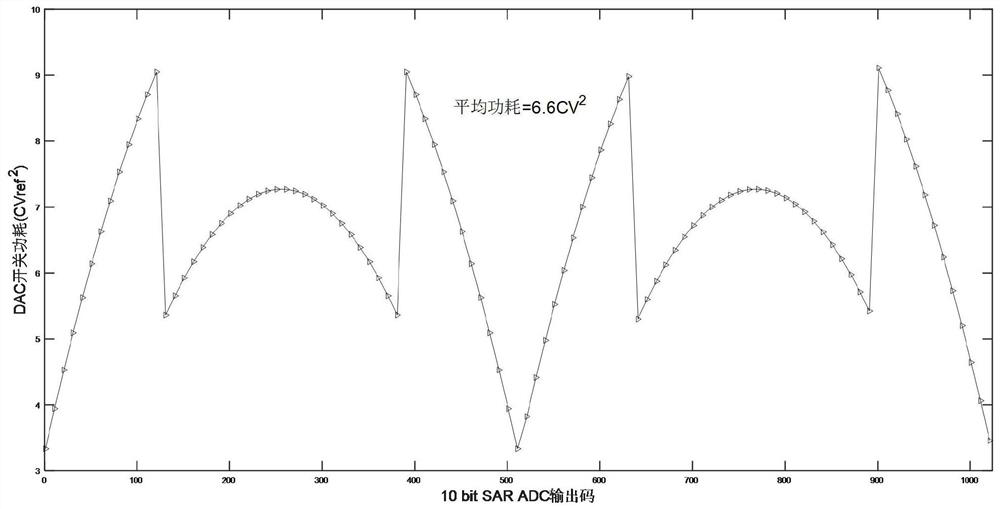

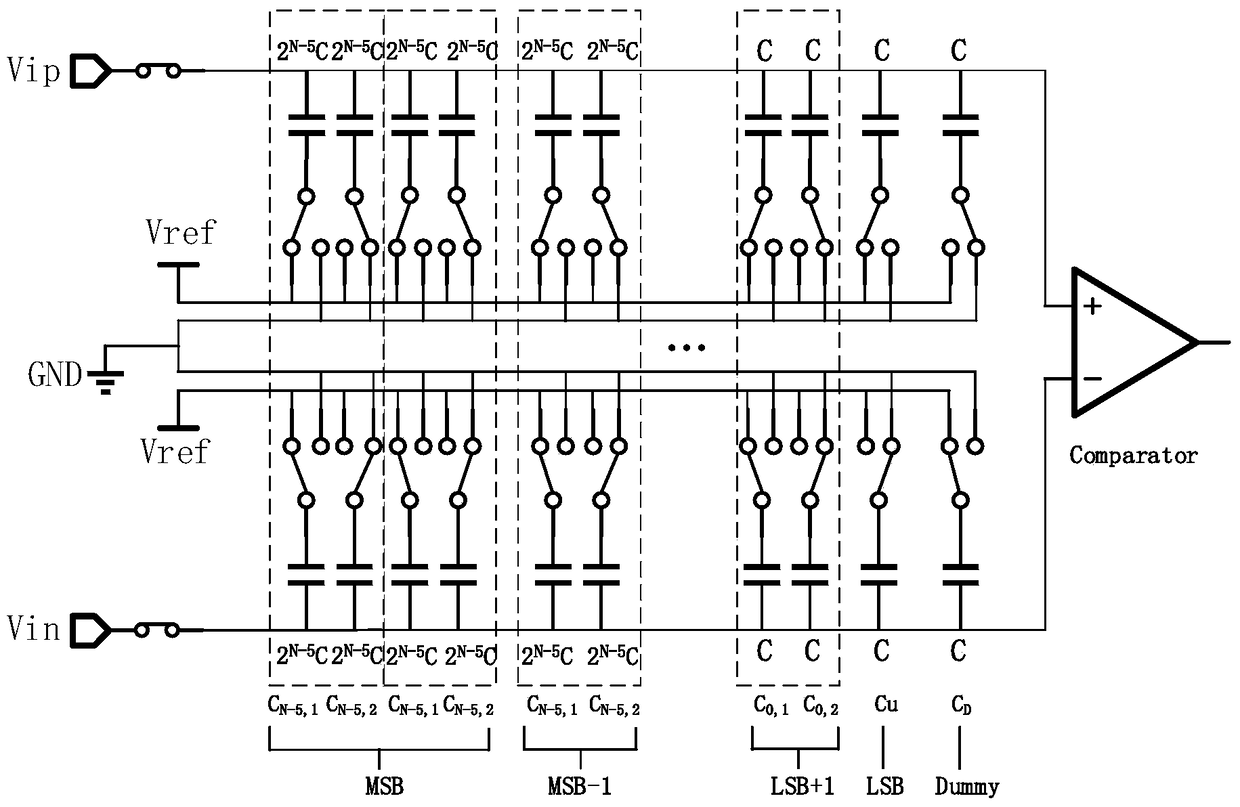

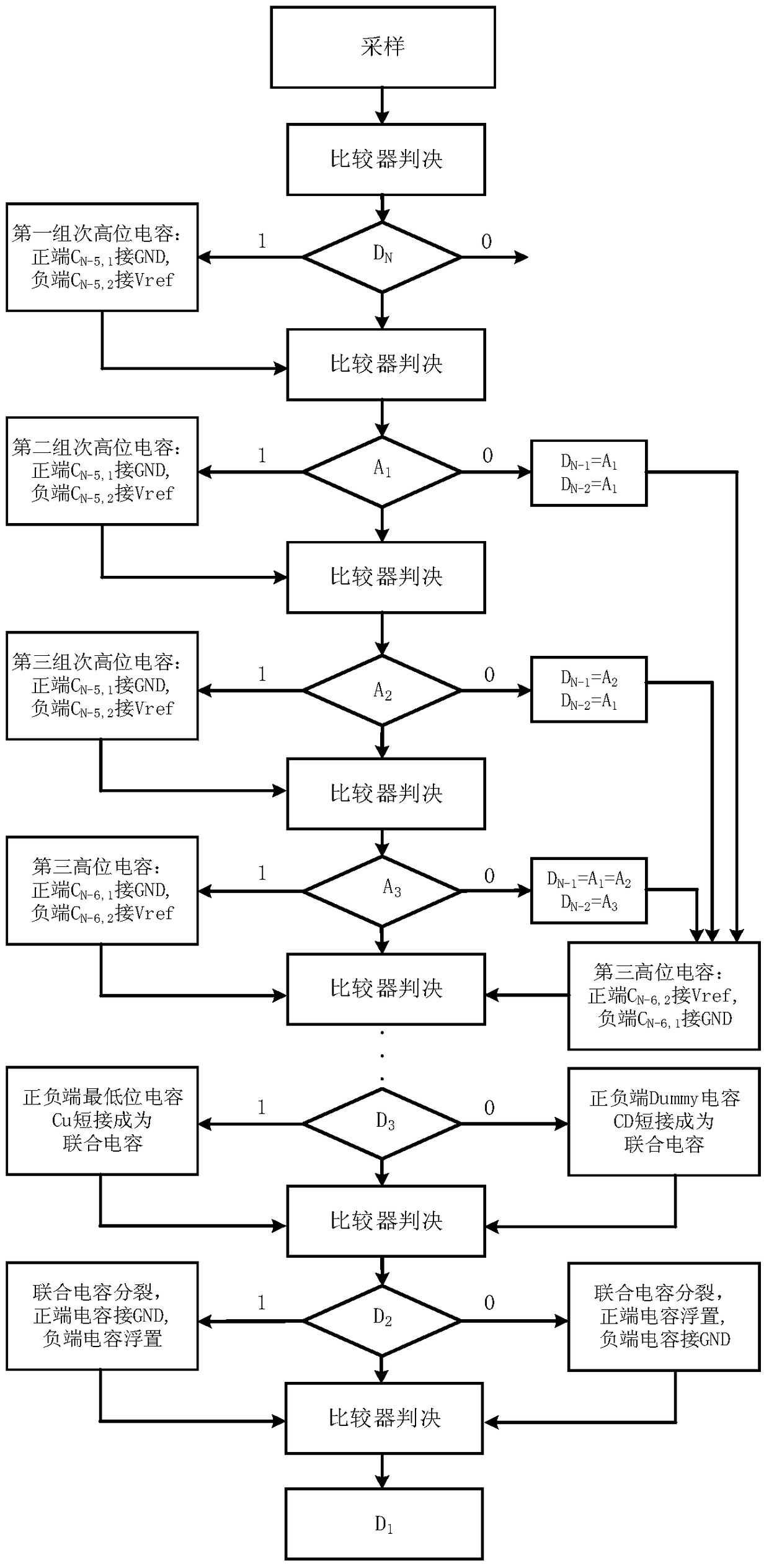

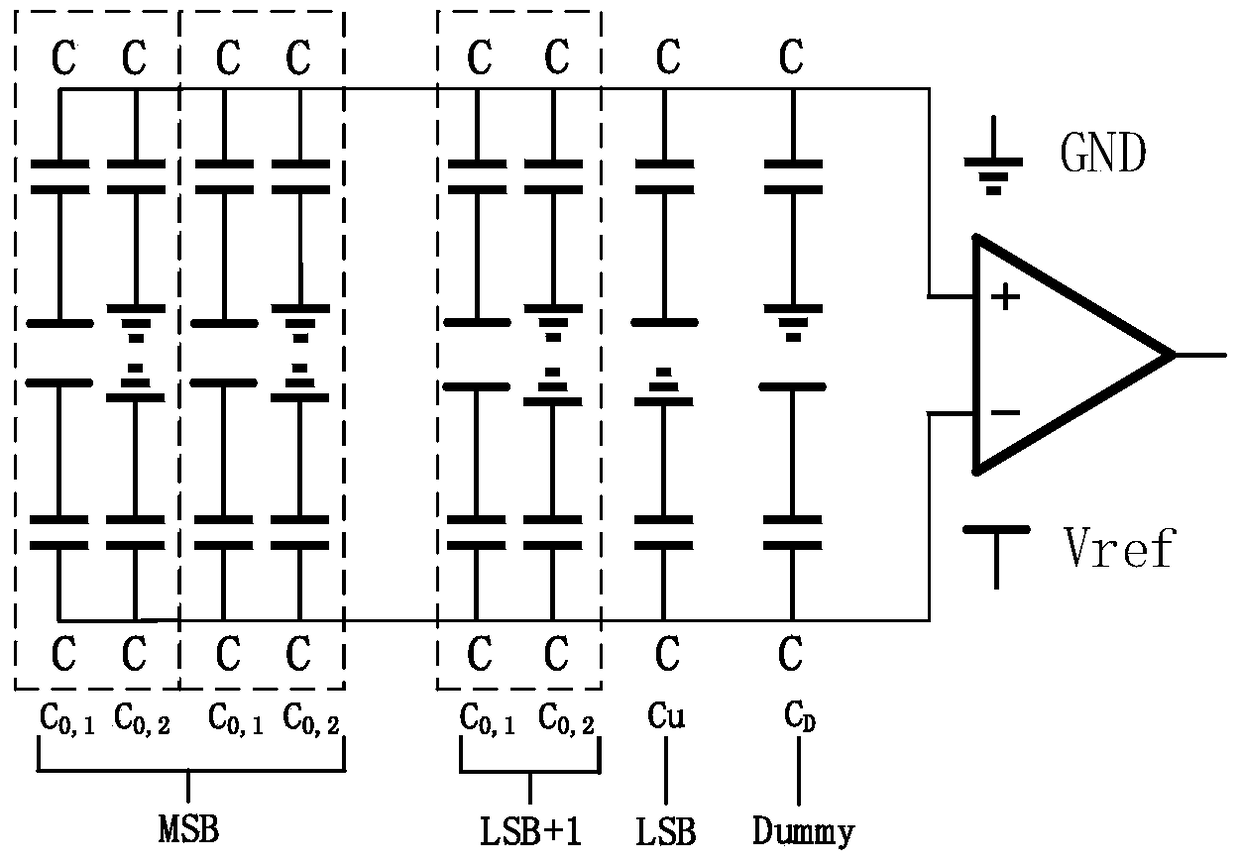

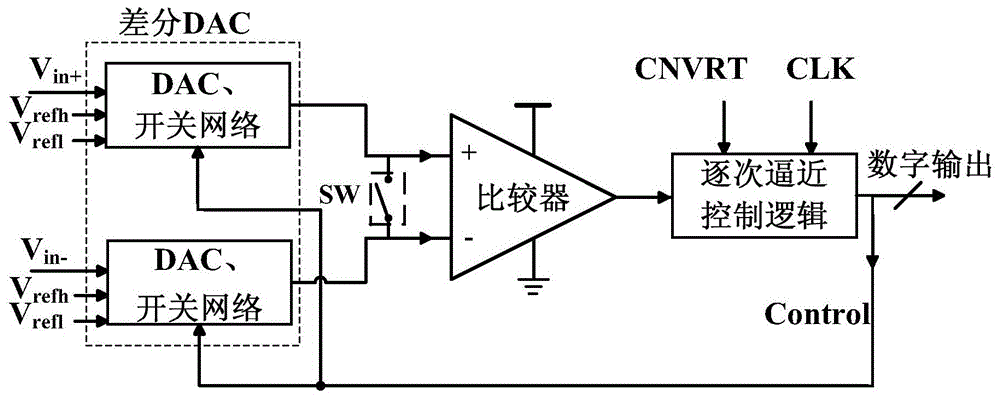

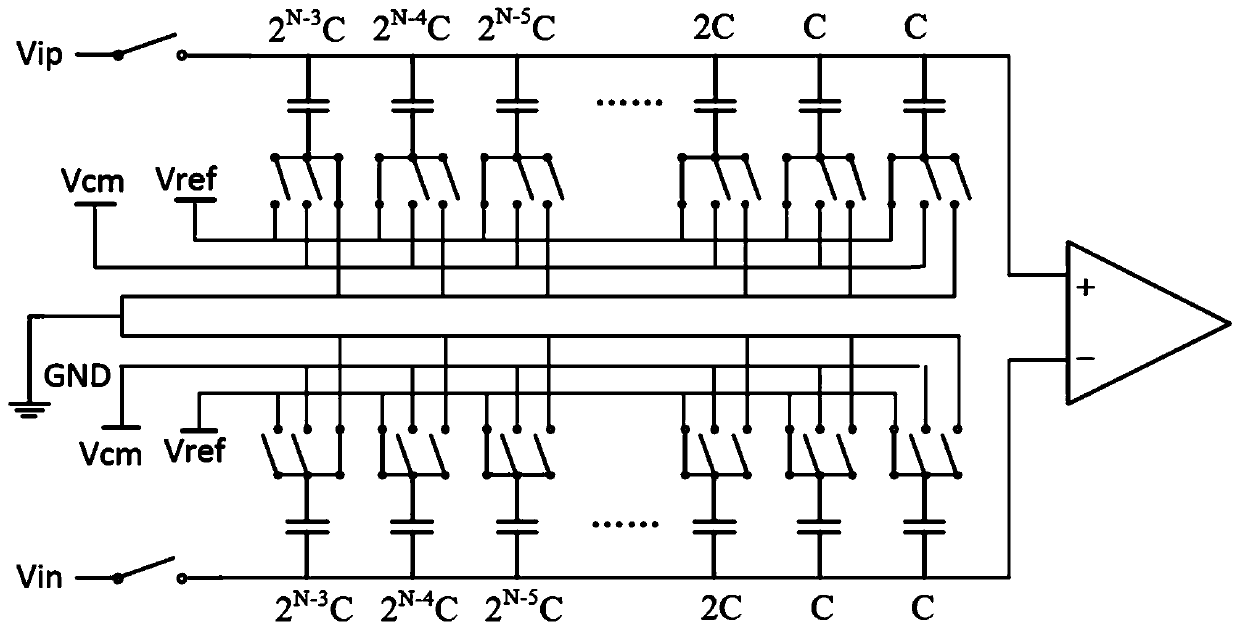

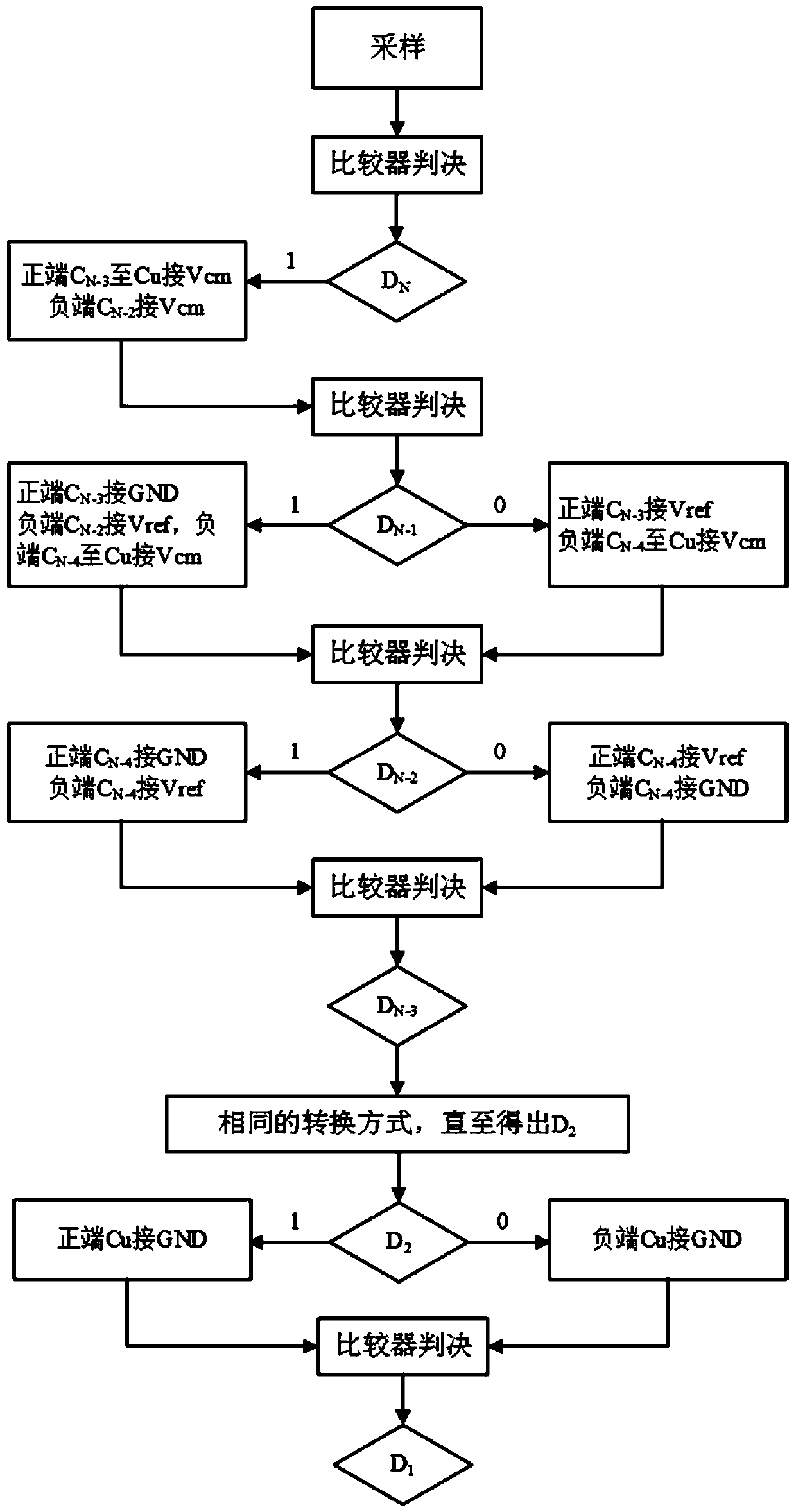

Binary capacitor array applied to near-threshold SARADC and switching method with low power consumption thereof

ActiveCN105553479AImprove performanceMitigate the deterioration of linearityAnalogue/digital conversionElectric signal transmission systemsCapacitanceEngineering

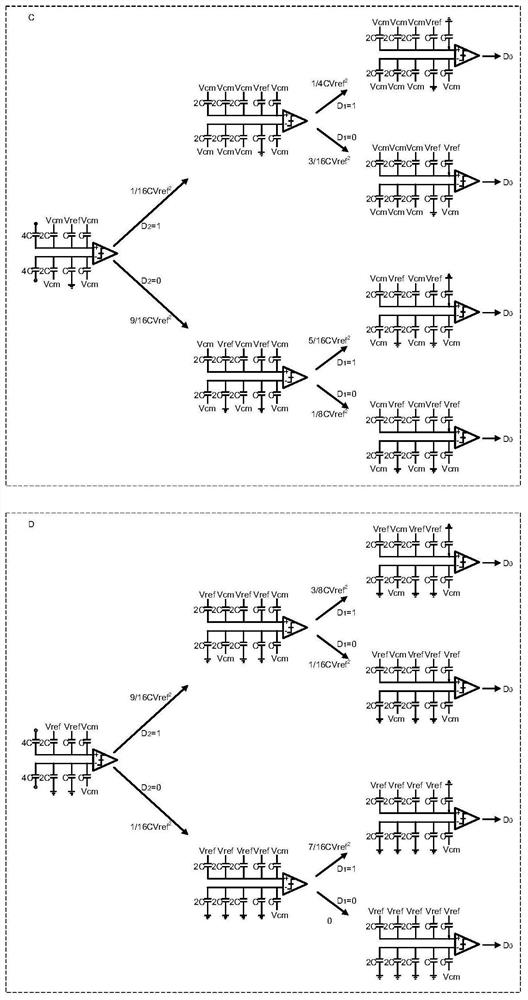

The invention discloses a binary capacitor array applied to a near-threshold SARADC and a switching method with low power consumption thereof. By means of special construction of a core module thereof, namely a DAC capacitor array, the power consumption of the DAC part in the conversion process of the SARADC can be greatly reduced in combination with a provided new switching algorithm. Only two reference levels are adopted in the algorithm, such that the algorithm is applied to designing the SARADC under near-threshold voltage. Compared with the area of the capacitor array required by the ordinary two-level capacitor switching technology, by means of flexible application of united, split and floating capacitor switching technologies, the total area of the capacitor array is reduced by 50%.

Owner:SOUTHEAST UNIV

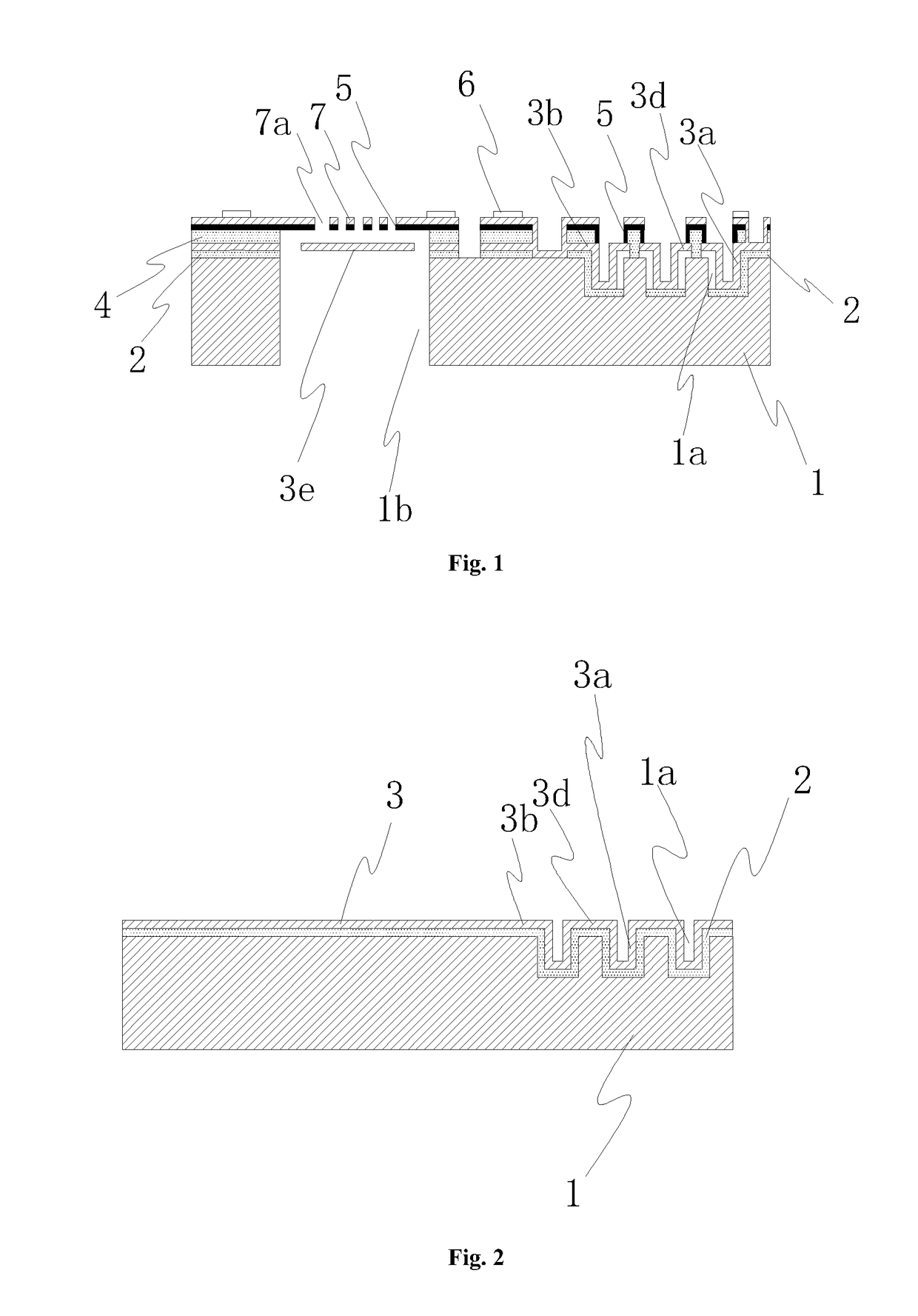

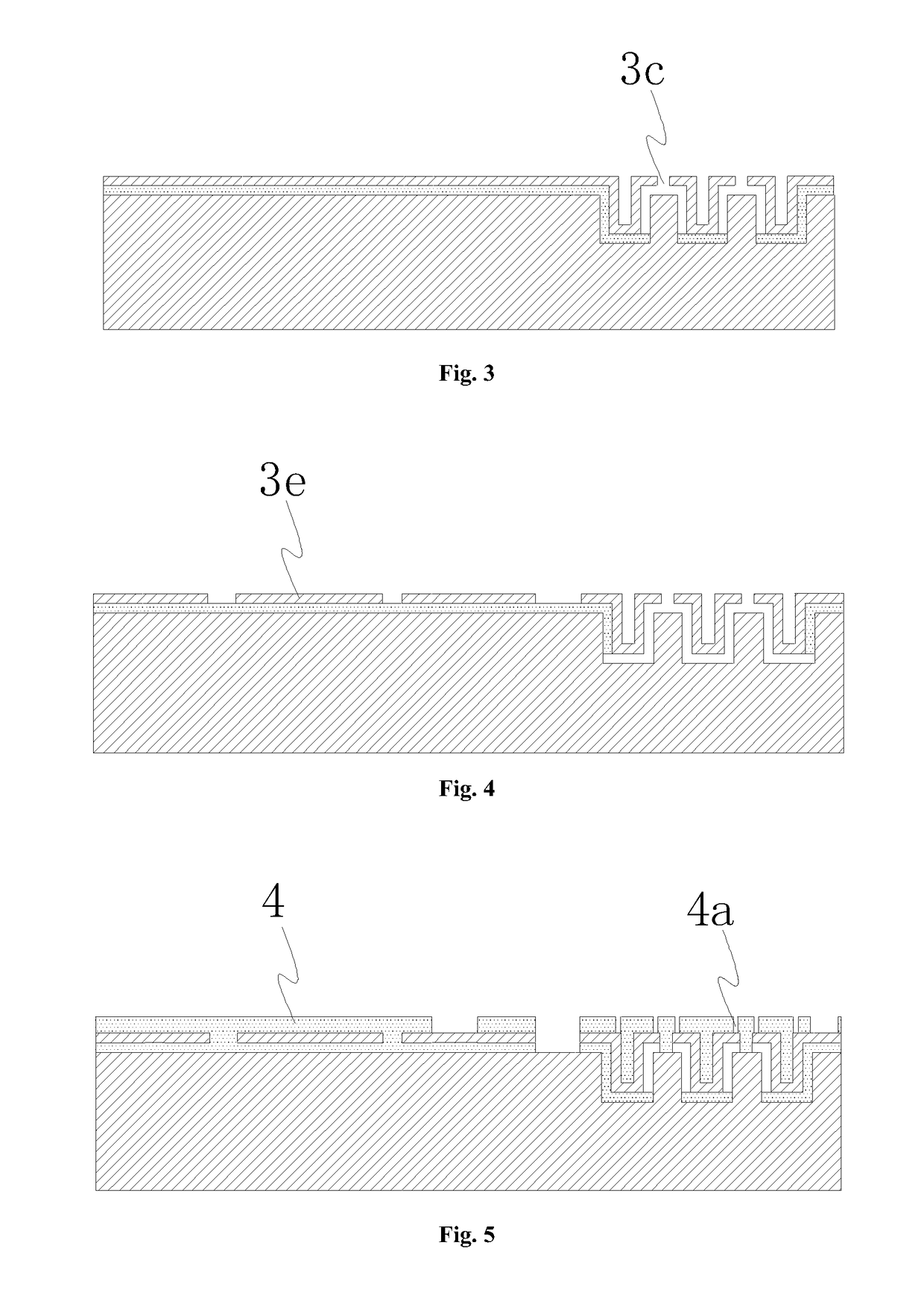

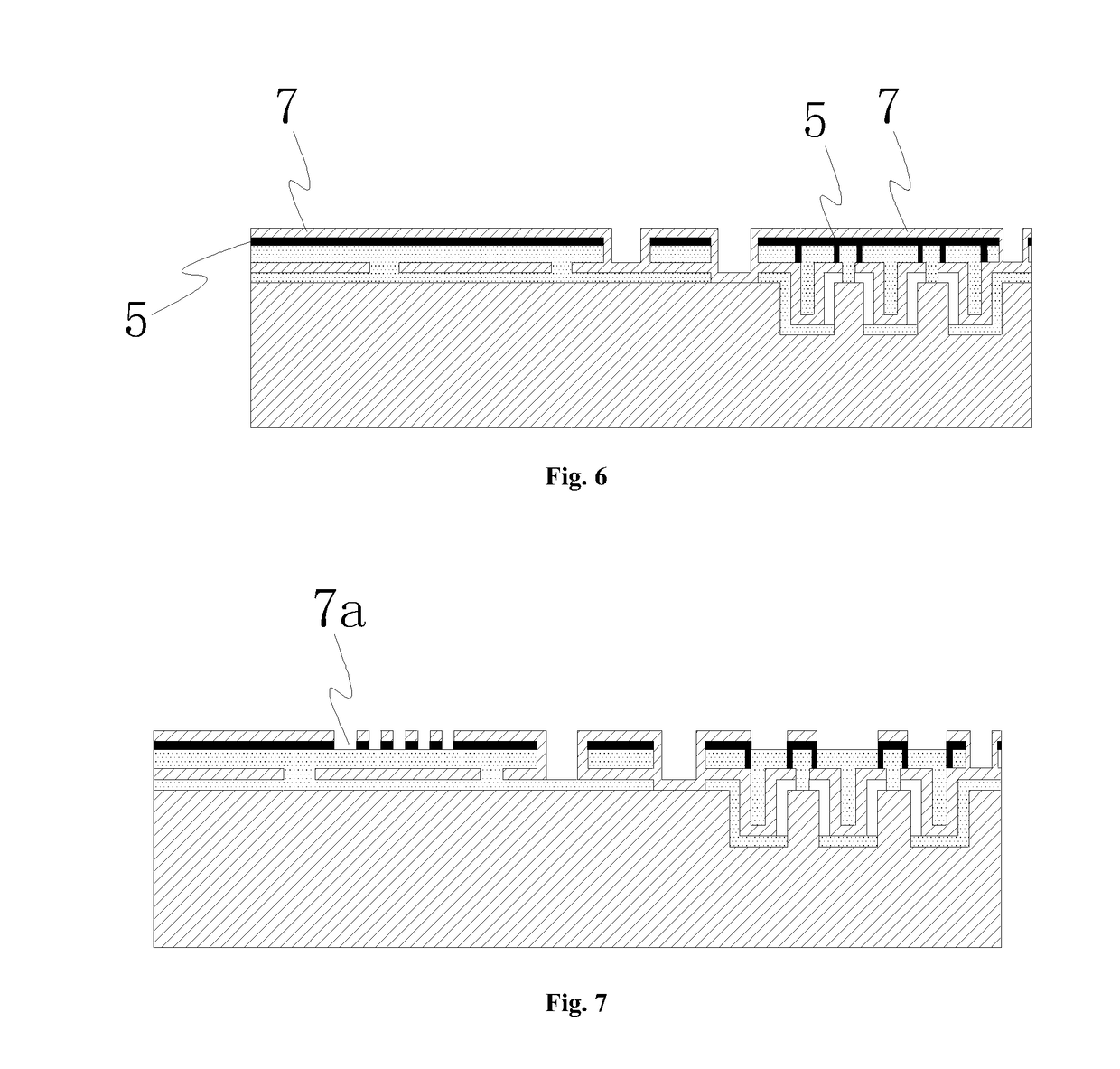

Acoustic sensor integrated MEMS microphone structure and fabrication method thereof

ActiveUS20180359571A1Small sizeIncrease productivityMicrophonesDecorative surface effectsEngineeringMems microphone

An acoustic sensor integrated MEMS microphone structure and a fabrication method thereof. A diaphragm (3e) and back-pole (7) which forms a condenser structure are formed on a substrate (1) having at least one recessed slot (1a) on the top. A sensitive electrode is formed on the substrate (1), the sensitive electrode comprising a fixed portion (3b) fixed on the substrate (1) via a sacrificial layer (2), and a bending portion (3a) inserted into the recessed slot (1a), wherein the bending portion and the side wall of the recessed slot form the condenser structure. The integrated structure integrates the condenser structure of the microphone and condenser structure of the acoustic sensor on a substrate (1), thereby increasing the integration level thereof and reducing the overall size of the package. Meanwhile, the microphone diaphragm (3e) and the sensitive electrode of the acoustic sensor can be fabricated on a same substrate (1) at the same time, from the same material, and using the same fabricating process to increase production efficiency.

Owner:WEIFANG GOERTEK MICROELECTRONICS CO LTD

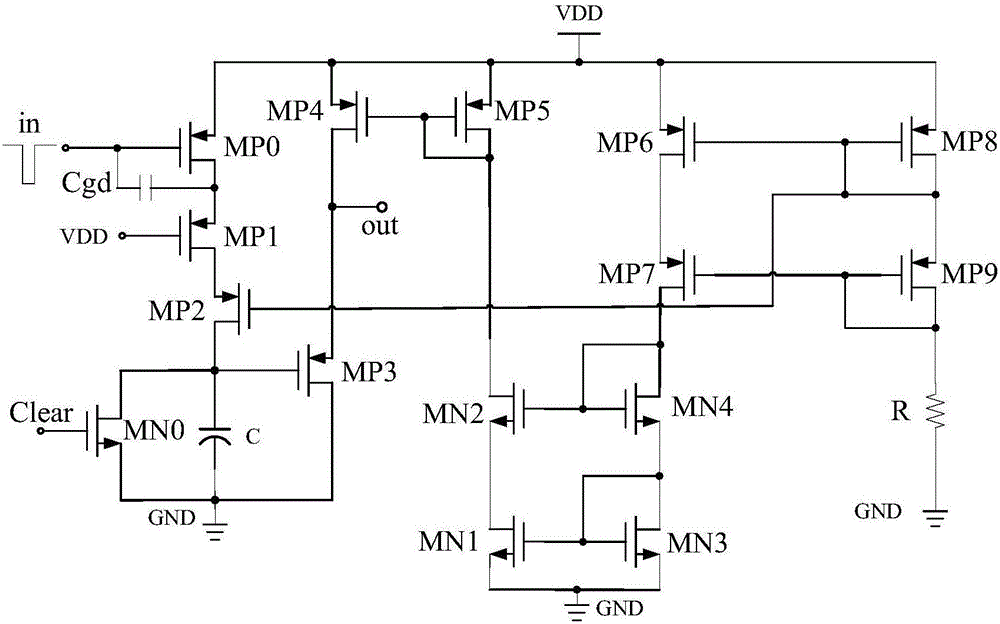

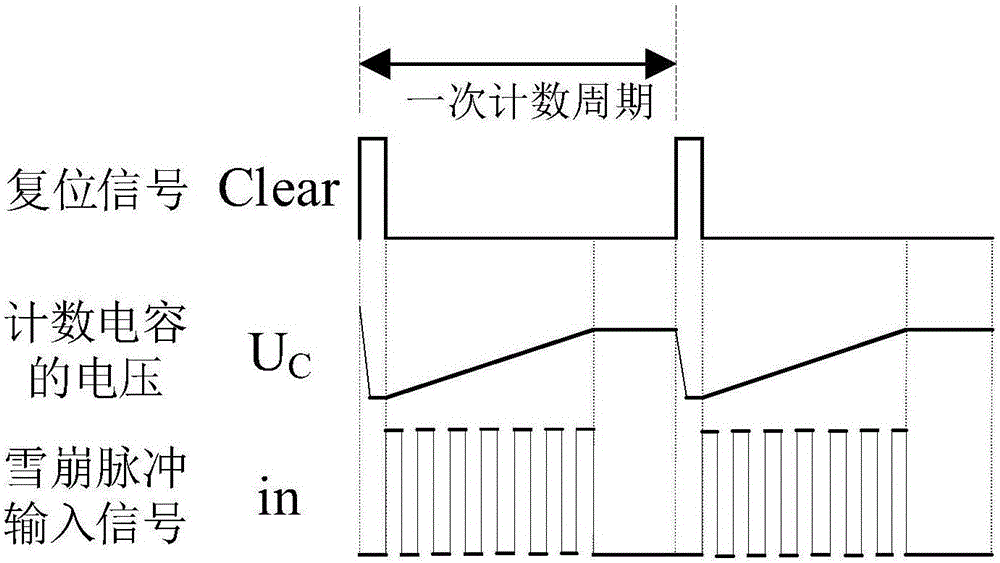

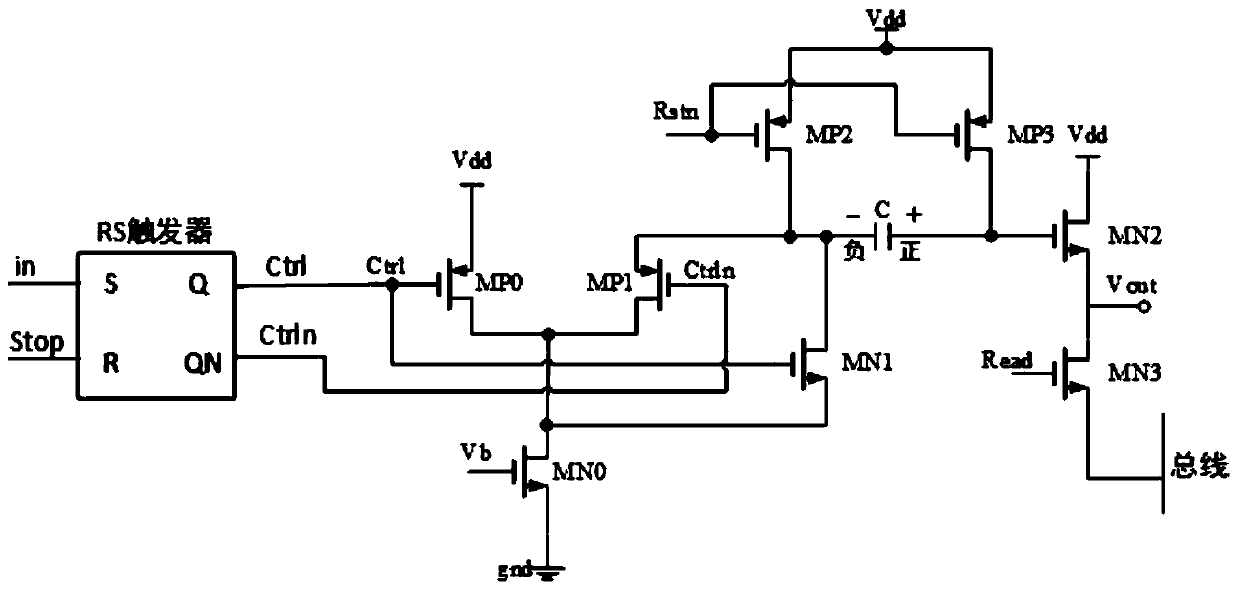

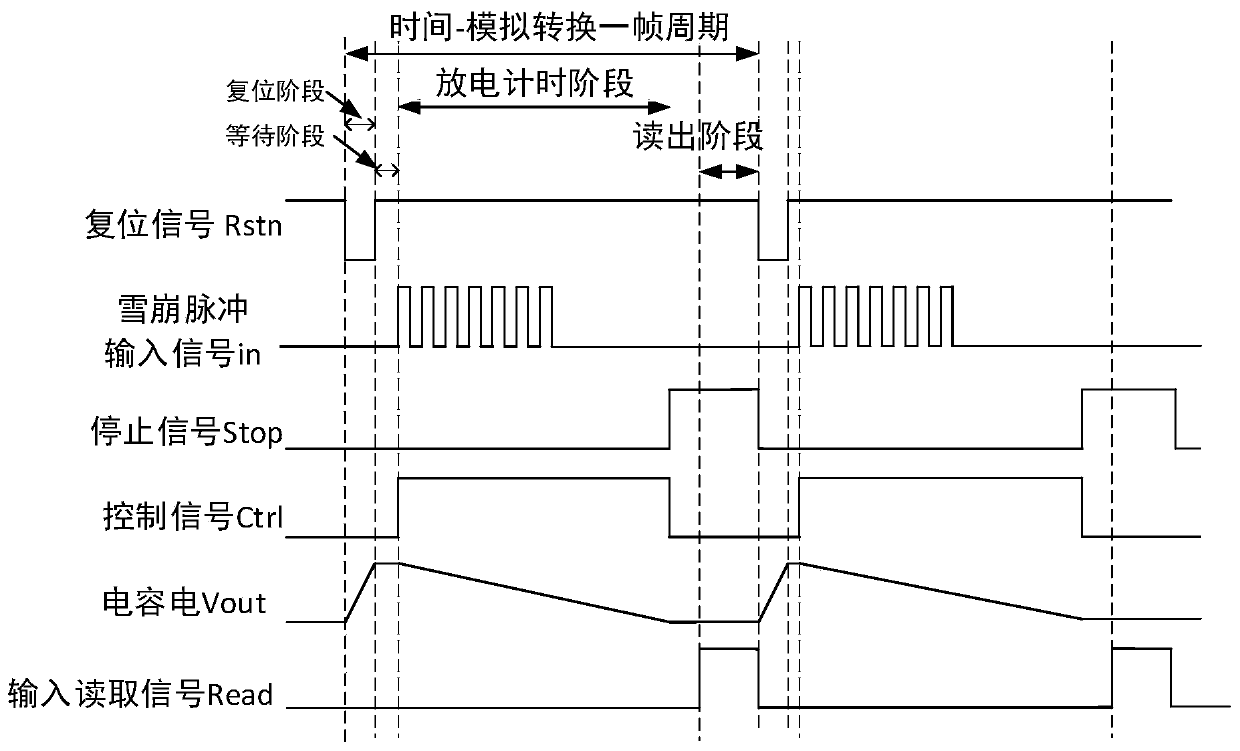

Analog counting circuit with high counting range applied to single photon avalanche diode (SPAD) detector

ActiveCN106656166ACapacitor area is smallLarge counting rangeCounting chain pulse counters using semiconductor devices with 2 electrodesElectrical resistance and conductanceCapacitance

The invention discloses an analog counting circuit with a high counting range applied to a single photon avalanche diode (SPAD) detector. The circuit is composed of a counting capacitor C, a resistor R and fifteen MOS transistors, wherein a Cascode biasing circuit is formed by the NMOS transistors MN3 and MN4, the PMOS transistors MP6, MP7, MP8 and MP9, and the resistor R for providing bias for the counting circuit; meanwhile, the biasing circuit also provides a current source load for an output follower of the counting circuit, so that linear output of a counter is ensured; the biasing circuit also provides a biasing voltage with high level for the current-limiting PMOS transistor, thus playing a role in preventing the breakover current from being excessive on a charging branch of the counting capacitor. The invention also provides a counting method by using the analog counting circuit with the high counting range applied to the SPAD detector. The method comprises three stages consisting of a resetting stage, a counting stage and a reading stage. The analog counting circuit provided by the invention can reduce capacitor area and is large in counting range, and also has the advantage of high filling coefficient of a pixel unit.

Owner:NANJING UNIV OF POSTS & TELECOMM

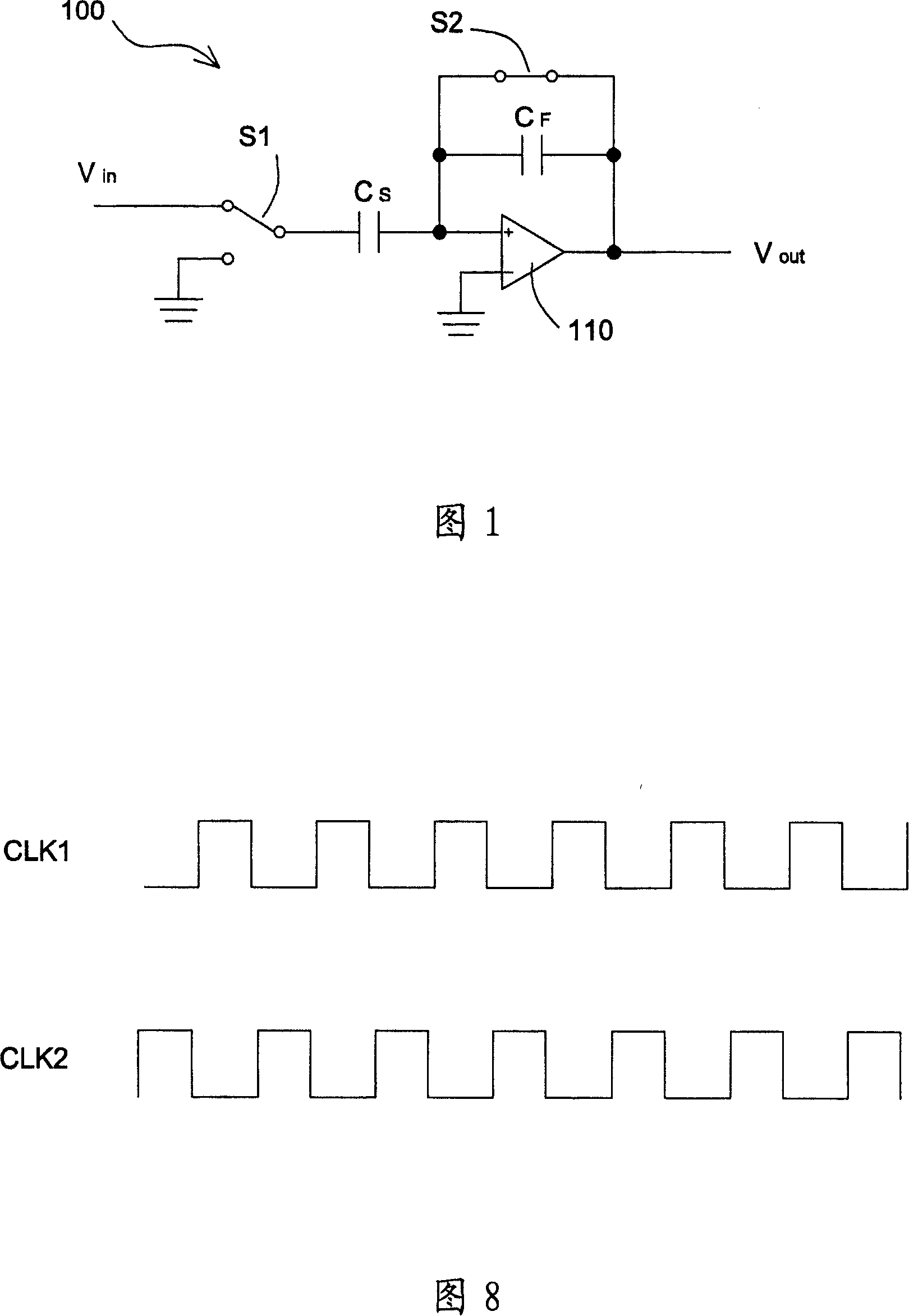

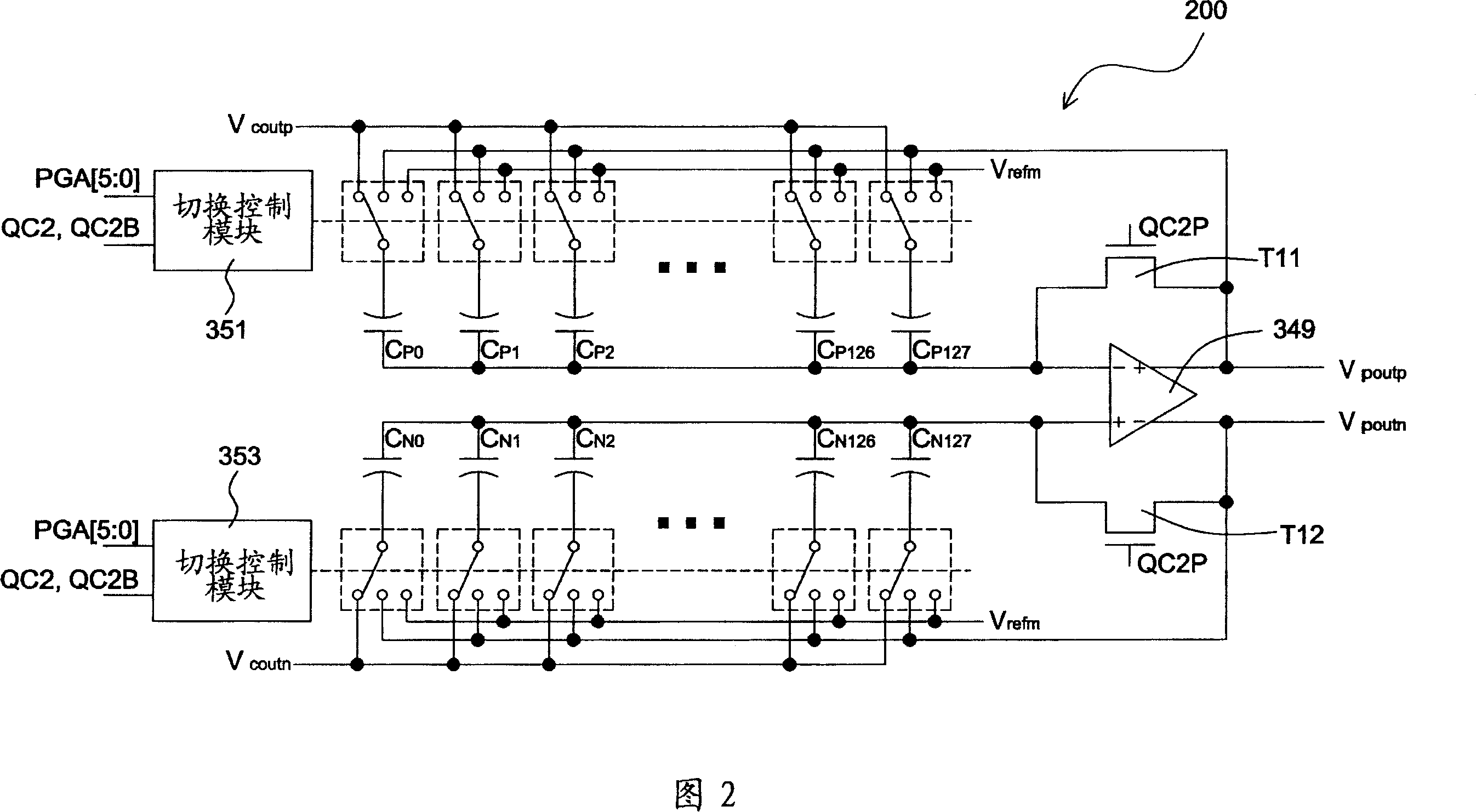

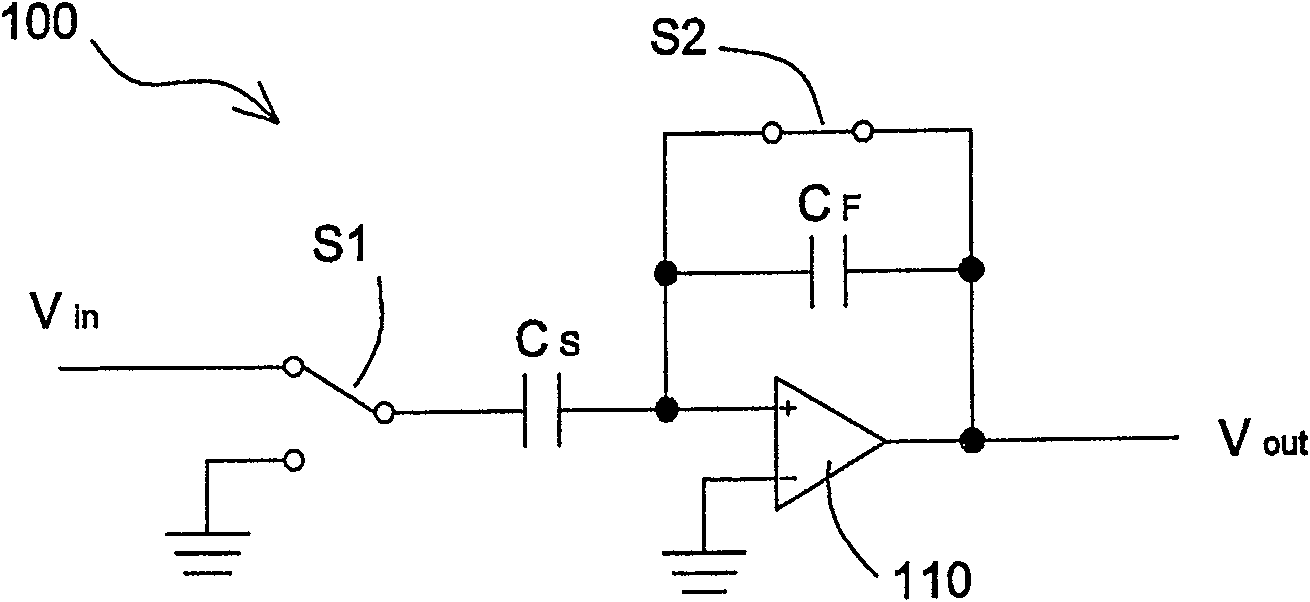

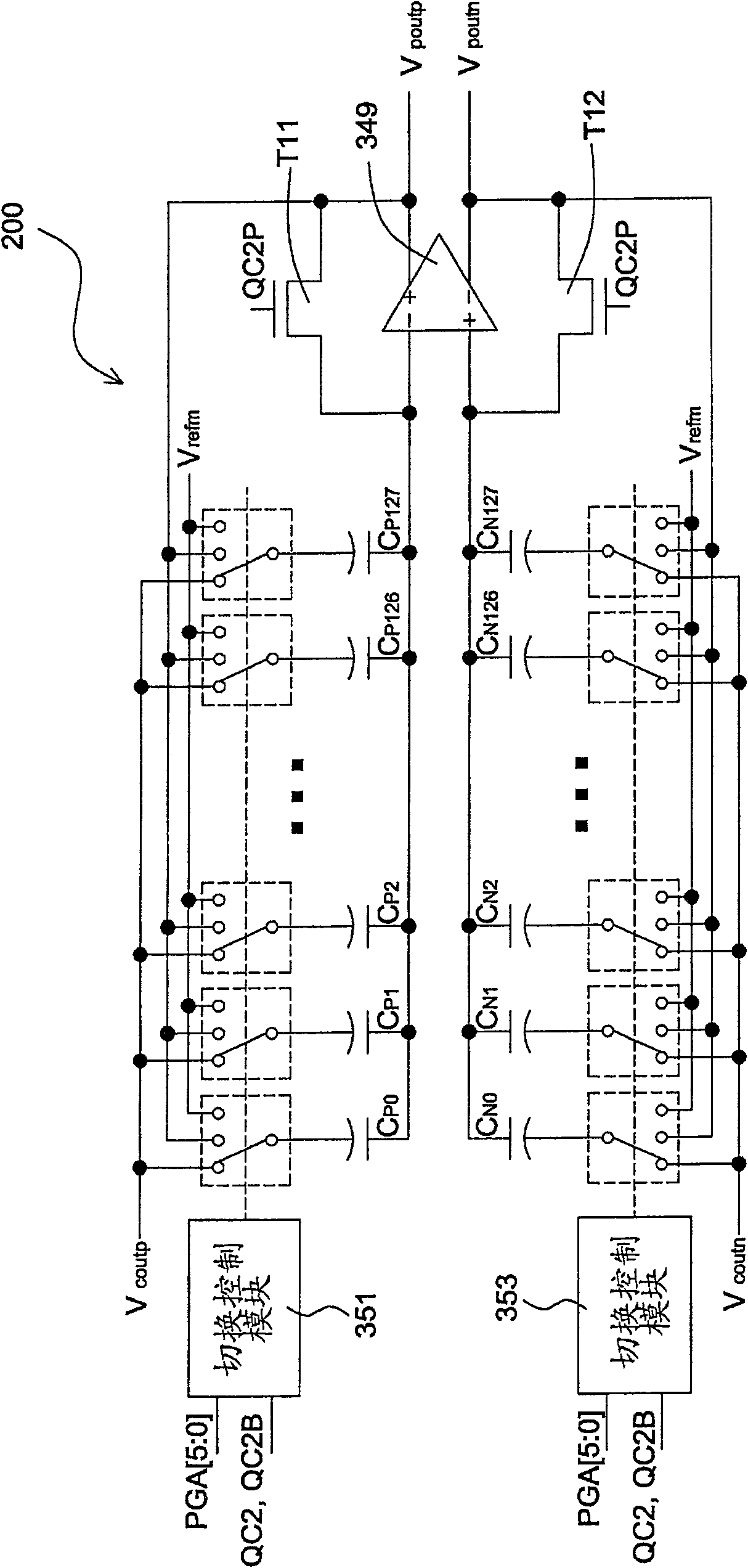

Programmable gain amplifier

InactiveCN101132177AReduce areaCapacitor area is smallAnalogue-digital convertersCapacitanceUltrasound attenuation

A programmable gain amplifier comprises: an operational amplifier, N (N>0) attenuation capacitances, N+1 group of control capacitance modules, multiple change-over switches, a change-over control module and a feedback switch. Each group of control capacitance module has at least one control capacitance. Each change-over switch is controlled by the change-over control module, the common ends of the switches are respectively connected with the second end of the control capacitances, the capacitances, by said connection, are connected with an input signal, a reference voltage, or the output end of the operational amplifier. The feedback amplifier connects between the output end and No.1 input end of the operational amplifier, it is getting-through at No.1 phase period, and cutting-off at other period. At No.2 phase period, the control capacitance can be connected, controlled by the change-over switch, the output end of the operational amplifier to be used as feedback capacitance.

Owner:SUNPLUS TECH CO LTD

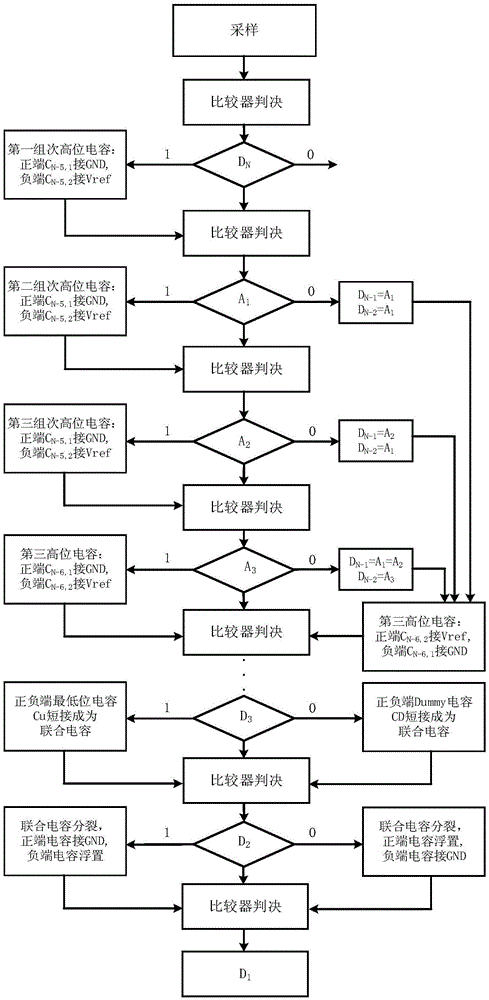

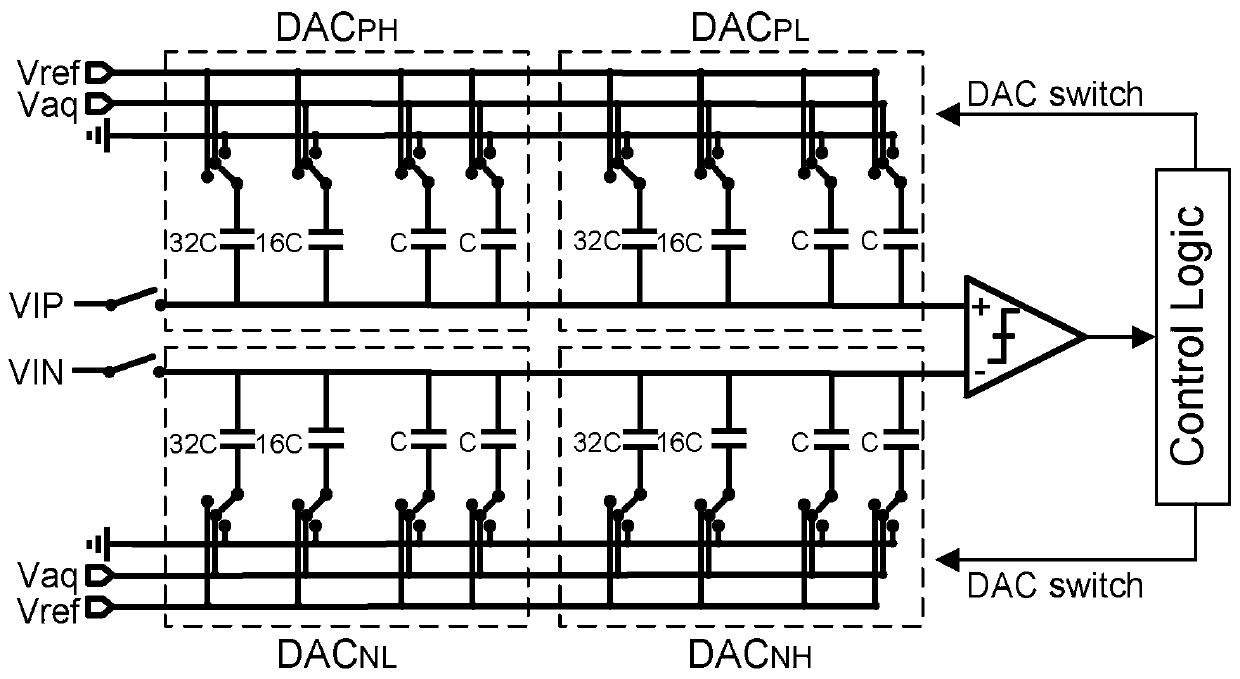

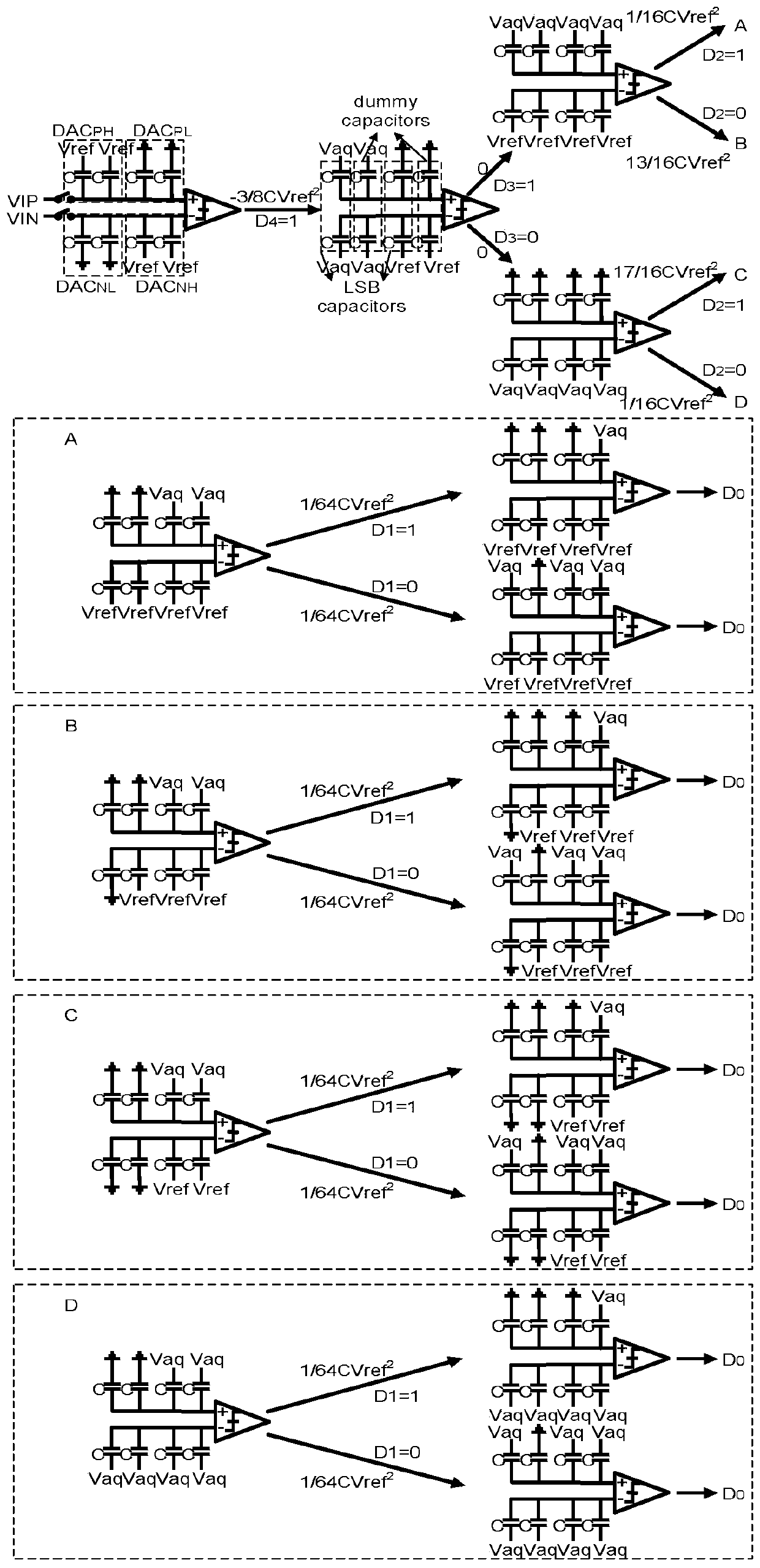

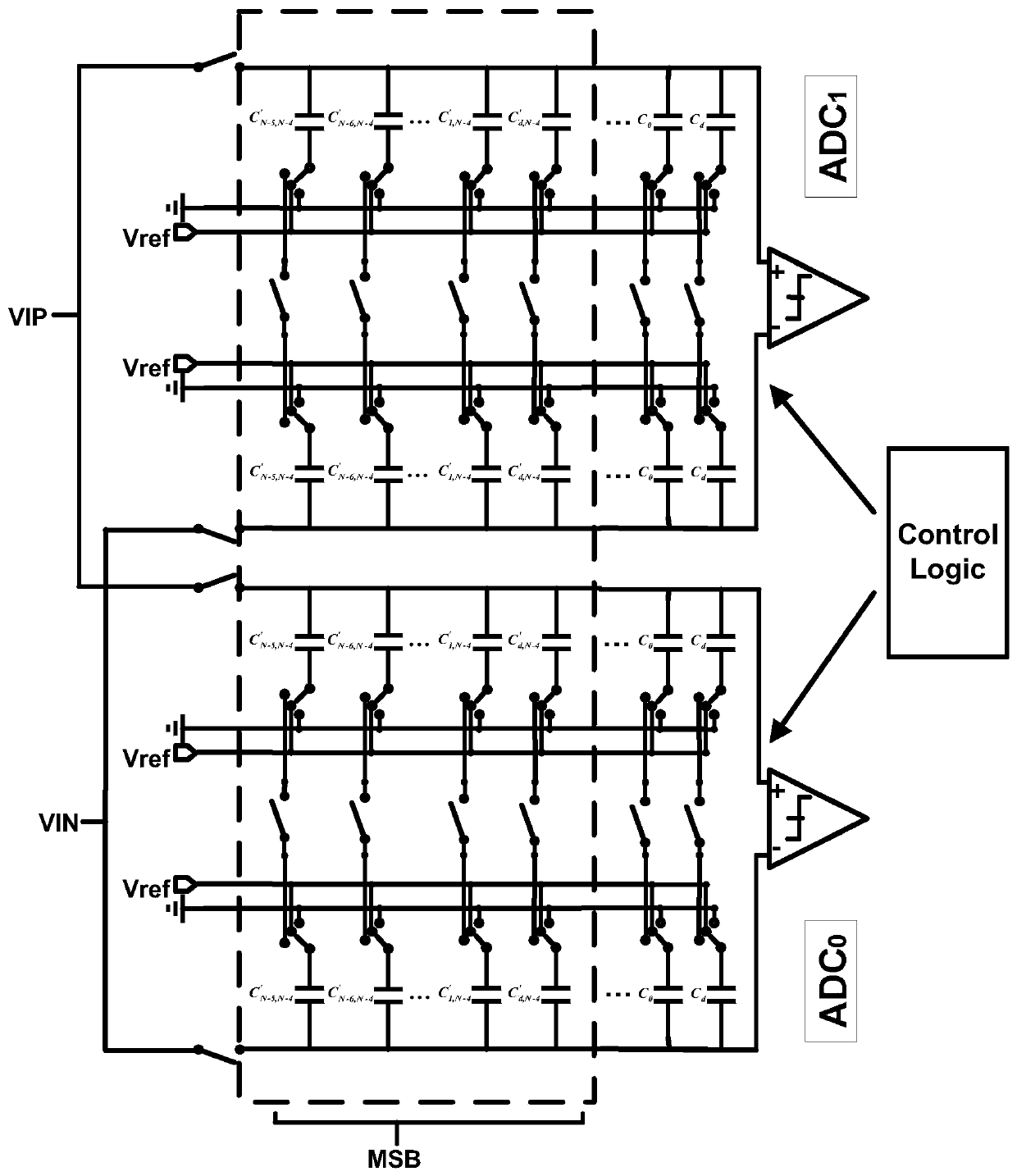

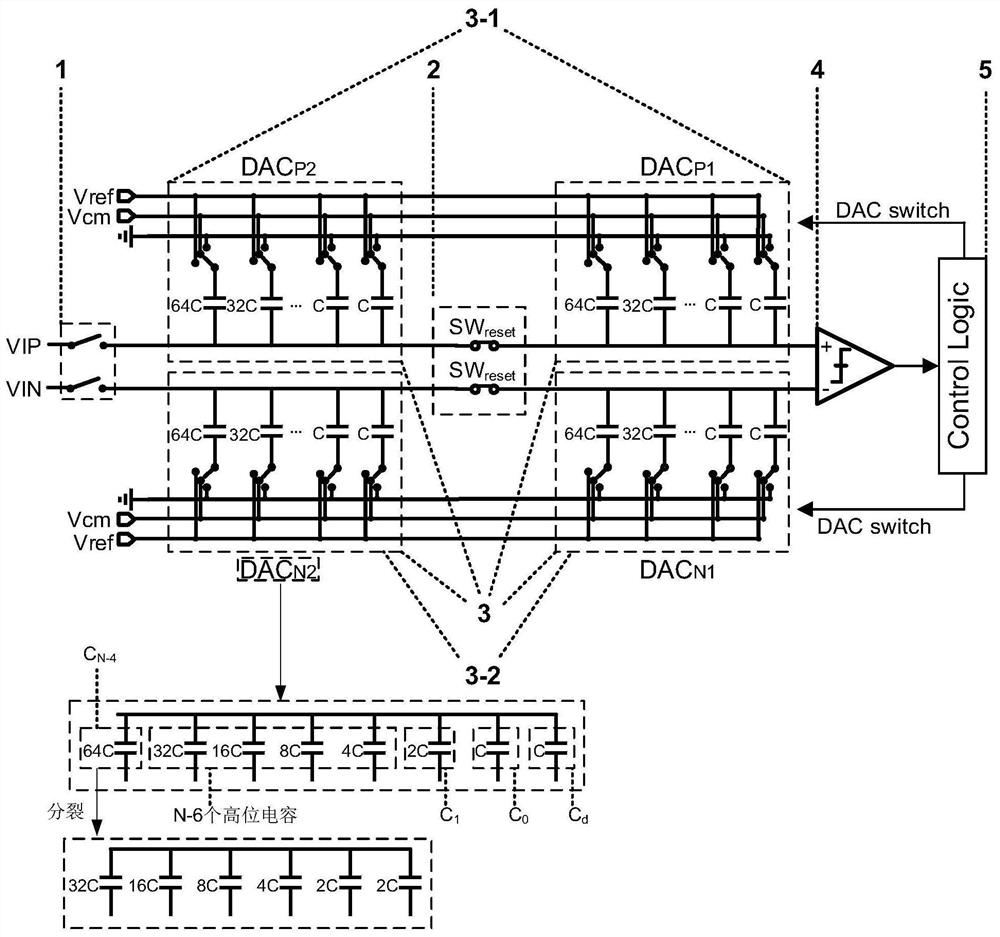

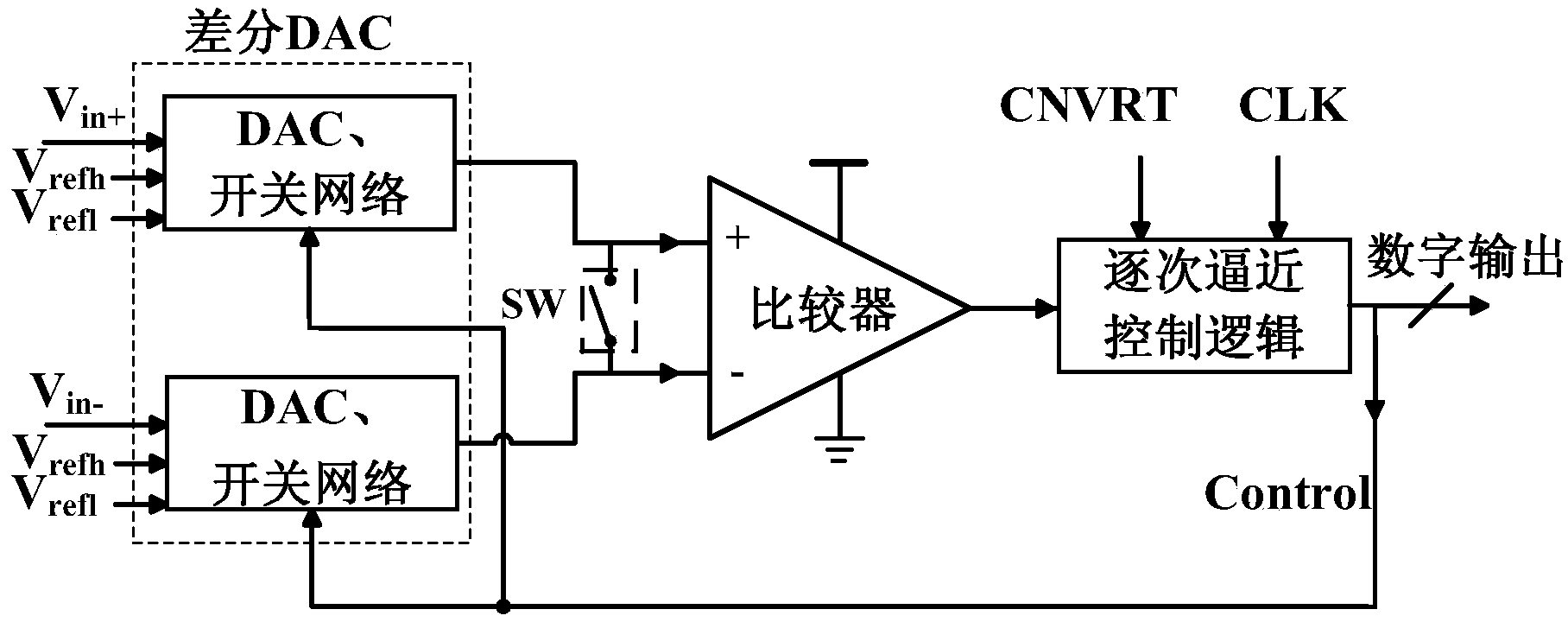

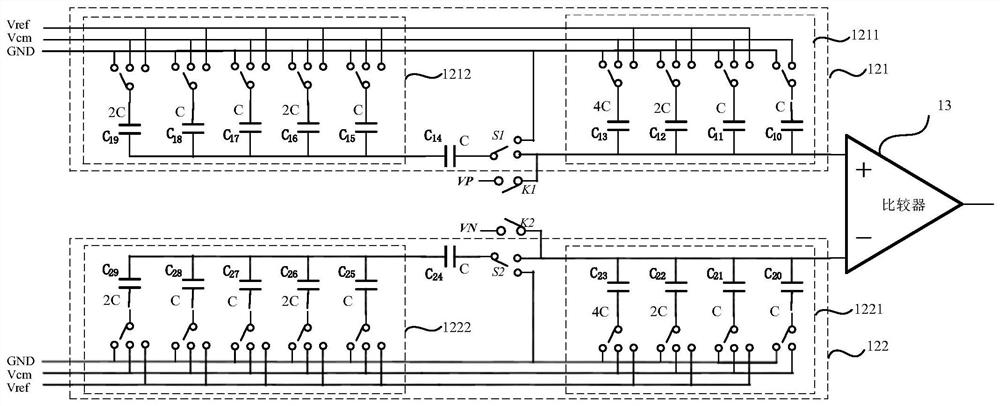

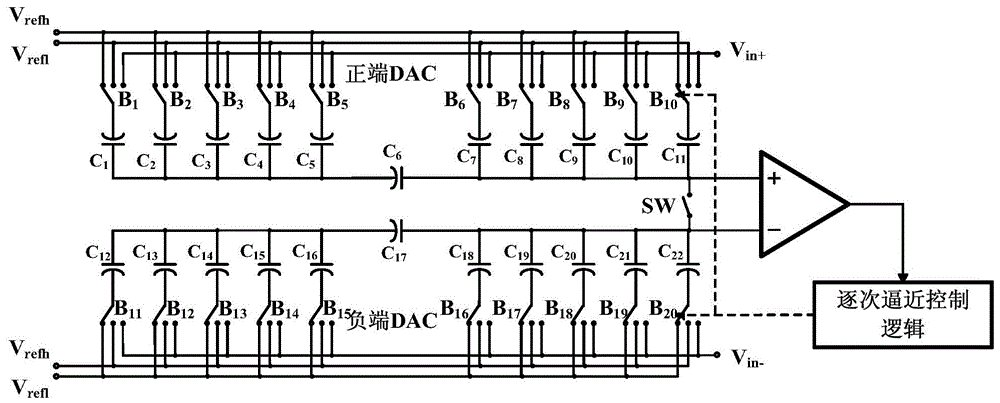

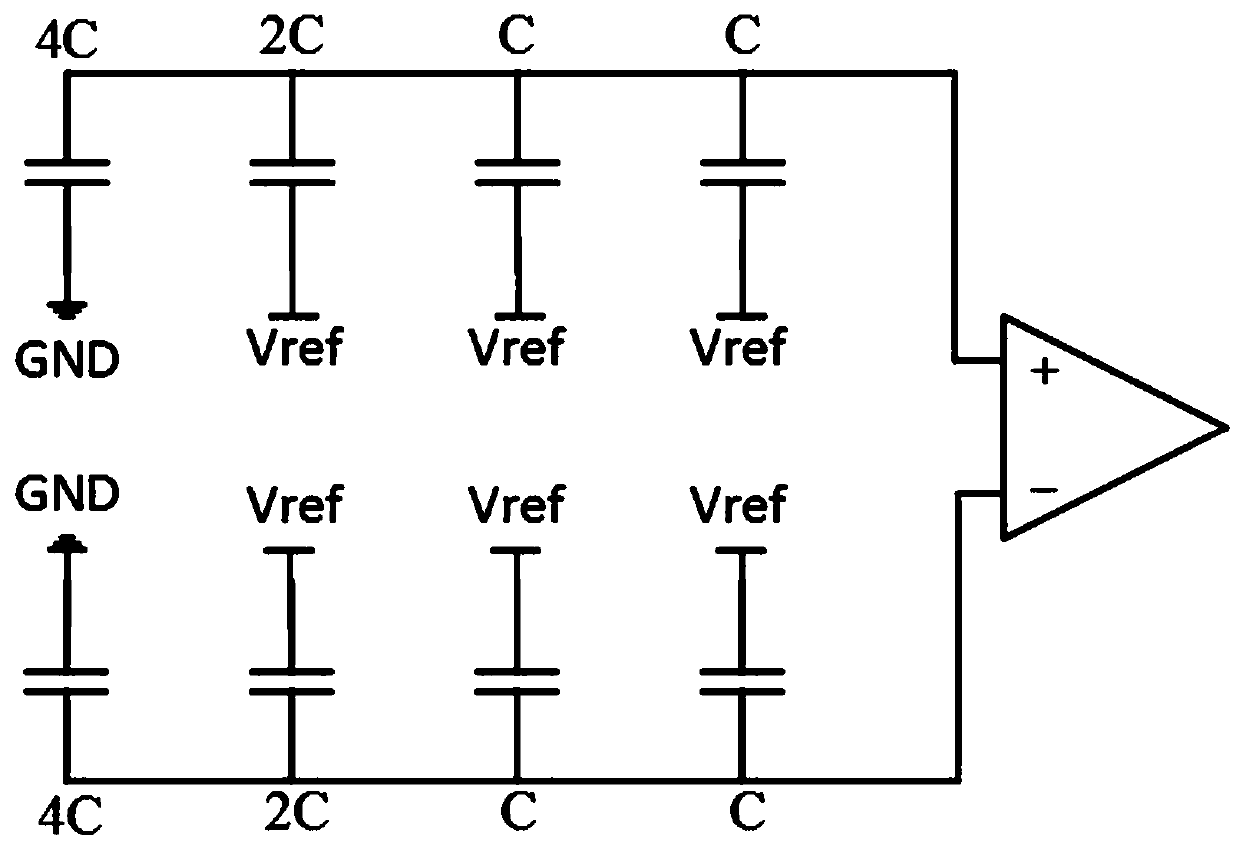

Analog-to-digital converter and three-level switching method applied to SAR ADC

ActiveCN111371457AReduce power consumptionCapacitor area is smallAnalogue/digital conversionElectric signal transmission systemsCapacitanceConverters

The invention discloses an analog-to-digital converter and a three-level switching method applied to an SAR ADC. The method belongs to the technical field of capacitive DACs of SAR ADCs, the whole process is divided into a sampling stage and a conversion stage, and the sampling stage is connected to top polar plates of an upper capacitor array and a lower capacitor array through sampling switchesaccording to input signals VIP and VIN; in the conversion stage, the comparator performs MSB bit-to-LSB bit comparison on the voltages of the top polar plates of the upper and lower capacitor arrays to obtain corresponding digital codes, and controls the connection relationship of the capacitor bottom polar plates in the upper and lower capacitor arrays according to the digital codes; and obtaining an N-bit digital output code through N times of comparison. Different from most published three-level switching methods, a new third reference level Vaq is adopted, and the value of the new third reference level Vaq is equal to one fourth of the reference voltage Vref. Compared with a traditional switching algorithm, the method has the advantages that 99.61% of power consumption of the capacitorsplit type DAC can be reduced, 87.5% of capacitor area is saved, and good compromise between energy efficiency and area saving is achieved.

Owner:SOUTHEAST UNIV

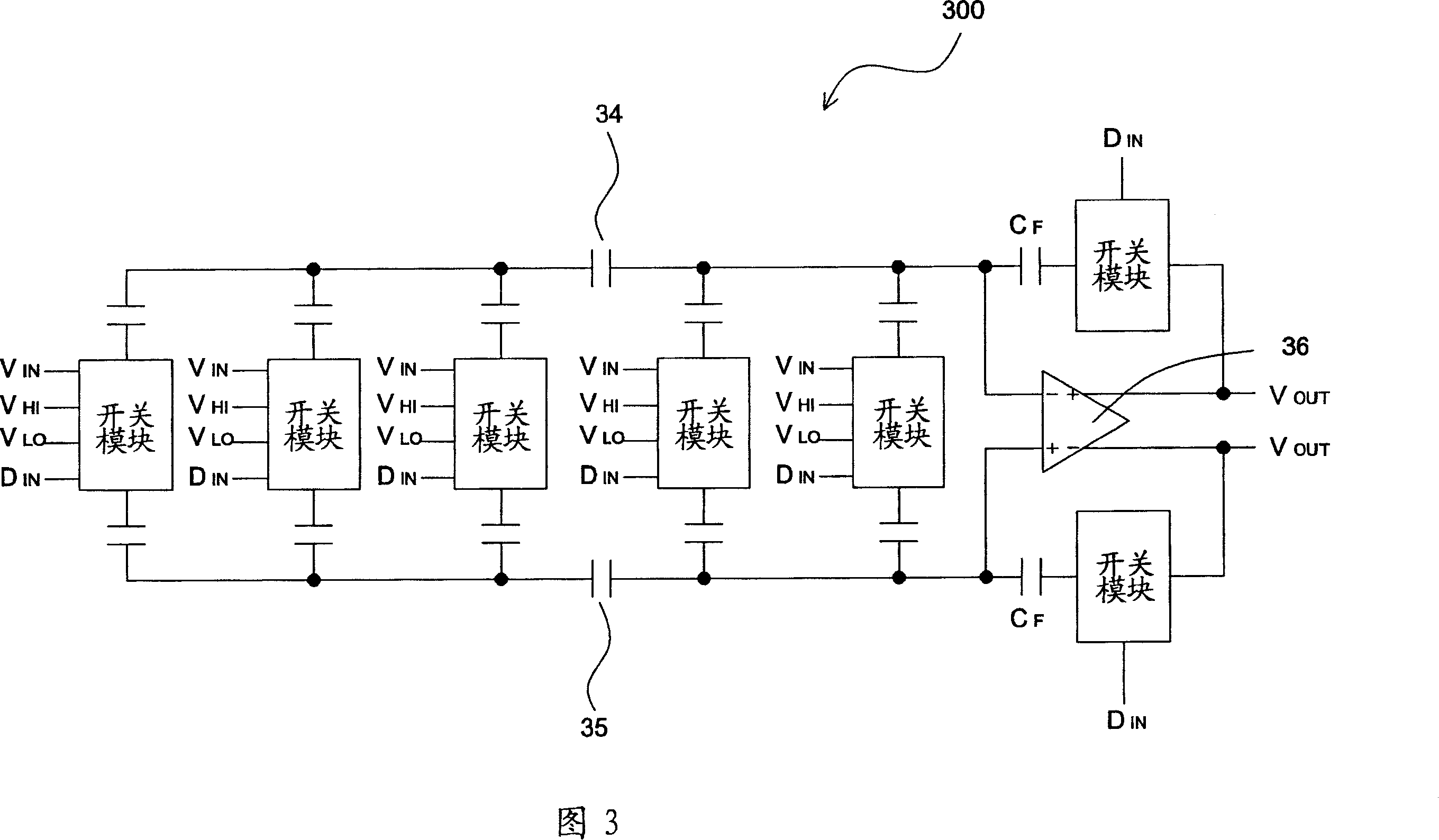

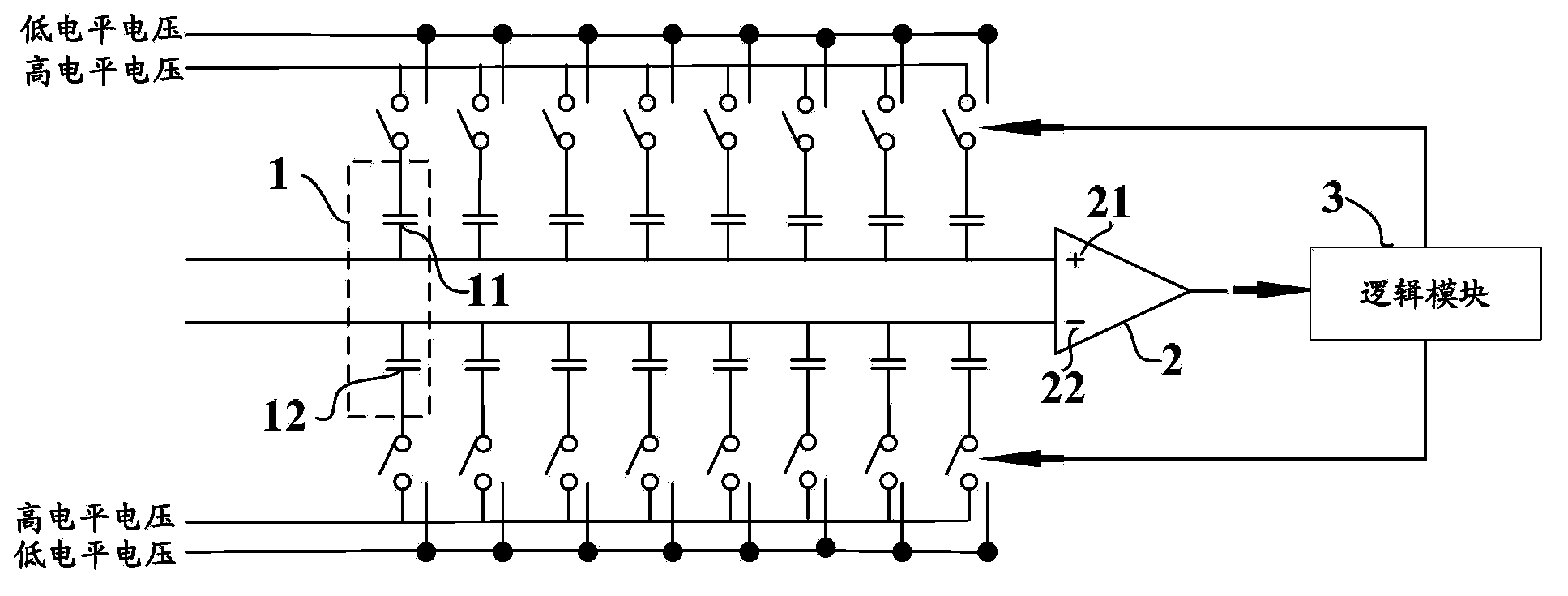

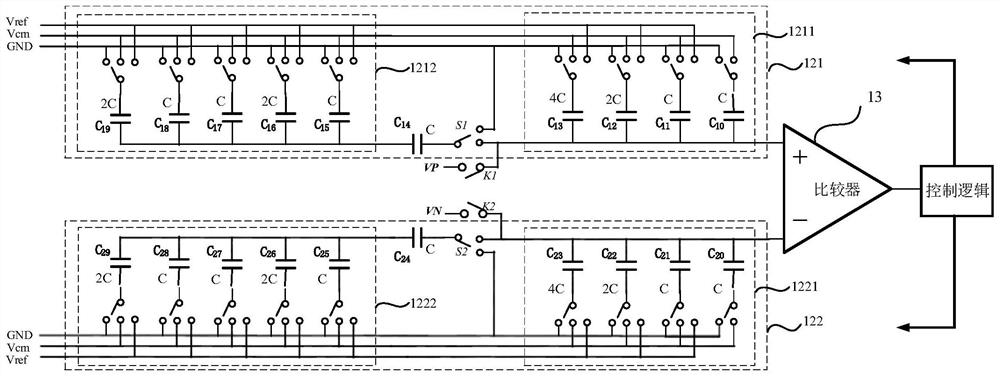

High-speed switch time sequence for successive approximation type analog-digital converter

ActiveCN104218952ACapacitor area is smallFast conversionAnalogue/digital conversionElectric signal transmission systemsA d converterCapacitance

The invention provides a high-speed switch time sequence for a successive approximation type analog-digital converter. The analog-digital converter comprises N orderly connected capacitor banks, each capacitor bank comprises a first capacitor array and a second capacitor array; the first capacitor bank is in a second connection state, and other capacitor banks are in a first connection state; the first connection state is as follows: a lower pole plate of the first capacitor array is connected with low-level voltage, a lower pole plate of the second capacitor array is connected with high-level voltage; the second connection state is as follows: the lower pole plate of the first capacitor array is connected with the high-level voltage, and the lower pole plate of the second capacitor array is connected with the low-level voltage; the high-speed switch time sequence further comprises a comparator, upper pole plates of all first capacitor arrays are connected with a first input end of the comparator, the upper pole plates of all second capacitor arrays are connected with a second input end of the comparator; a logic module is connected with the comparator and used for controlling the connection states of the capacitor banks according to internally stored time slot instructions. According to the time sequence provided by the invention, the capacitance area of the analog-digital converter is smaller, and the conversion speed is faster.

Owner:XIDIAN UNIV

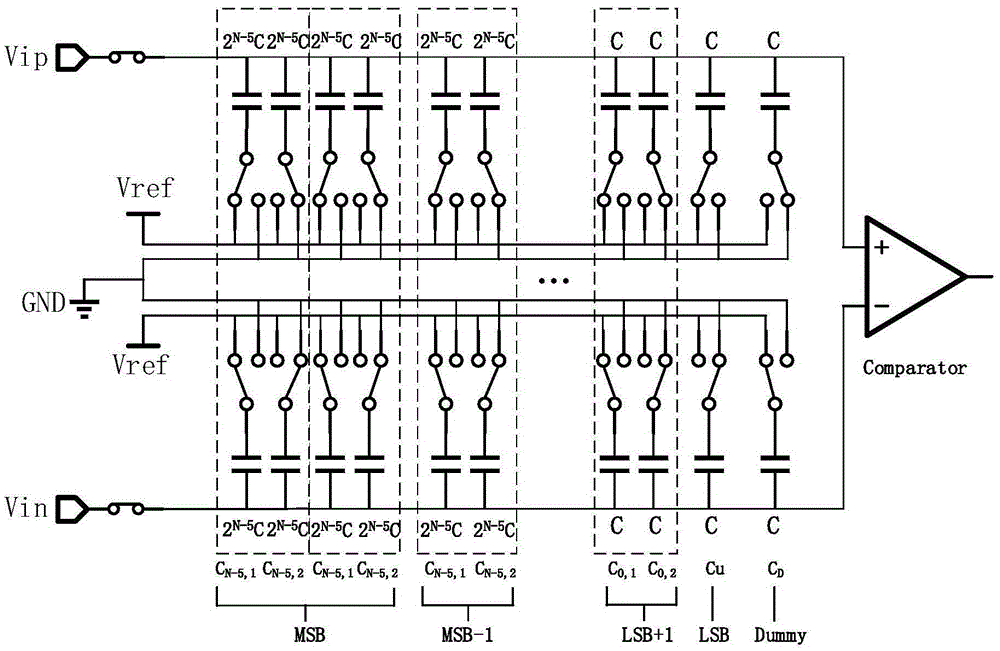

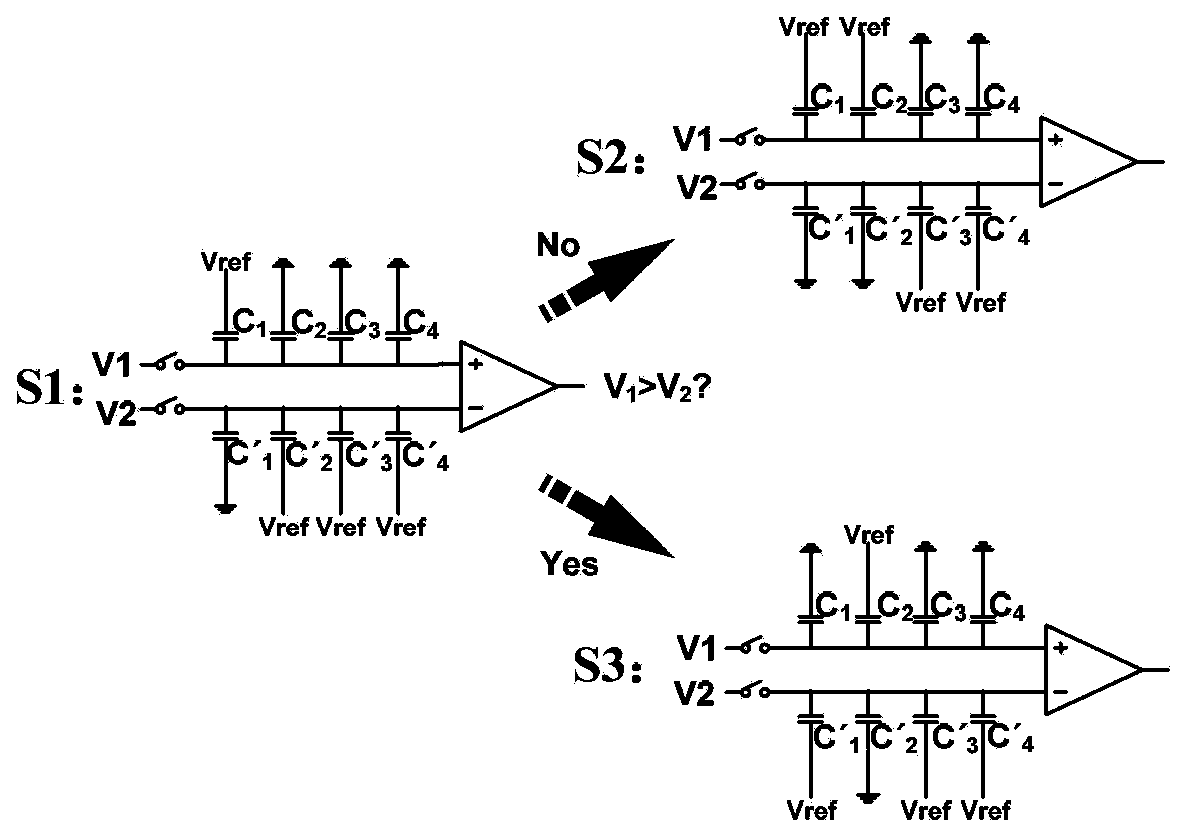

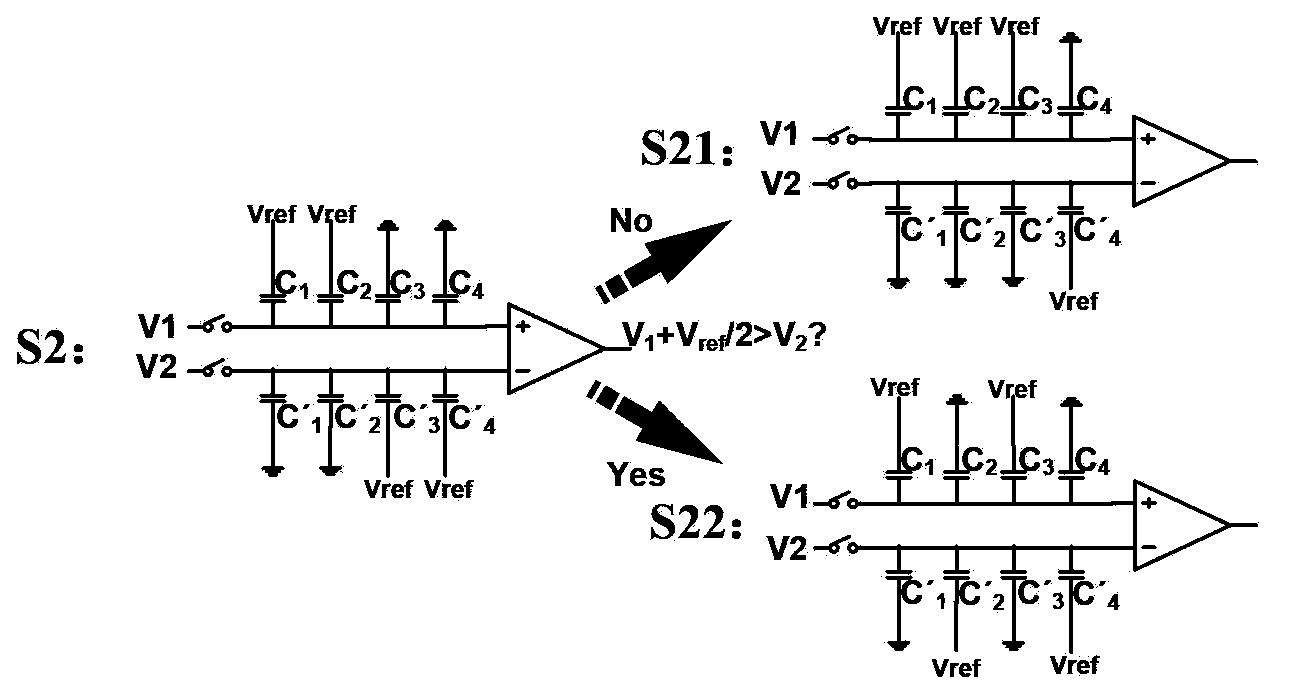

Capacitor array switching method applied to low-voltage SAR ADC

ActiveCN110380730AImprove signal-to-noise ratioReduce Switching Power ConsumptionAnalogue/digital conversionElectric signal transmission systemsCapacitanceLow voltage

The invention discloses a capacitor array switching method applied to a low-voltage SAR ADC. An analog-to-digital converter based on the method comprises two N-bit sub analog-to-digital converters with the same structure, the method comprises the following steps: for the input signals VIP and VIN, after N comparisons, obtaining N-bit digital output codes, which are divided into a sampling stage and a conversion stage, wherein, in the sampling stage, the input signals VIP and VIN are respectively connected to top polar plates of an upper capacitor array and a lower capacitor array through sampling switches, and bottom polar plates of all capacitors of the upper capacitor array and bottom polar plates of all capacitors of the lower capacitor array are connected to corresponding voltages; and, in the conversion stage, the comparator performs MSB bit-to-LSB bit comparison on the voltages of the top polar plates of the upper and lower capacitor arrays to obtain corresponding digital codes,and the connection relationship of the capacitor bottom polar plates in the upper and lower capacitor arrays are controlled according to the digital codes, and the N-bit digital output codes are obtained through N times of comparison. According to the invention, the power consumption of the DAC part in the conversion process can be greatly reduced, only two reference levels are adopted, and the method is suitable for the design under the near threshold voltage.

Owner:SOUTHEAST UNIV

Successive approximation type analog-to-digital converter and three-level switching method thereof

PendingCN112583409AReduce Switching Power ConsumptionReduce power consumptionAnalogue/digital conversionElectric signal transmission systemsCapacitanceA d converter

The invention discloses a successive approximation type analog-to-digital converter and a three-level switching method thereof. The method comprises the steps that input signals VIP and VIN are compared N times to obtain an N-bit digital code, the N-bit digital code is divided into a sampling stage and a conversion stage, and in the sampling stage, the input signals VIP and VIN are connected to top polar plates of an upper capacitor array and a lower capacitor array through sampling switches respectively, and the bottom polar plate of each capacitor is connected to a corresponding voltage; inthe conversion stage, the comparator performs MSB bit-to-LSB bit comparison on the voltages of the top electrode plates of the upper capacitor array and the lower capacitor array to obtain corresponding digital codes, and the connection relation of the capacitor bottom electrode plates in the capacitor arrays is controlled according to the digital codes; and comparing for N times is performed to obtain an N-bit digital code. According to the invention, the voltage change of + / -Vref is generated on the top plate of the capacitor for the first time, so that the reference voltage Vref of the capacitor array is reduced to half of the reference voltage Vref of a common method. Compared with a traditional switching algorithm, the method has the advantages that 99.79% of DAC power consumption isreduced, 75% of capacitance area is saved, common-mode level offset is only 0.5 LSB, and compromise of energy efficiency, area and common-mode level is achieved.

Owner:SOUTHEAST UNIV

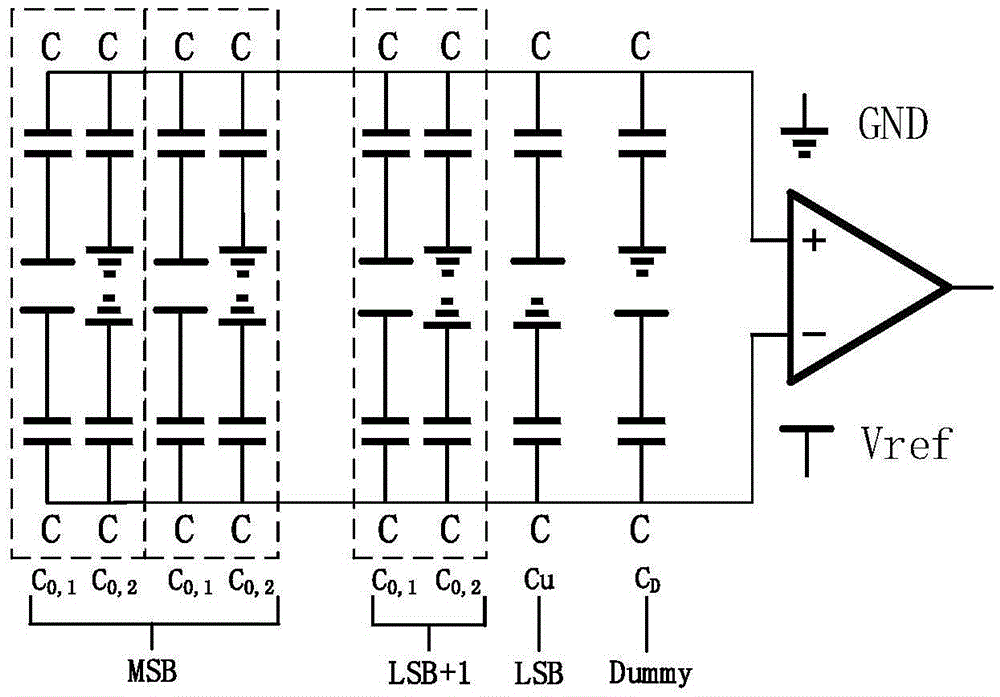

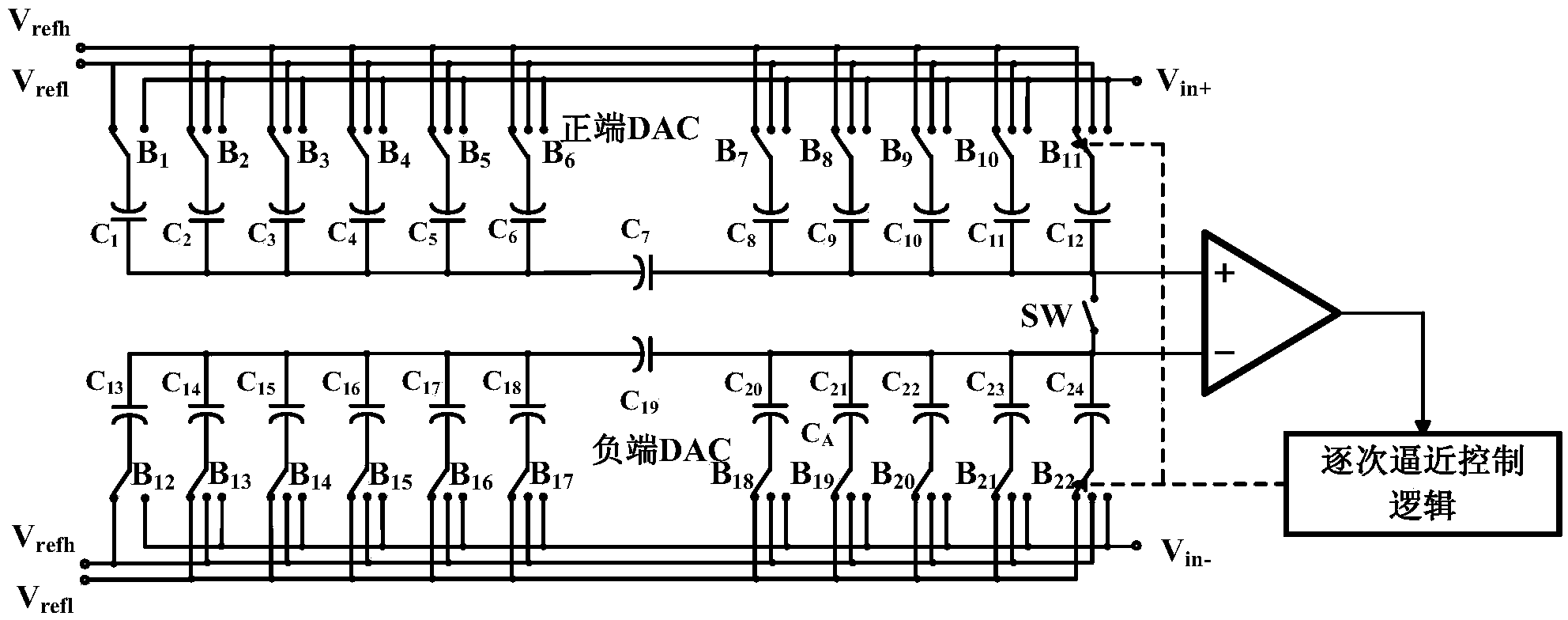

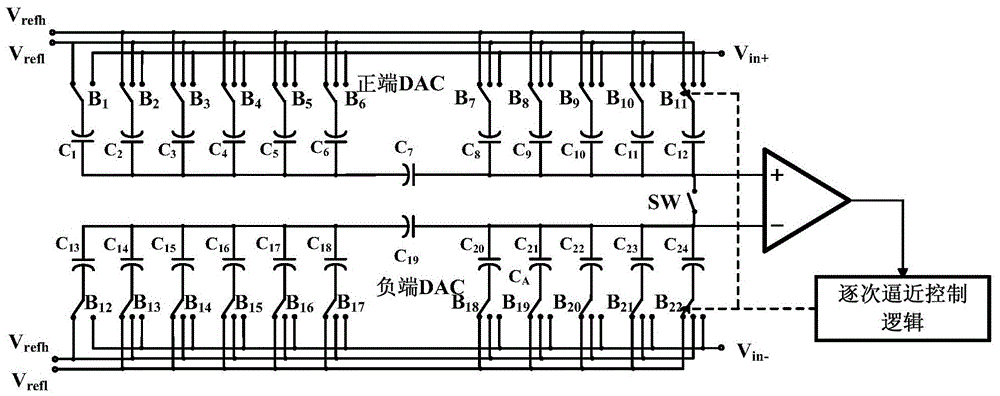

Improved 10-bit differential capacitance segmented coupling type DAC

ActiveCN104038223AHigh precisionReduce areaAnalogue/digital conversion calibration/testingCapacitanceCoupling

The invention discloses an improved 10-bit differential capacitance segmented coupling type DAC. The improved 10-bit differential capacitance segmented coupling type DAC comprises a positive secondary capacitance array, a positive coupling capacitor, a positive main capacitance array, a negative coupling capacitor, a negative main capacitance array and a sampling switch. The improved 10-bit differential capacitance segmented coupling type DAC uses a 12-bit differential DAC to realize the 10-bit differential DAC, the gain error of a 1-LSB is avoided, and the static property of the DAC is improved; and meanwhile, the positive secondary capacitance array, the positive main capacitance array, the negative secondary capacitance array and the negative main capacitance array realize the smaller capacitance through replacing the lowest capacitance in the DAC by unit capacitors in series, and the problem of oversize area due to improving the DAC precision is avoided. The improved 10-bit differential capacitance segmented coupling type DAC has good static property and takes up small area.

Owner:SOUTH CHINA UNIV OF TECH

Two-level switching method applied to successive approximation type analog-to-digital converter

PendingCN112332847AImprove energy efficiencyReduce Switching Power ConsumptionAnalogue/digital conversionElectric signal transmission systemsCapacitanceControl engineering

The invention discloses a two-level switching method applied to a successive approximation type analog-to-digital converter, which comprises the following steps of: comparing input signals VIP and VINfor N times to obtain an N-bit digital code, dividing the N-bit digital code into a sampling stage and a conversion stage, connecting the input signals VIP and VIN to top polar plates of an upper capacitor array and a lower capacitor array through a sampling switch in the sampling stage, and connecting each capacitor bottom polar plate to a corresponding voltage; in the conversion stage, enablingthe comparator to perform comparison from MSB bits to LSB bits on the voltages of the top polar plates of the upper and lower capacitor arrays to obtain corresponding digital codes so as to control the state of the bottom polar plate of each capacitor; and comparing for N times to obtain an N-bit digital code. The voltage change of + / -Vref is generated by switching for the first time, and the reference voltage Vref of the capacitor array is reduced to half of the reference voltage Vref of a common method; the introduced floating state is released within three-step conversion so as to simplifythe control logic; and only the LSB bit introduces a common mode level offset of 0.5 LSB. Compared with a traditional switching algorithm, the method has the advantages that the power consumption ofthe DAC is reduced by 99.51%, the capacitance area is saved by 75%, and the requirements on other modules of the ADC are not improved.

Owner:SOUTHEAST UNIV

Power-on reset circuit

ActiveUS7274227B2Reduce areaReduce capacitancePulse automatic controlElectronic switchingPower-on resetElectricity

A power-on reset circuit is provided. The power-on reset circuit includes an adjusting circuit, a charging / discharging unit and an output circuit. The adjusting circuit receives and adjusts a clock signal so as to output a control signal, wherein a minimum level of the control signal is clamped to be higher than a pre-defined level. The charging / discharging unit having a capacitor apparatus receives the control signal, determines whether to charge / discharge the capacitor apparatus based on the control signal, and outputs a storage voltage of the capacitor apparatus. The output circuit receives the storage voltage and outputs the reset signal. Wherein, the adjusting circuit determines the charging / discharging duty cycle of the charging / discharging unit by adjusting the waveform and the minimum level of the control signal. The output circuit enables / disables the reset signal according to whether the storage voltage reaches the threshold voltage of the output circuit.

Owner:XIAMEN XM PLUS TECH LTD

A Binary Capacitor Array and Its Low Power Switching Method Applied to Near Threshold SAR ADC

ActiveCN105553479BImprove performanceMitigate the deterioration of linearityAnalogue/digital conversionElectric signal transmission systemsCapacitancePower switching

The invention discloses a binary capacitor array applied to a near-threshold SARADC and a switching method with low power consumption thereof. By means of special construction of a core module thereof, namely a DAC capacitor array, the power consumption of the DAC part in the conversion process of the SARADC can be greatly reduced in combination with a provided new switching algorithm. Only two reference levels are adopted in the algorithm, such that the algorithm is applied to designing the SARADC under near-threshold voltage. Compared with the area of the capacitor array required by the ordinary two-level capacitor switching technology, by means of flexible application of united, split and floating capacitor switching technologies, the total area of the capacitor array is reduced by 50%.

Owner:SOUTHEAST UNIV

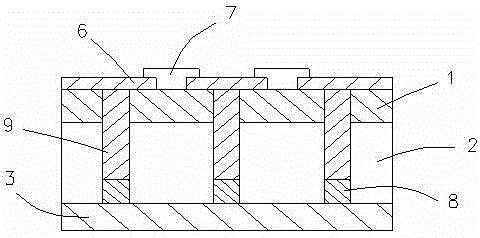

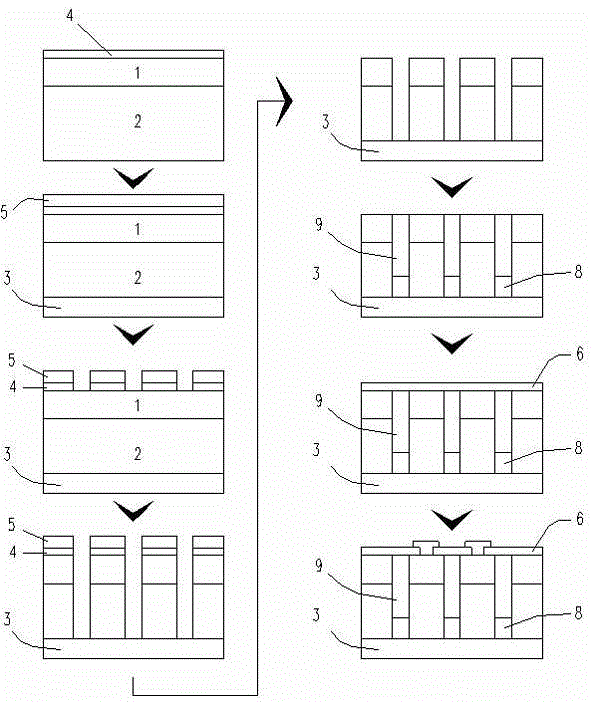

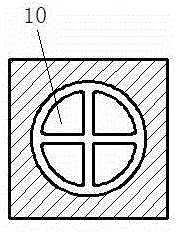

Deep trench isolated anti-crosstalk photoelectric detector and manufacturing method thereof

ActiveCN104900666AQuick responseReduce leakage currentSemiconductor/solid-state device manufacturingRadiation controlled devicesCapacitanceRC time constant

The invention discloses a deep trench isolated anti-crosstalk photoelectric detector, comprising a P-i-N laminar structure formed by sequentially laminating a P-type diffusion layer, a substrate layer and an N-type diffusion layer, wherein an isolation region is formed on the P-i-N laminar structure and divides the photo-surface of the P-i-N laminar structure into a plurality of quadrants. The photoelectric detector is characterized in that the isolation region is realized by adopting the following structure: a deep trench is made in the photo-surface of the P-i-N laminar structure, the cross section contour of the deep trench is matched with the outer contours of the plurality of quadrants, the axial direction of the deep trench is the same as the laminating direction of the P-i-N laminar structure, the depth of the deep trench reaches the upper end surface of the N-type diffusion layer, and the deep trench is filled with an insulating material. The photoelectric detector has the advantages: each quadrant of the quadrant photoelectric detector is effectively isolated, the area of the depletion layer of the photoelectric detector is reduced, the internal junction capacitance area is reduced, the RC time constant is reduced, and the response speed of a device is improved; and the deep trench is positioned in the body of the quadrant photoelectric detector, so that the influence of surface defects on the device is avoided.

Owner:CHONGQING EAGLE VALLEY OPTOELECTRONICS

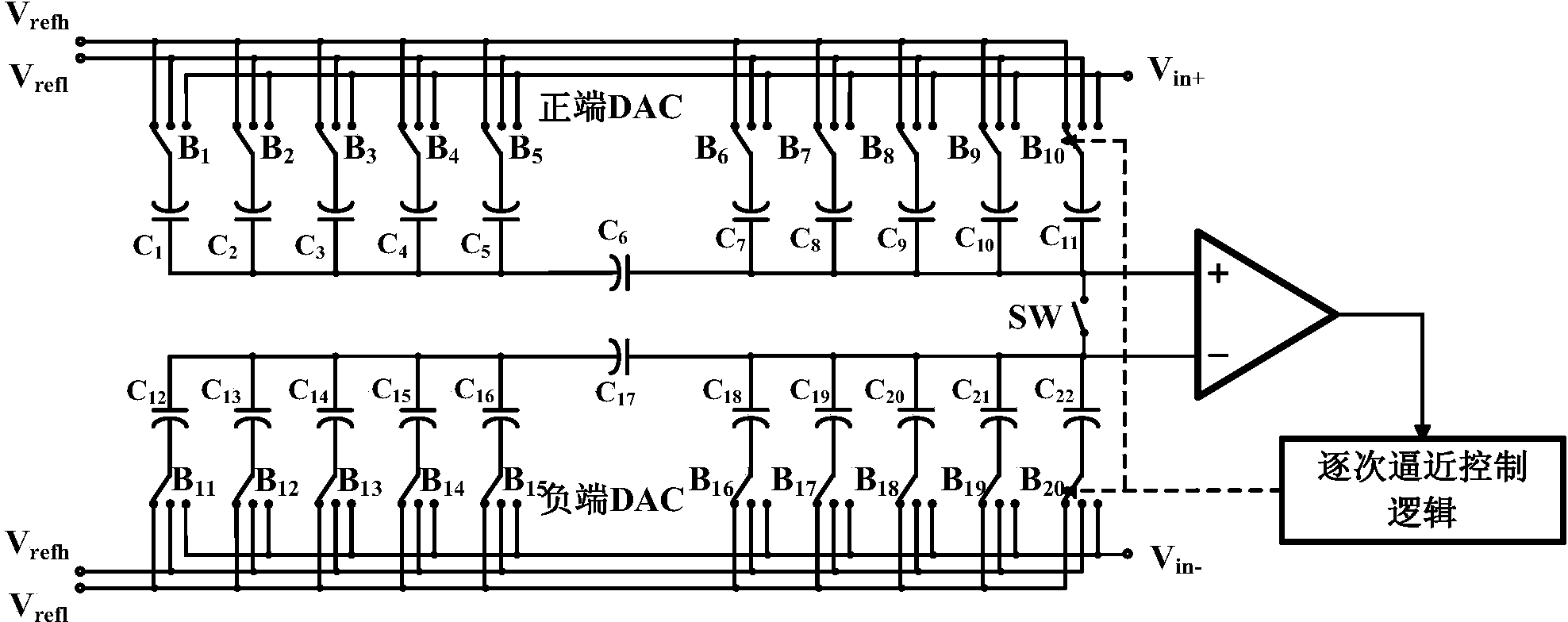

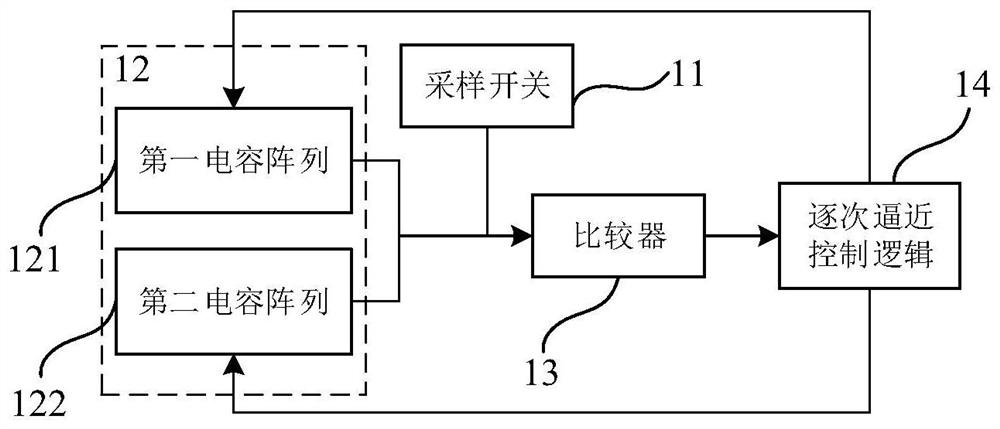

Successive approximation type analog-to-digital converter based on segmented differential capacitor array

PendingCN113612480ACapacitor area is smallReduce power consumptionAnalogue/digital conversionElectric signal transmission systemsCapacitanceA d converter

The invention discloses a successive approximation type analog-to-digital converter based on a segmented differential capacitor array. The successive approximation type analog-to-digital converter comprises: a sampling switch; a sectional type differential capacitor array which is electrically connected with the sampling switch; a comparator which is electrically connected with the sectional type differential capacitor array; and a successive approximation control logic which is electrically connected with the sectional type differential capacitor array and the comparator. The sectional type differential capacitor array comprises a first capacitor array and a second capacitor array which are symmetrically arranged, an upper pole plate of the first capacitor array is connected with a positive input end of the comparator, and an upper pole plate of the second capacitor array is connected with a negative input end of the comparator; lower polar plates of the first capacitor array and the second capacitor array are selectively and electrically connected to a reference voltage end through a control switch; and each of the first capacitor array and the second capacitor array comprises two sub-capacitor arrays which are connected through a unit bridging capacitor. According to the successive approximation type analog-to-digital converter provided by the invention, the capacitance area is saved, the power consumption is reduced, and the quantization speed is improved.

Owner:XIDIAN UNIV

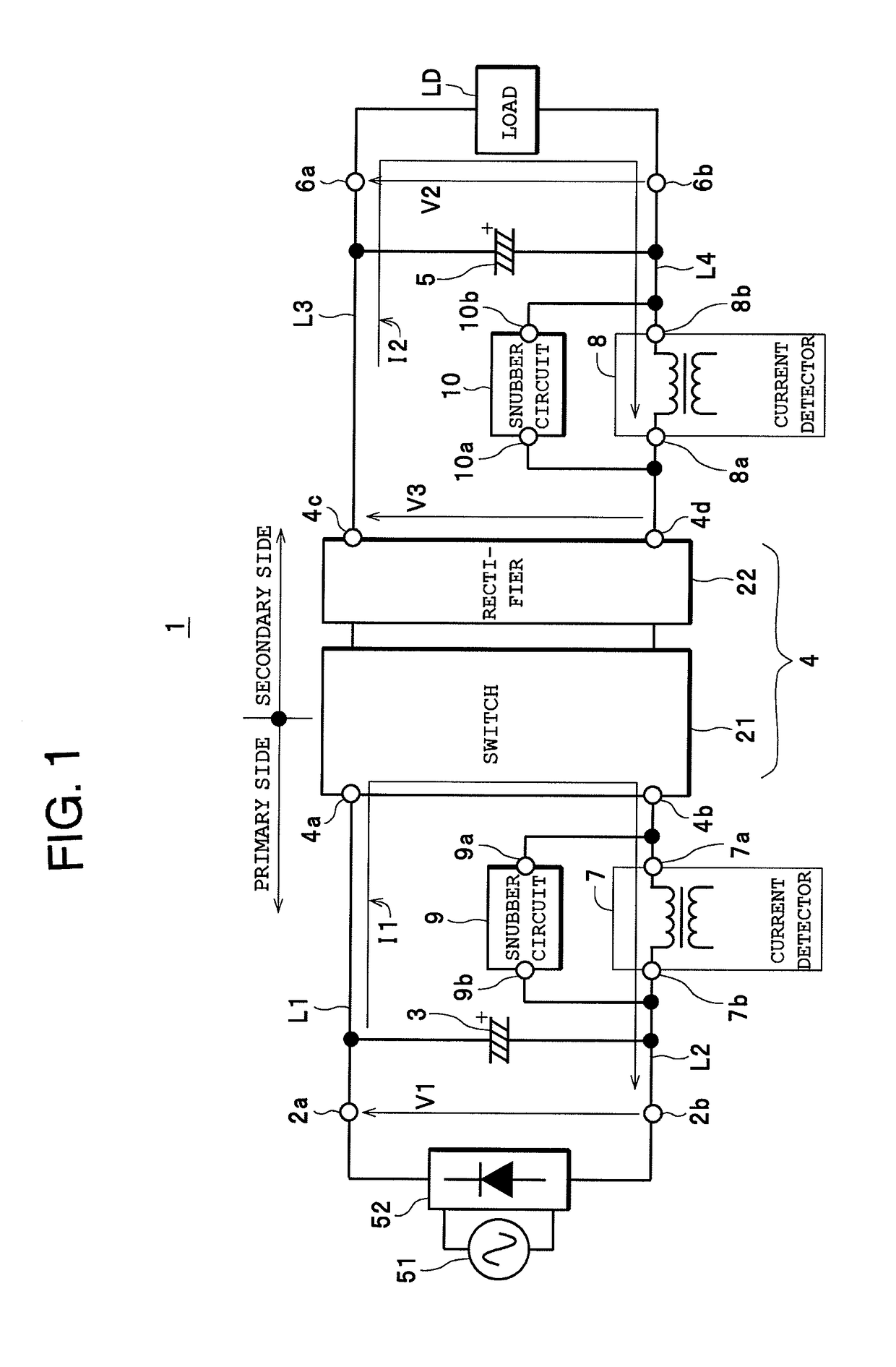

Electronic device

ActiveUS20190020265A1Increase capacitanceIncrease capacitor areaEfficient power electronics conversionApparatus with intermediate ac conversionSnubberEngineering

An electronic device includes a power converter and a current detector that is disposed at at least one position out of a primary-side position and a secondary-side position for the power converter and detects a current flowing at the at least one position. A snubber circuit including a capacitor is directly connected in parallel to both ends of the current detector.

Owner:TDK CORPARATION

An Improved 10‑bit Differential Capacitive Segment-Coupled DAC

ActiveCN104038223BHigh precisionReduce areaAnalogue/digital conversion calibration/testingCapacitanceCoupling

The invention discloses an improved 10-bit differential capacitance segmented coupling type DAC. The improved 10-bit differential capacitance segmented coupling type DAC comprises a positive secondary capacitance array, a positive coupling capacitor, a positive main capacitance array, a negative coupling capacitor, a negative main capacitance array and a sampling switch. The improved 10-bit differential capacitance segmented coupling type DAC uses a 12-bit differential DAC to realize the 10-bit differential DAC, the gain error of a 1-LSB is avoided, and the static property of the DAC is improved; and meanwhile, the positive secondary capacitance array, the positive main capacitance array, the negative secondary capacitance array and the negative main capacitance array realize the smaller capacitance through replacing the lowest capacitance in the DAC by unit capacitors in series, and the problem of oversize area due to improving the DAC precision is avoided. The improved 10-bit differential capacitance segmented coupling type DAC has good static property and takes up small area.

Owner:SOUTH CHINA UNIV OF TECH

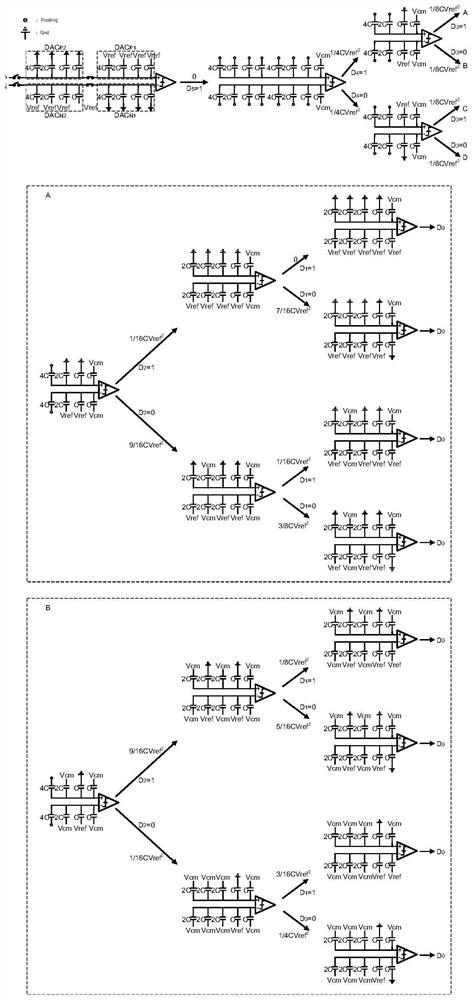

A low-power-consumption switching algorithm applied to an SAR ADC

ActiveCN109936370AReduce power consumptionLow misalignmentAnalogue/digital conversionElectric signal transmission systemsCapacitanceVoltage reference

The invention discloses a low-power-consumption switching algorithm applied to an SAR ADC, an adopted DAC capacitor array is divided into a positive-end capacitor array and a negative-end capacitor array, the positive end and the negative end of the positive-end capacitor array are equal, and each capacitor array comprises N-2 capacitors conforming to a binary relation and a dummy capacitor. All the capacitors have no split structure, and each capacitor is connected with a reference voltage or a GND or a common-mode voltage; when the highest-order capacitor is in the reference level reset state, a pole plate is connected with GND, and when the rest capacitors are in the reference level reset state, the pole plates are connected with reference voltage; for an input signal, a digital code isobtained after conversion of an N-bit SAR ADC. An extra complex structure does not need to be introduced, meanwhile, the offset of the comparator is reduced, and the capacitance area is saved.

Owner:SOUTHEAST UNIV

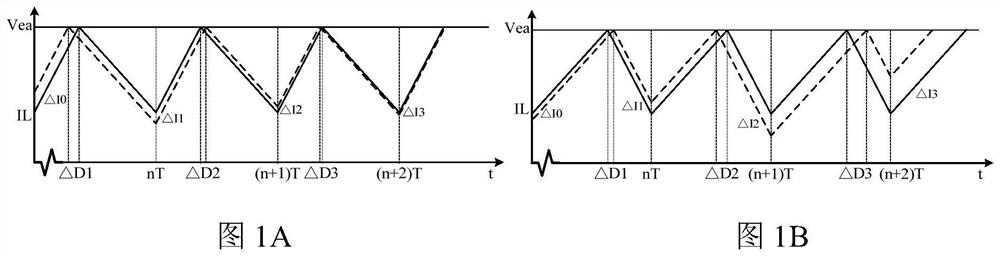

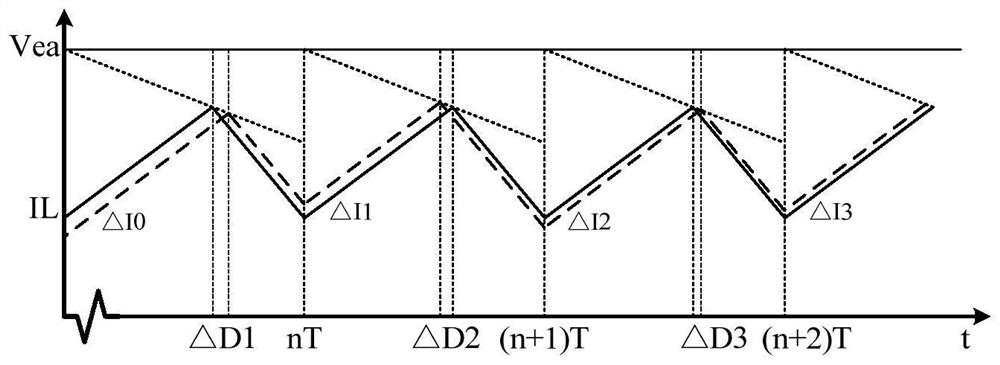

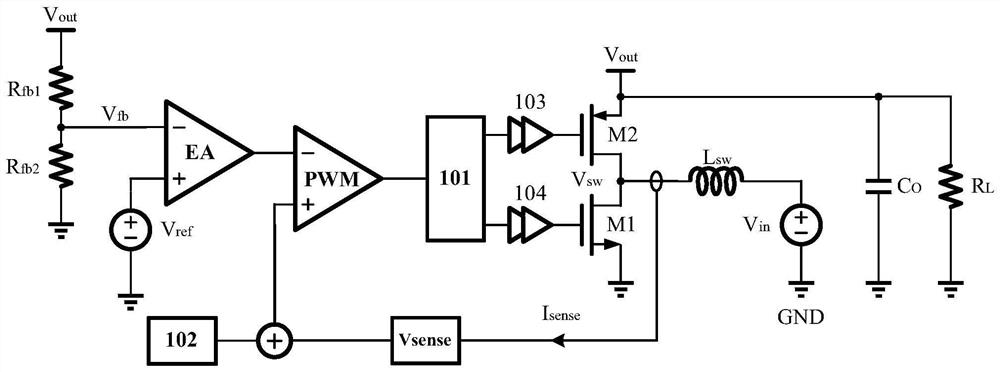

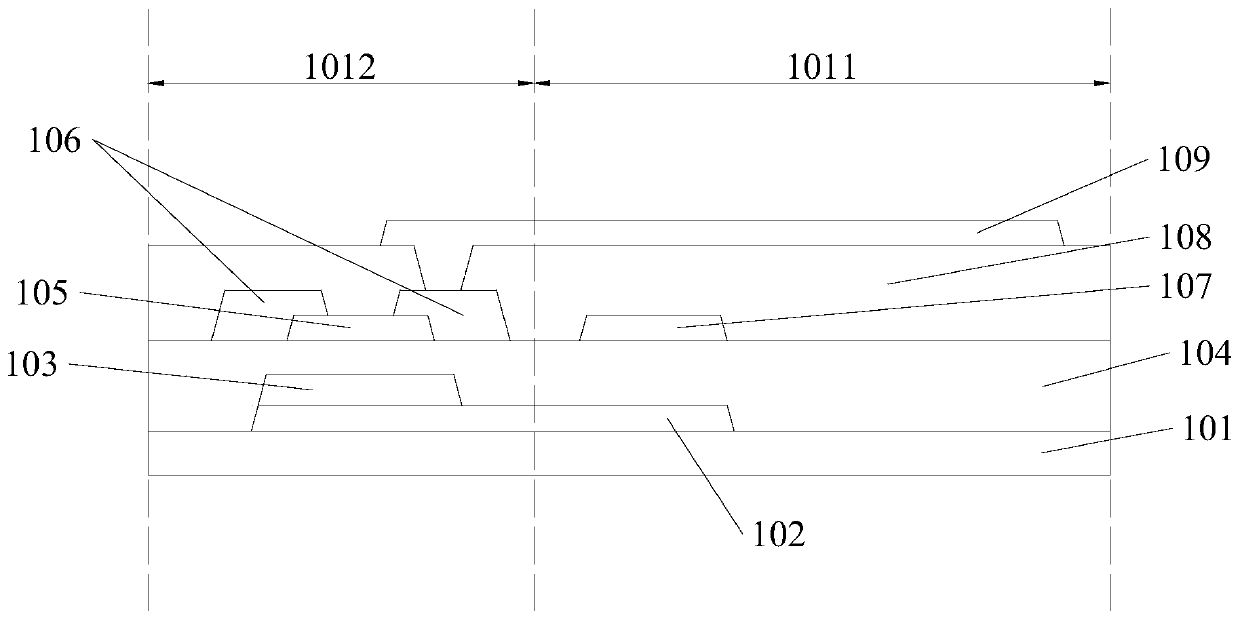

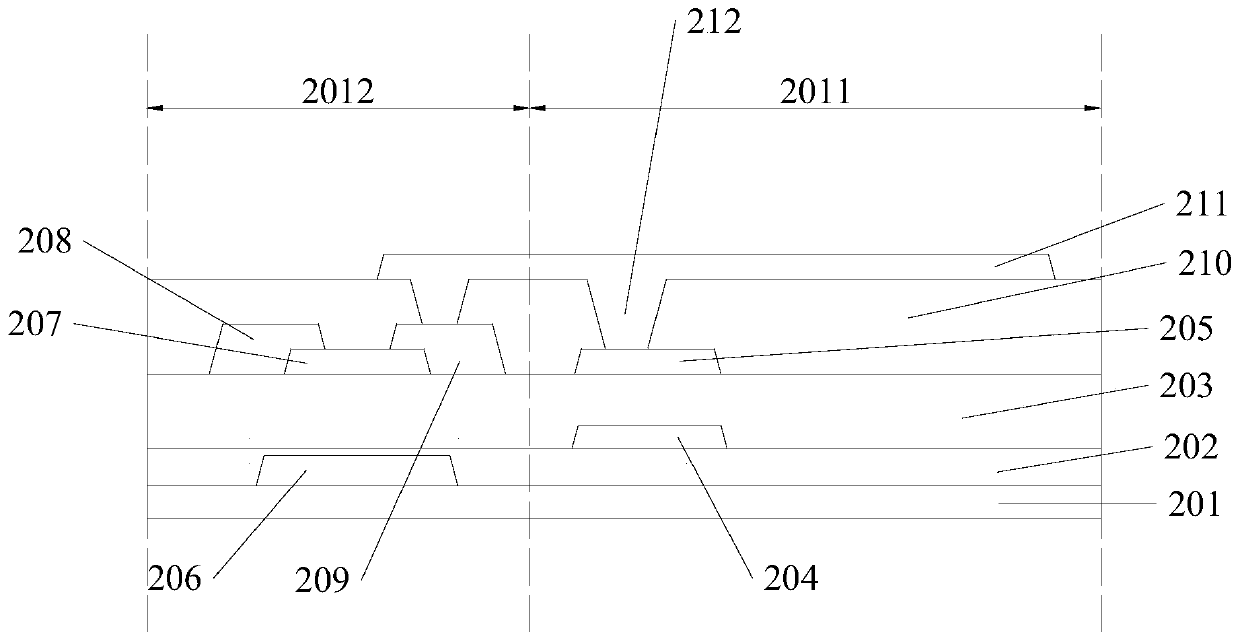

Self-adaptive slope compensation BOOST circuit

PendingCN114552987AIncrease profitOscillation suppressionEfficient power electronics conversionDc-dc conversionHemt circuitsVoltage range

The invention relates to a self-adaptive slope compensation BOOST circuit, which comprises a basic BOOST circuit and a self-adaptive slope compensation circuit, the basic BOOST circuit is set to receive an input voltage Vin and provide an output voltage Vout, and the self-adaptive slope compensation circuit comprises a differential circuit and a slope generation circuit, the differential circuit is configured to generate a differential current whose current magnitude is proportional to a difference between the output voltage Vout and the input voltage Vin, and the ramp generation circuit is configured to generate a sawtooth voltage whose slope is proportional to the difference between the output voltage Vout and the input voltage Vin. According to the self-adaptive slope compensation BOOST circuit, the differential circuit and the slope generation circuit are used for generating a compensation slope voltage signal which is related to input and output voltage and changes along with the duty ratio, the structure is simple, implementation is easy, and the compensation performance is good in a wide output voltage range.

Owner:SHANGHAI ORIENT CHIP TECH CO LTD

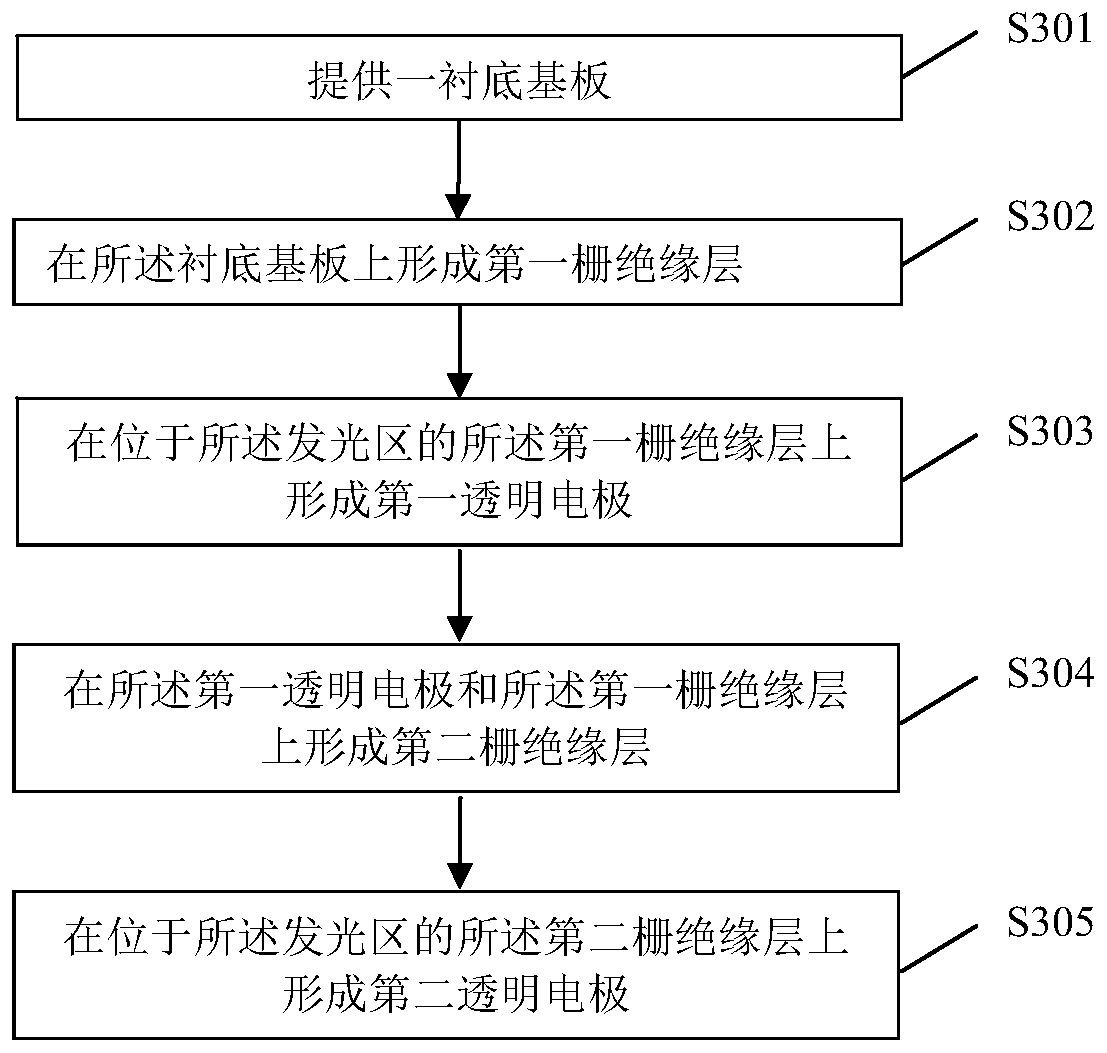

Array substrate, manufacturing method thereof and display panel

InactiveCN110707101AImprove yieldIncrease capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingImage resolutionEngineering

The invention provides an array substrate, a manufacturing method thereof and a display panel. The array substrate comprises a light-emitting area and a non-light-emitting area, and the array substrate comprises a substrate base plate; gate insulating layers which comprise a first gate insulating layer and a second gate insulating layer which are sequentially arranged on the substrate base plate;a storage capacitor which is located in the light-emitting area and comprises a first transparent electrode and a second transparent electrode, wherein the first transparent electrode is arranged between the first gate insulating layer and the second gate insulating layer, and the second transparent electrode is arranged on the second gate insulating layer and is opposite to the first transparentelectrode in position. According to the array substrate, the yield of products is increased, and the aperture opening ratio of pixels is increased. According to the display panel, the aperture openingratio of the pixels is large, and the resolution ratio during display is high.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

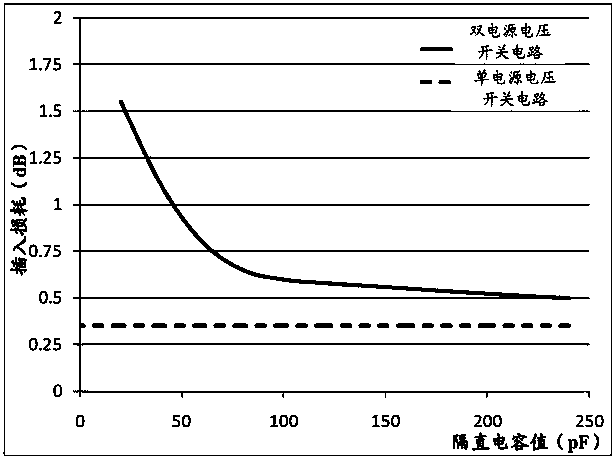

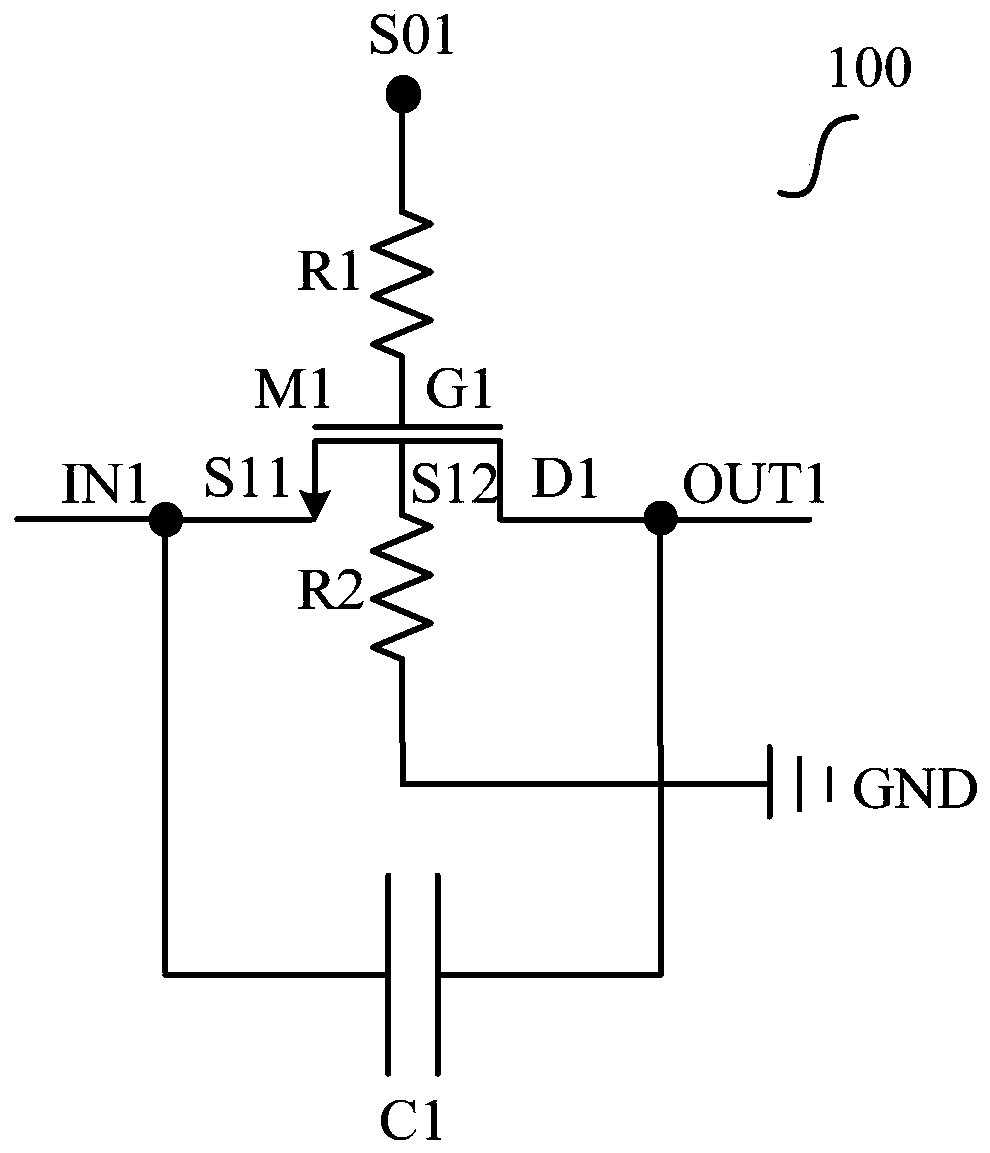

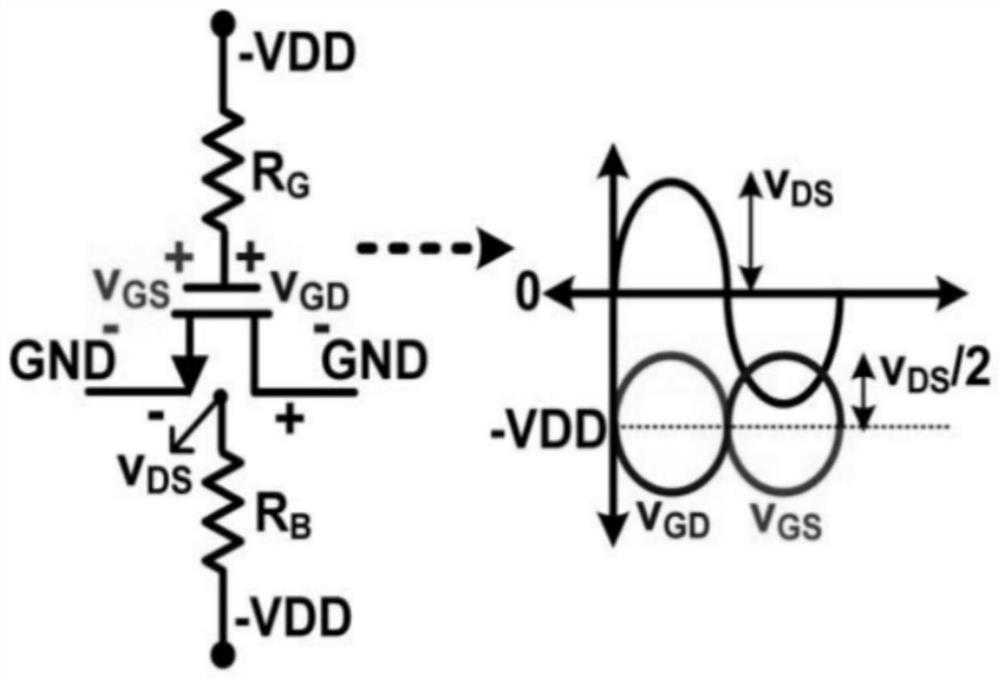

A DC blocking circuit and a switching circuit

The invention relates to a direct current blocking circuit and a switching circuit; the direct current blocking circuit is used for blocking a direct current bias; the direct current blocking circuit comprises a first MOS (Metal Oxide Semiconductor) tube, a first resistor, a second resistor and a first capacitor, wherein the first MOS tube, the first resistor and the second resistor are in serial connection; the first capacitor is in parallel connection with the first MOS tube; the grid electrode of the first MOS tube is coupled to the first end of the first resistor, the source electrode of the first MOS tube is coupled to the input end of the direct current blocking circuit and the first end of the first capacitor, and the drain electrode of the first MOS tube and the second end of the first capacitor are coupled to the output end of the direct current blocking circuit; the first end of the second resistor is coupled to the substrate end of the first MOS tube, and the second end of the second resistor is grounded; the second end of the first resistor is coupled to a first control signal; and when the first control signal is a power signal, the first MOS tube is in a conducting state. According to the direct current blocking circuit and the switching circuit disclosed by the invention, on the basis of keeping no degradation of the high-power linearity and the simple structure, the circuit area is decreased, and the degradation degree of insertion loss is reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Conversion circuit, heartbeat current signal conversion device and method, and heartbeat detection system

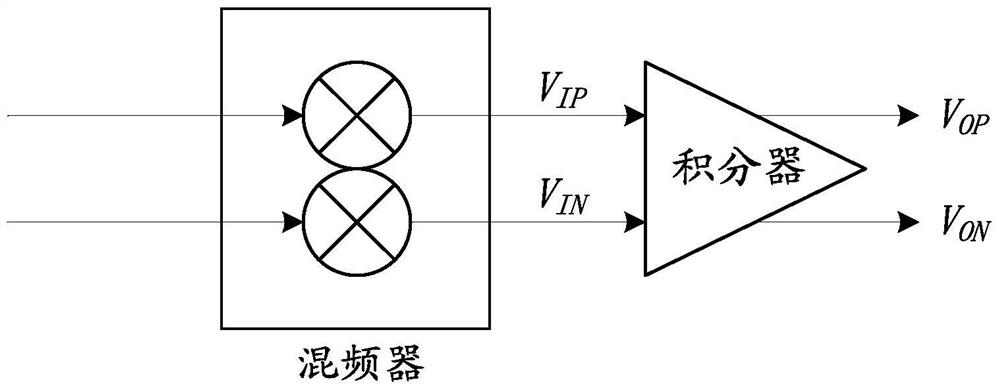

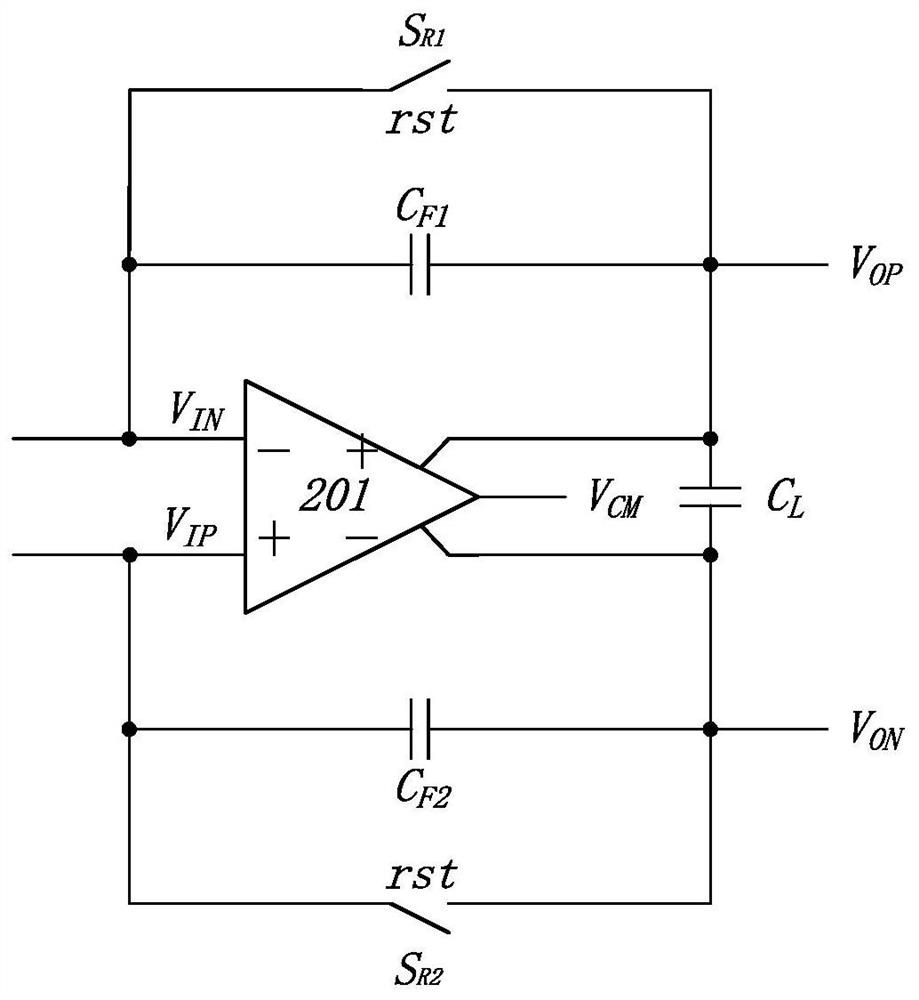

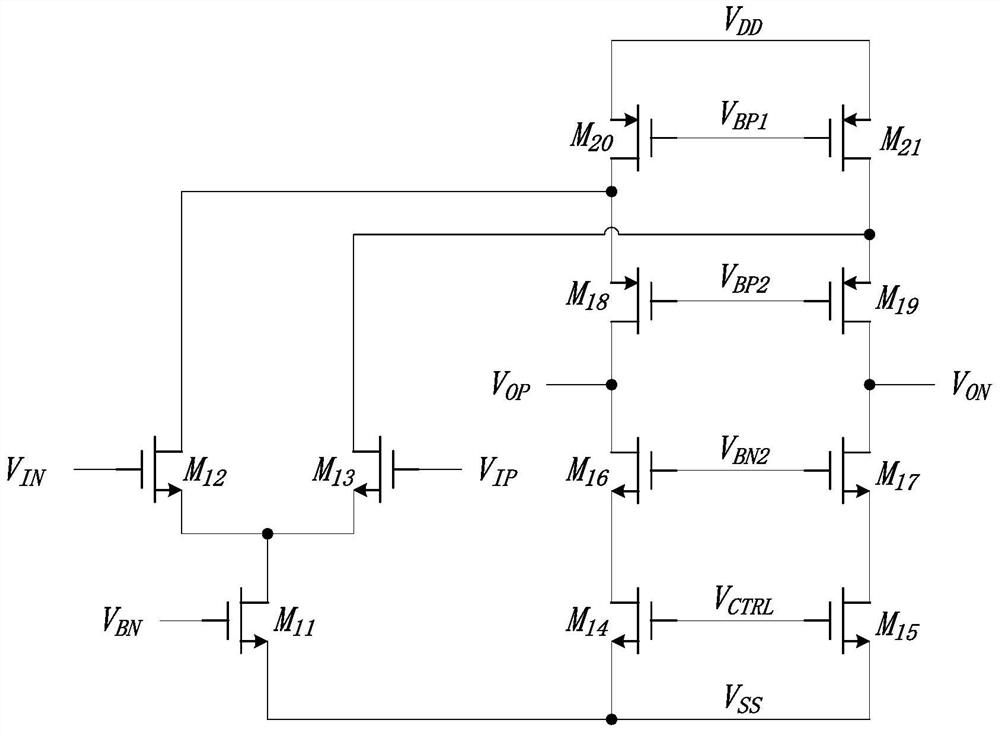

ActiveCN107294497BLow costSimplify the linkMeasuring/recording heart/pulse rateMulti-frequency-changing modulation transferenceIntegratorFrequency mixer

A heartbeat current signal conversion device, comprising a converter for converting a modulated optical signal into a current signal and transmitting same; a mixer for performing frequency conversion of a heartbeat current signal and a background photocurrent signal in the current signal, and then transmitting the modulated photocurrent signal, the frequency-converted heartbeat current signal and the frequency-converted background photocurrent signal in the current signal; a fully differential integrator for performing both positive integration and inverse integration on the modulated photocurrent signal, the frequency-converted heartbeat current signal and the frequency-converted background photocurrent signal, which are inputted, and then outputting a voltage signal. The fully differential integrator can improve the suppression of the heartbeat current signal conversion device to the common mode noise, and the linearity and the dynamic output range of the circuit. Moreover, the heartbeat current signal conversion device loop always forms a closed loop, and thus a direct output to the next-stage circuit can be achieved, eliminating an output buffer circuit, thereby reducing power consumption.

Owner:SHENZHEN GOODIX TECH CO LTD

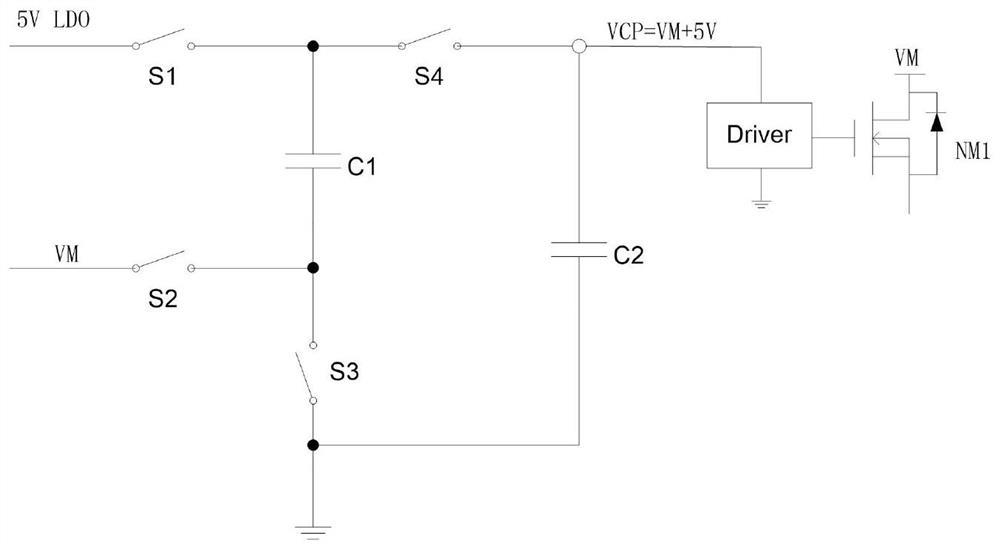

Drive control circuit, control method and charge pump circuit

PendingCN112821752AReduce areaReduce power consumptionApparatus without intermediate ac conversionCapacitanceControl theory

The invention discloses a drive control circuit, a control method and a charge pump circuit. The drive control circuit is used for driving a switching tube, comprises a first capacitor and can be coupled with a first power supply and a second power supply. When the driving control circuit is in a first working state, the driving control circuit controls the first capacitor to be coupled with the first power supply and controls the first power supply to charge the first capacitor; when the driving control circuit is in a second working state, the driving control circuit controls the switching tube to be coupled with the second power supply and controls the second power supply to supply power to the switching tube; and when the driving control circuit is in a third working state, the driving control circuit controls the first capacitor to be coupled with the control end of the switching tube and controls the first capacitor to supply power to the switching tube. According to the drive control circuit, the control method and the charge pump circuit, the circuit energy consumption can be reduced, and the circuit efficiency can be improved.

Owner:XIAMEN KIWI MICROELECTRONICS TECH CO LTD

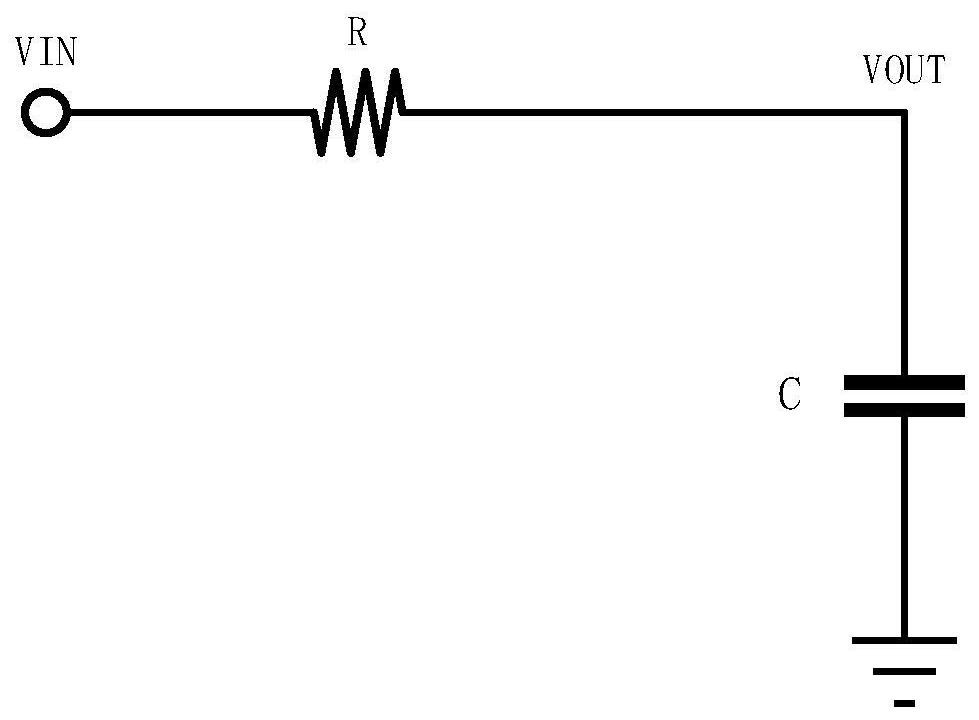

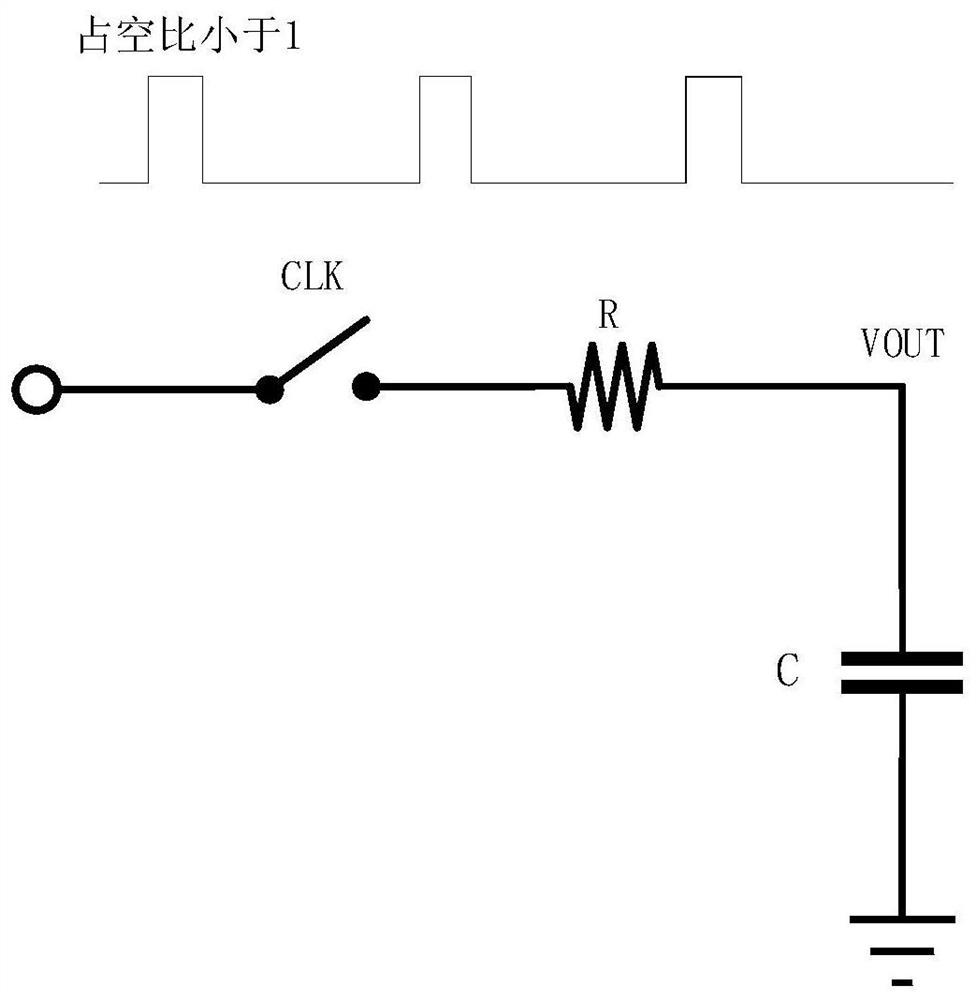

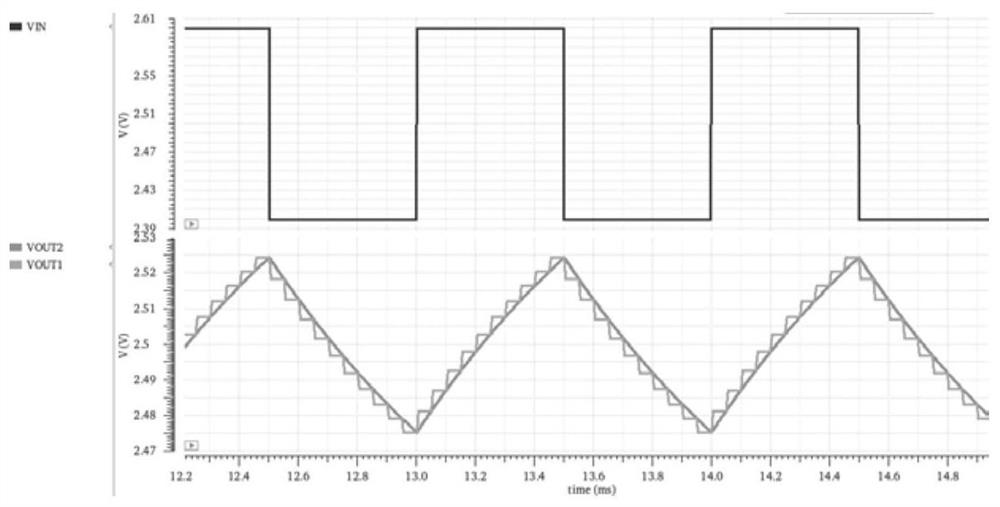

Low-pass filter for sampling at small duty ratio

PendingCN113489472ALow costCapacitor area is smallFrequency selective two-port networksCapacitanceLow-pass filter

The invention belongs to the technical field of analog circuits, and particularly relates to a low-pass filter for small-duty-ratio sampling. The filter comprises a capacitor and a resistor, and further comprises a sampling switch; the starting end of the sampling switch is connected with an input end, the other end of the sampling switch is grounded after passing through the resistor and the capacitor in sequence, and the connecting point of the resistor and the capacitor is an output end; and the duty ratio of the sampling switch is less than 1. The invention has the beneficial effects that the capacitance area can be greatly reduced, and the chip cost is saved.

Owner:SOUTHCHIP SEMICON TECH SHANGHAI CO LTD

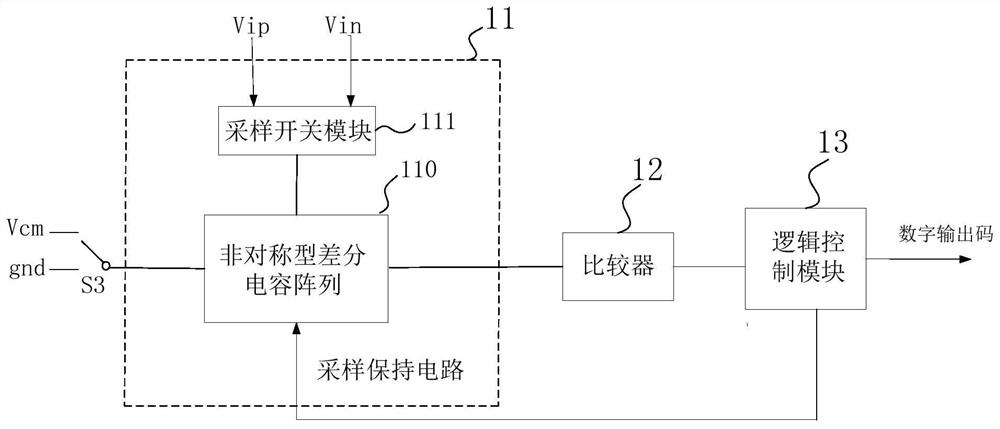

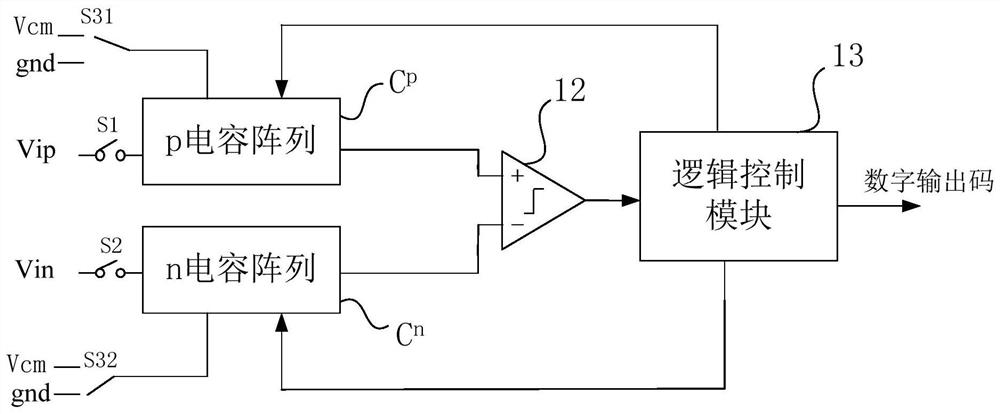

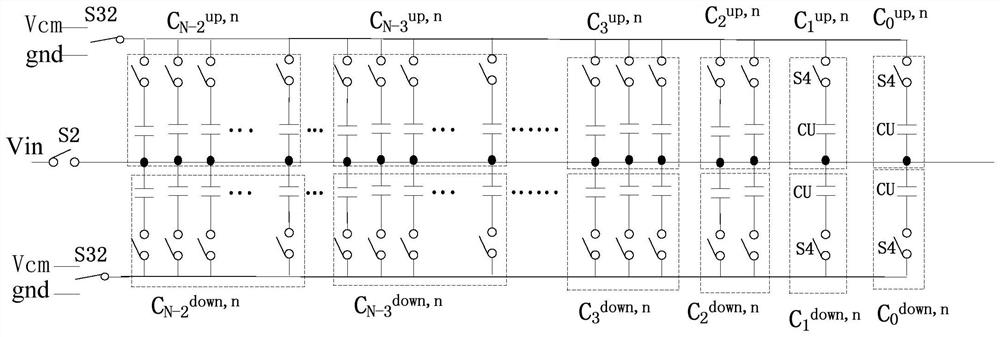

Successive Approximation Analog-to-Digital Converter Based on Asymmetric Differential Capacitor Array

ActiveCN107888190BSave extra spaceSwitching power consumptionPower saving provisionsElectric signal transmission systemsCapacitanceSoftware engineering

The invention relates to a successive approximation register analog-to-digital converter based on an asymmetric differential capacitor array. The successive approximation register analog-to-digital converter comprises a sample hold circuit, a comparer and a logic control module. The sample hold circuit comprises an asymmetric differential capacitor array and a sample switch module. According to the asymmetric differential capacitor array, a first input end is selectively electrically connected with a common-mode voltage end and a grounding terminal through a single pole double throw switch, asecond input end is electrically connected with an output end of the sample switch module, a third input end is electrically connected with a first output end of the logic control module, and the output end is electrically connected with the comparer. The first input end and the second input end of the sample switch module are electrically connected with an analog signal negative input end and ananalog signal positive input end. The output end of the comparer is electrically connected with the input end of the logic control module. According to the successive approximation register analog-to-digital converter provided by the invention, the power consumption can be effectively reduced, a capacitor area can be reduced, and the design difficulty can be reduced.

Owner:XIDIAN UNIV

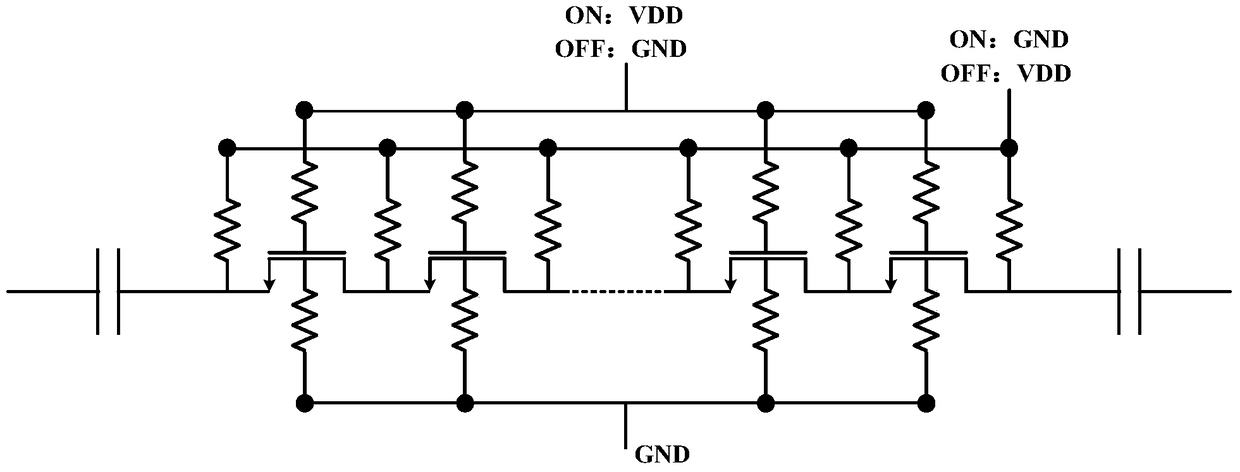

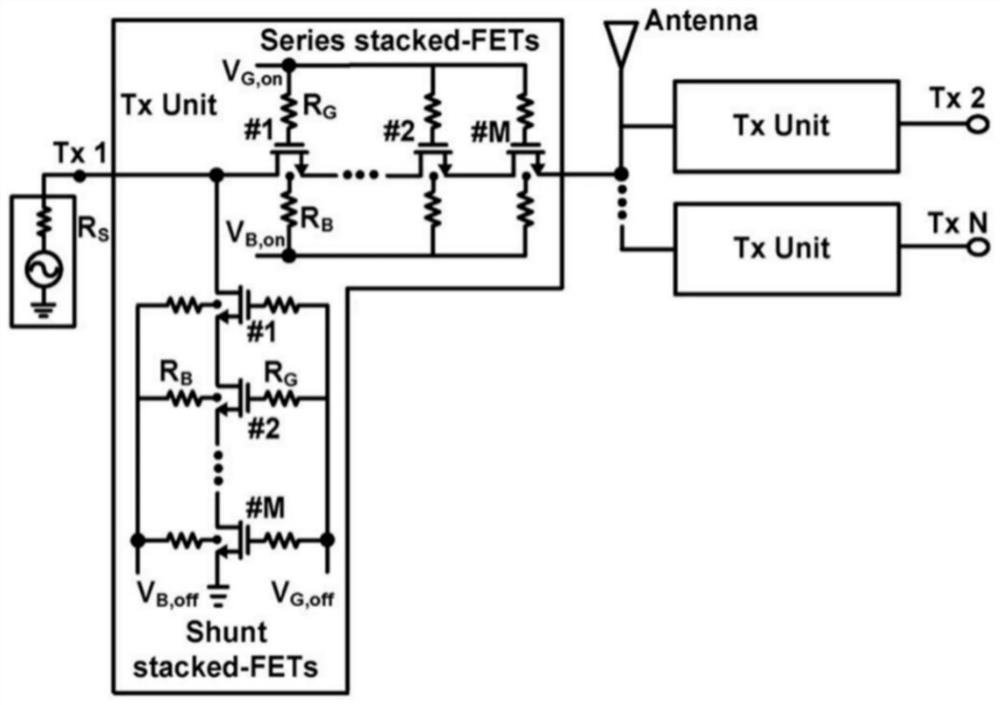

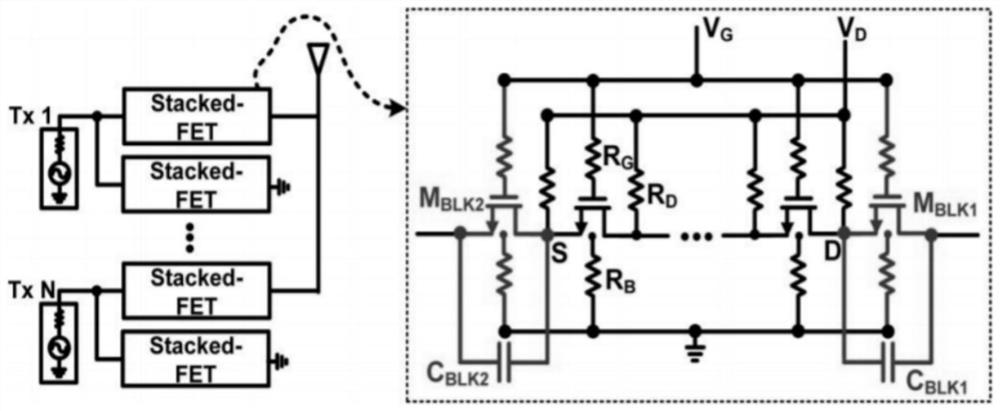

An Ultra-Low Power Biased RF Switch

ActiveCN109088626BReduce areaLow costElectronic switchingHigh level techniquesCapacitanceHemt circuits

The present invention proposes a new radio frequency switch structure: each radio frequency switch includes a series branch and a parallel branch, the series branches through different radio frequency switches share an AC coupling capacitor, the parallel branch and the parallel branch in the same radio frequency switch The series branch shares an AC coupling capacitor, removes the blocking transistor and the AC coupling capacitor close to the ground in the parallel branch of the same radio frequency switch, does not need any negative voltage generating circuit, and can save more than 60% of the capacitor area compared with the traditional structure. The invention greatly reduces the area and cost of the chip while keeping the performance unchanged.

Owner:安徽矽磊电子科技有限公司

Programmable gain amplifier

InactiveCN100555873CReduce areaCapacitor area is smallAnalogue-digital convertersCapacitanceAudio power amplifier

A programmable gain amplifier includes an operational amplifier, N attenuation capacitors, N+1 sets of adjustment capacitor modules, multiple switching switches, a switching control module, and a feedback switch, where N is an integer greater than 0. Each group of adjustment capacitor modules has at least one adjustment capacitor. Each switching switch is controlled by the switching control module, and its switch common end is respectively connected to the second end of the adjustment capacitor, so as to connect the connected adjustment capacitor to an input signal, a reference voltage, or the output end of the operational amplifier. The feedback switch is connected between the output end of the operational amplifier and the first input end, is turned on during a first phase period, and is turned off during other periods. The adjustment capacitor can be connected to the output terminal of the operational amplifier as a feedback capacitor through the control of the switching switch in a second phase, and the first phase and the second phase do not overlap.

Owner:SUNPLUS TECH CO LTD

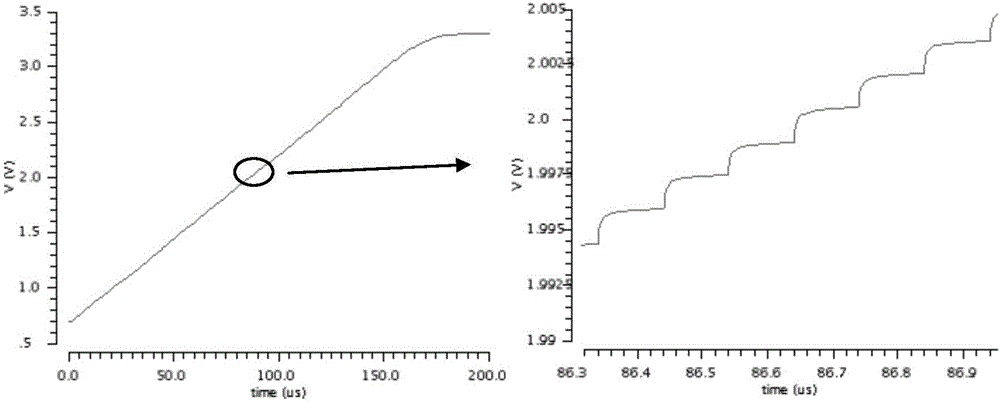

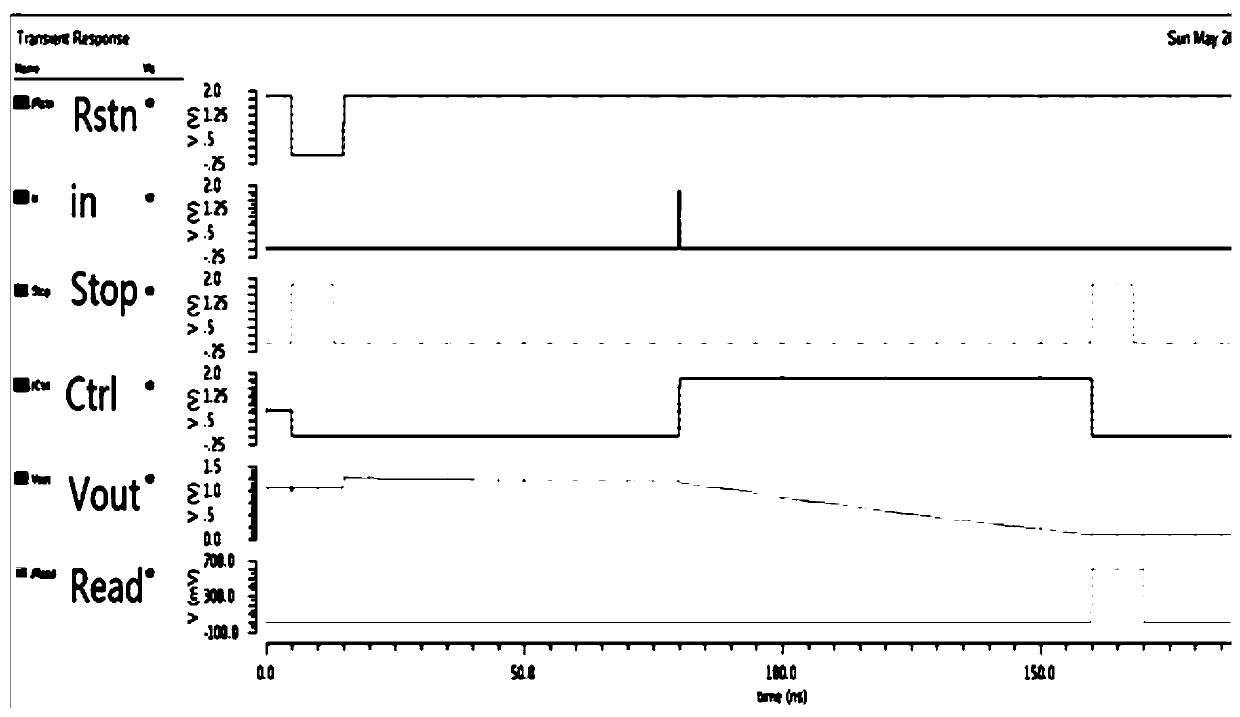

A Compact Time-to-Analog Conversion Circuit for Single Photon Detectors

The invention discloses a compact type time to analog conversion circuit applied to a single-photon detector. The compact type time to analog conversion circuit applied to the single-photon detector comprises an RS trigger, a timing capacitor C and eight MOS transistors, wherein the MP0 and the MP1 form a differential structure as an input stage; the MN1 and the MP1 form a complementary CMOS switch; the three MOS transistors including the MP0, the MN1 and the MP1 form a control logic together, so that discharging of the timing capacitor C is controlled; the MP2 and the MP3 are used as two PMOSswitches used for controlling the reset operation of the timing capacitor C; and the MN2 and the MN3 form a source-level follower used for reading voltage on the timing capacitor C. The compact typetime to analog conversion circuit applied to the single-photon detector in the invention is small in capacitance area, small in transistor number and simple in structure; the effect of greatly reducing the area of a circuit layout is achieved; the circuit density and integrity are improved; fill factors of picture elements are effectively increased; simultaneously, the overall power consumption ofthe circuit is also reduced; the manufacture cost is low; the performance consistence of various circuits is good; and the yield is high.

Owner:NANJING UNIV OF POSTS & TELECOMM