Analog-to-digital converter and three-level switching method applied to SAR ADC

A technology of analog-to-digital converter and sampling switch, which is applied in the direction of analog-to-digital conversion, code conversion, instruments, etc., and can solve the problems of unsatisfactory capacitor area reduction and low switching power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] Embodiments of the present invention will be described below in conjunction with the accompanying drawings.

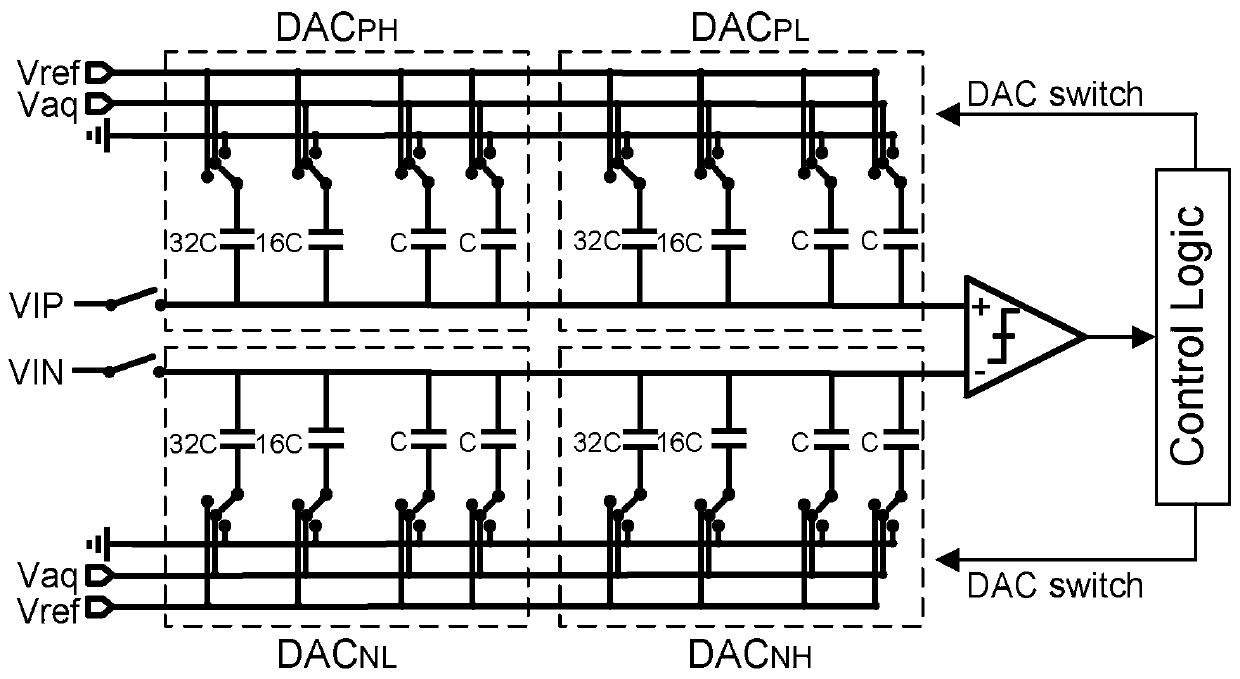

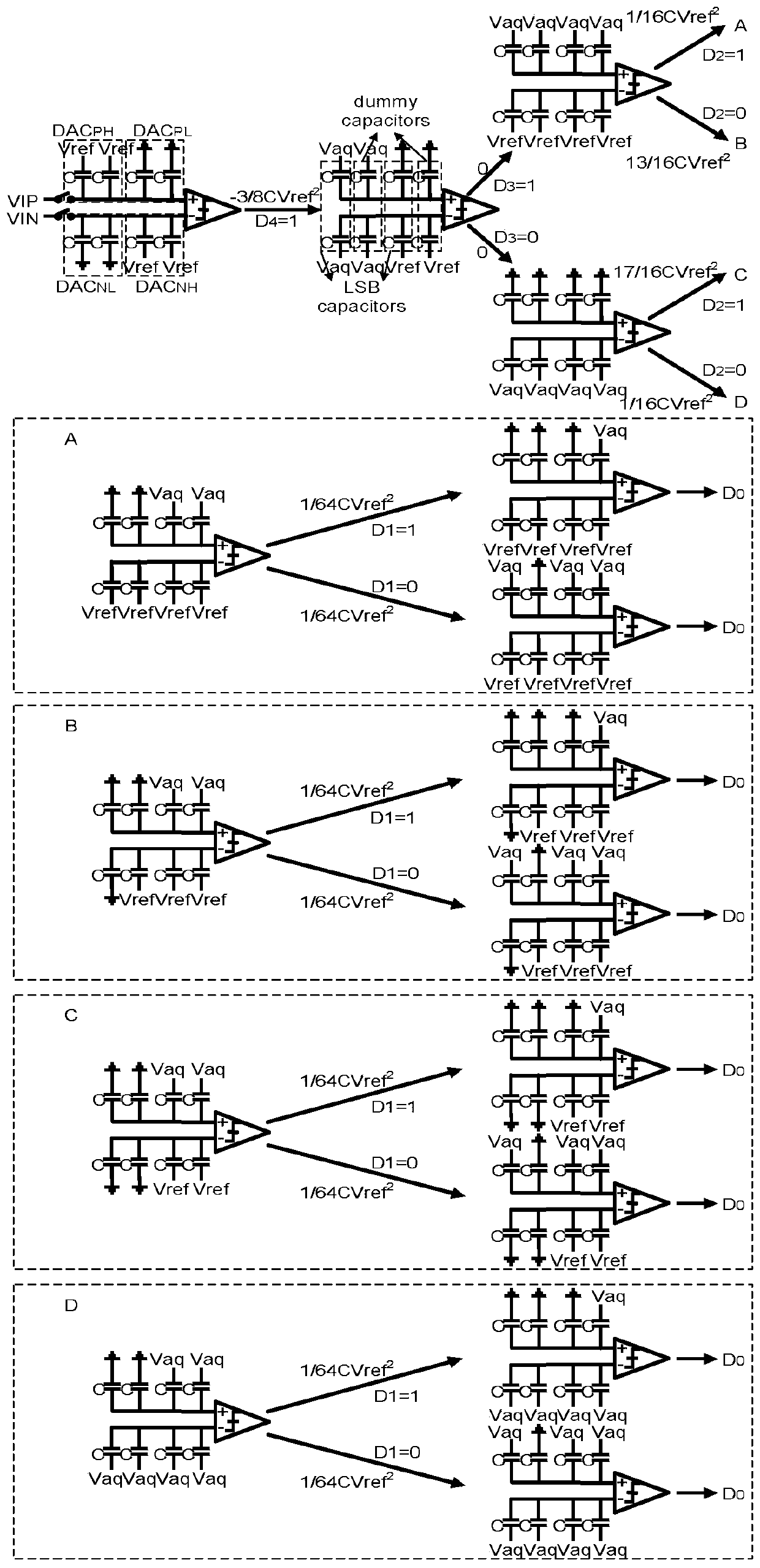

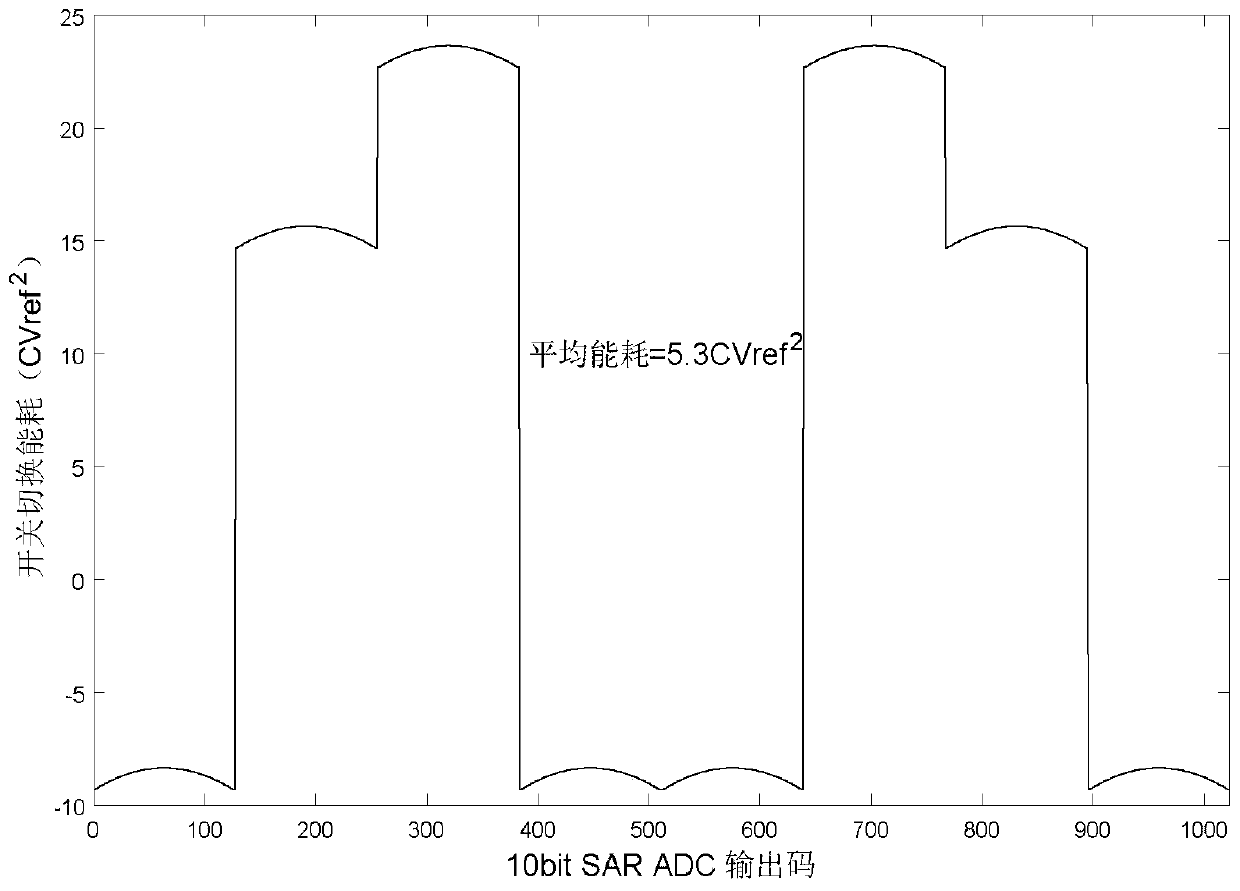

[0046] The present invention has designed a kind of three-level switch method that is applied to SAR ADC, and the structure of 10 SAR ADC based on this method is as follows figure 1 shown, including sampling switches, capacitor arrays, comparators, and digital control logic. Among them, the capacitor array includes the same upper capacitor array and lower capacitor array; the input signal VIP is connected to the top plate of the upper capacitor array through the sampling switch, and the input signal VIN is connected to the top plate of the lower capacitor array through the sampling switch; the upper capacitor The top plate of the array is connected to the non-inverting input of the comparator, and the top plate of the lower capacitor array is connected to the inverting input of the comparator; the differential output of the comparator generates a control signal ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More