VDMOS device with total dose irradiation resistance and manufacturing method thereof

A technology of anti-total dose and production method, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of inability to manufacture VDMOS devices, increase the thickness of gate oxide layer, etc., and achieve improved resistance to single event gate wear ability, high dielectric constant, and the effect of reducing transition accumulation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

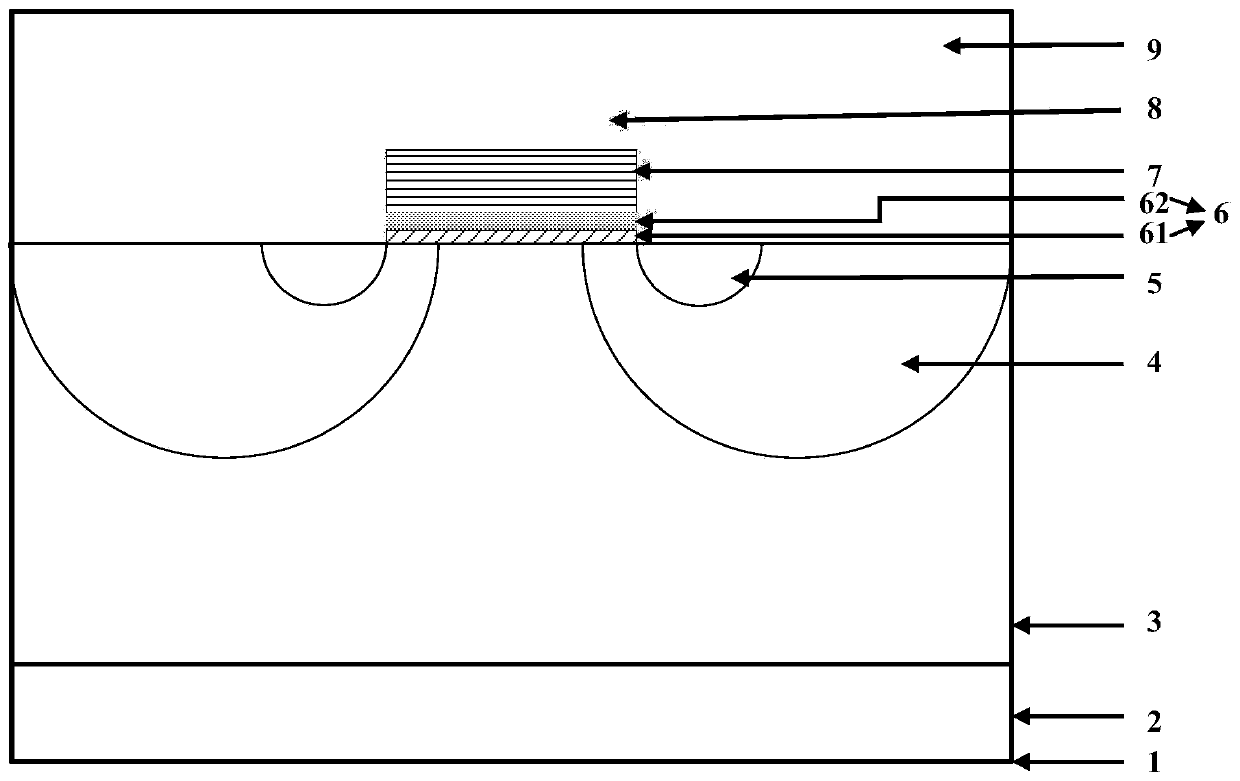

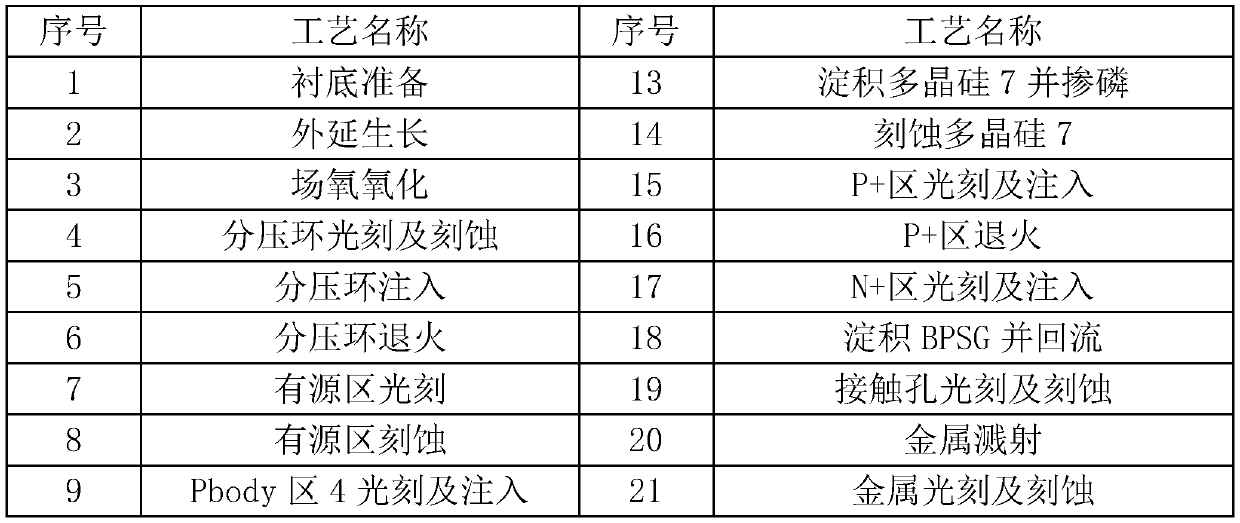

[0026] Embodiments of the present invention are described in detail below, wherein the same or similar reference numerals represent the same or similar elements or elements with similar functions. The embodiments described below by referring to the figures are exemplary, and are only used to explain the present invention and not to limit the present invention.

[0027] Those skilled in the art can understand that, unless otherwise defined, all terms (including technical terms and scientific terms) used herein have the same meaning as commonly understood by those of ordinary skill in the art to which this invention belongs. It should also be understood that terms such as those defined in commonly used dictionaries should be understood to have a meaning consistent with the meaning in the context of the prior art, and unless defined as herein, will not be used in an idealized or overly formal meaning to explain.

[0028] The present invention will be further described below in c...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More