Method for improving total dose irradiation resistance of FinFET device

A technology with anti-total dose and radiation performance, applied in the fields of semiconductor devices, electric solid-state devices, semiconductor/solid-state device components, etc., can solve the problems of threshold voltage drift, increase of off-state leakage current, etc., to reduce the impact and cost. The effect of improving and improving the anti-total dose radiation performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

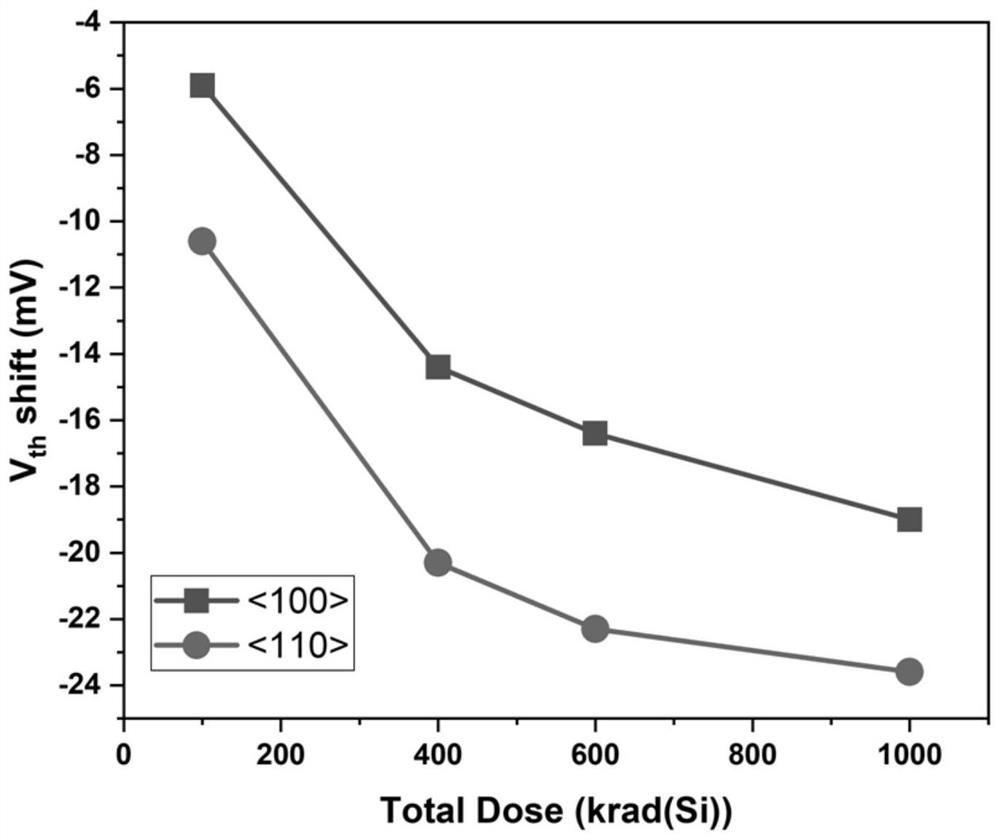

[0016] Example 1: P-type FinFET devices with channel orientations of and were prepared on the same bulk silicon (100) wafer, and their anti-total dose radiation performance was compared. Specific steps are as follows:

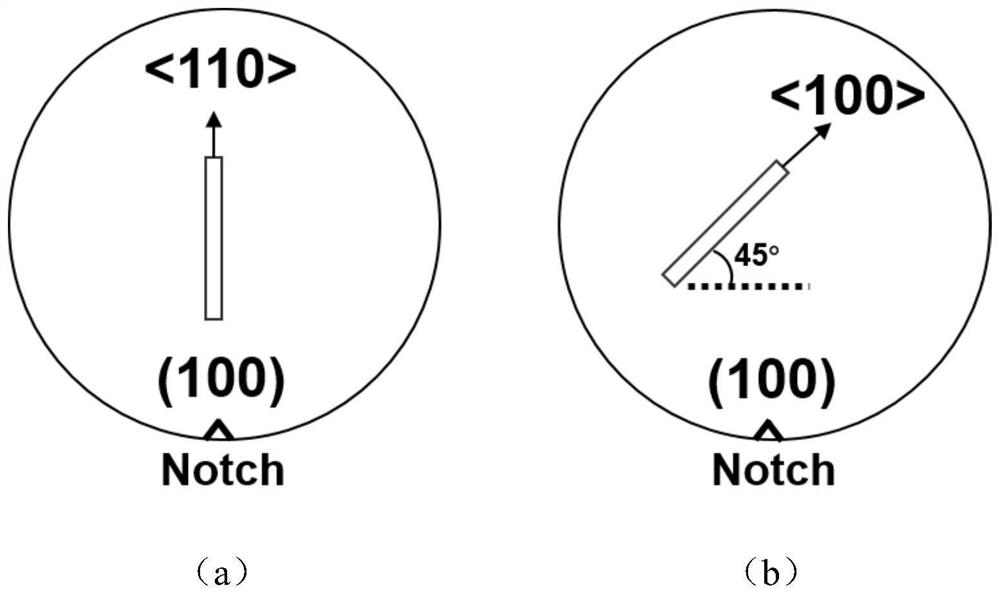

[0017] Step 1. Design P-type FinFET device layouts with channel crystal orientations of and on a (100) bulk silicon wafer. Except for different channel crystal orientations, other parameters are the same. For (100) wafers, the positioning mark (Notch) is downward as the positive direction, and the crystal orientation in the horizontal axis direction is . Ordinary layout FinFET device channel crystal orientation is , such as figure 1 It is shown in the middle left figure (a). The direction forming an angle of 45° with the horizontal axis is the channel direction of the FinFET device proposed by the present invention, and the crystal direction of the FinFET channel is , such as figure 1 As shown in the middle right figure (b);

[0018] Step 2. Prepare two...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More