Segmented parallel comparison type ADC

A comparator and weight technology, applied in the direction of analog-to-digital converters, electrical components, code conversion, etc., can solve the problems of no significant innovation, hardware cost and conversion speed, etc., so as to reduce power consumption and facilitate Regular design and integration, the effect of reducing the use of high-power comparators

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] Hereinafter, the contents of the present invention will be described in detail with reference to the accompanying drawings. Please note that the exemplary embodiments described below are for explaining the content of the present invention, and the understanding of the present invention should not be limited to these embodiments and the following description.

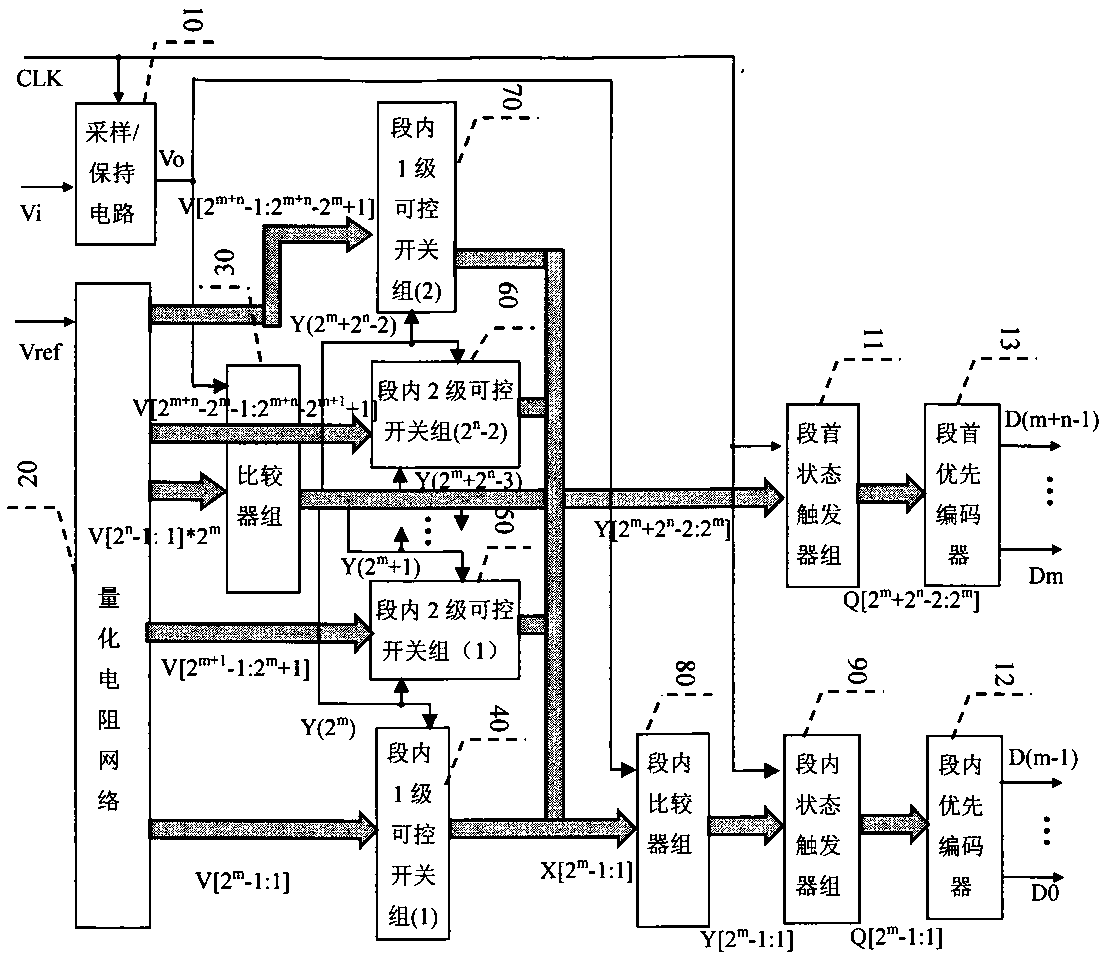

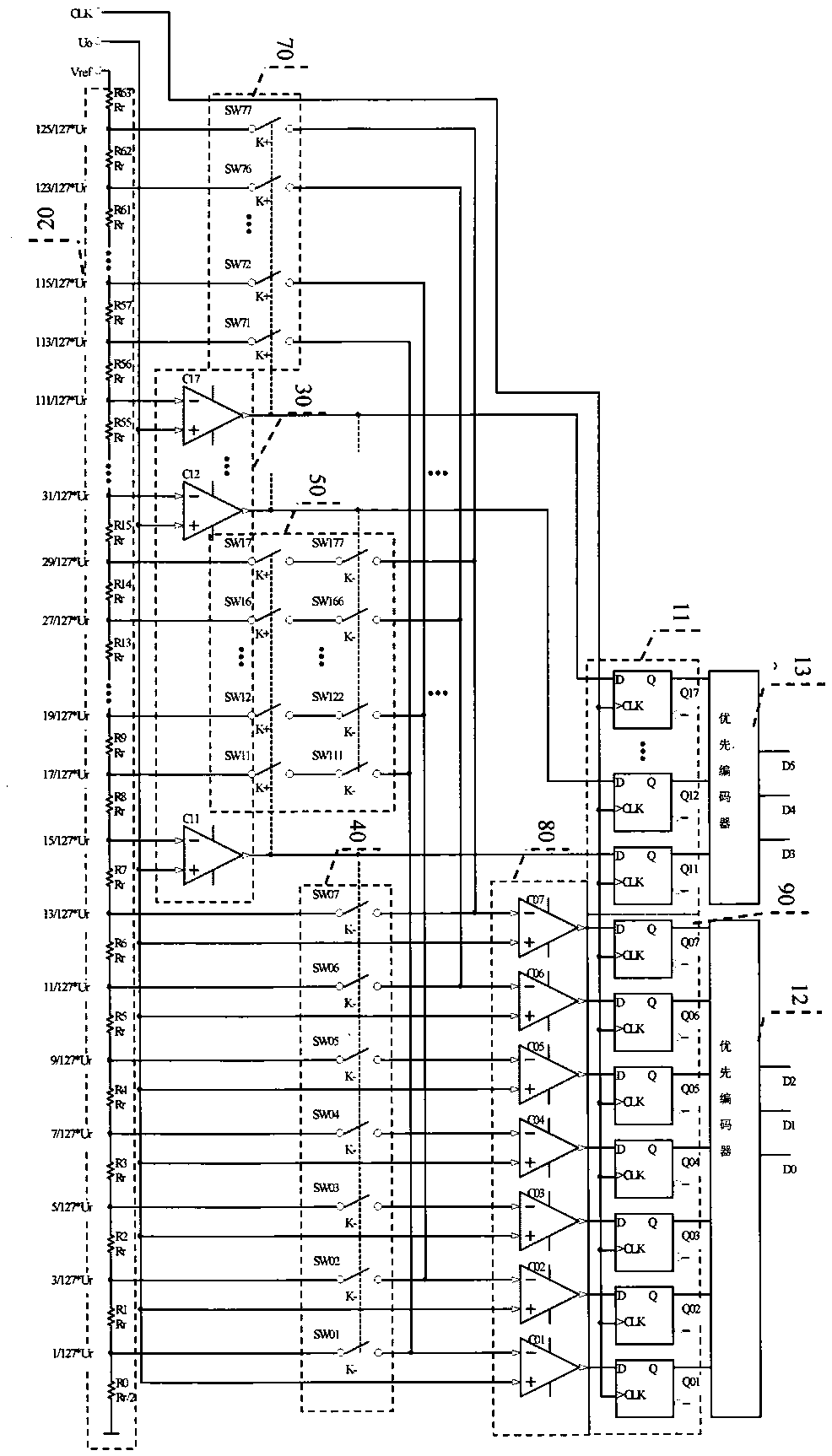

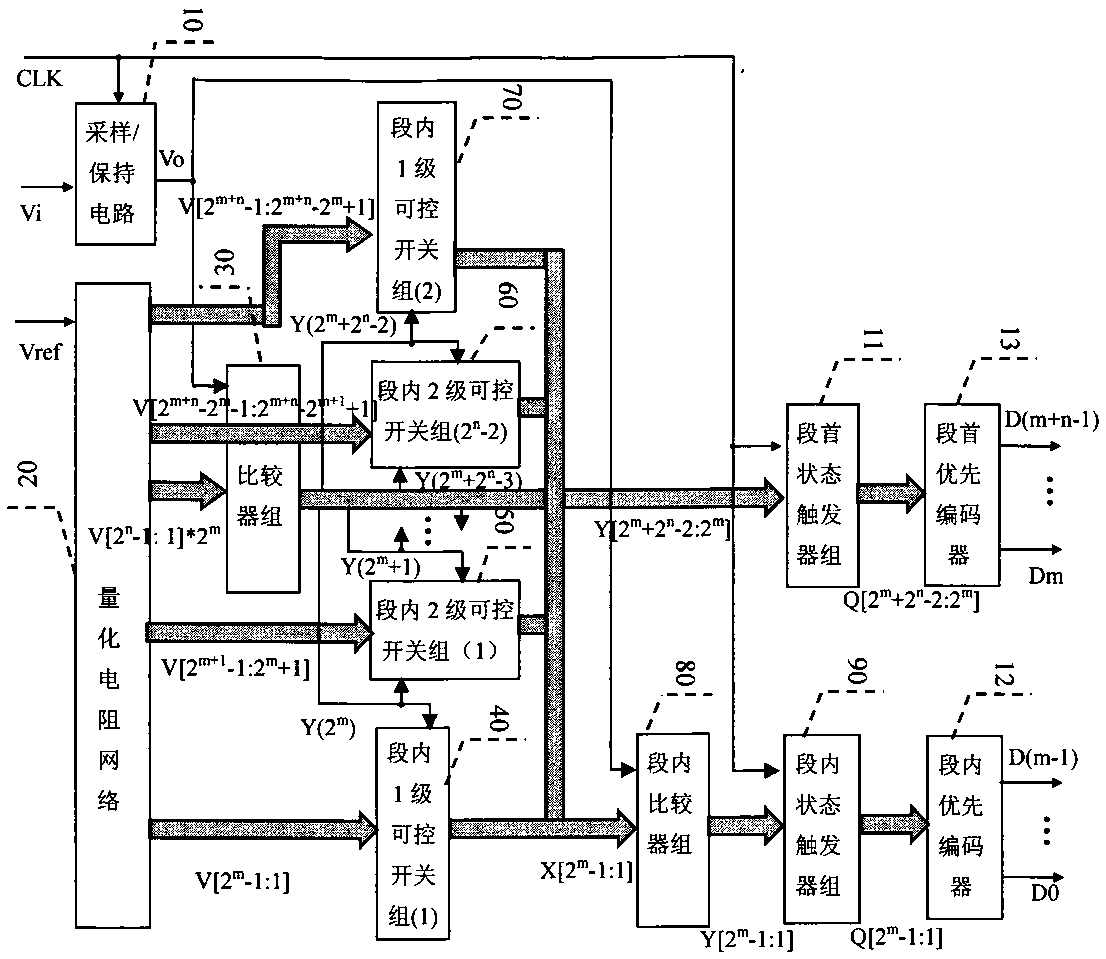

[0031] figure 1 A schematic diagram of the structure of the 2-section parallel comparison ADC of the present invention is given. The input signal includes the analog signal Vi to be converted, the clock CLK and the reference voltage Vref, and the output signal has m low-order binary codes and n high-order binary codes. CLK respectively controls the sample / hold circuit 10, the intra-segment state trigger group 90 and the segment-first state trigger group 110 to realize the start and save functions of the converter. The unit 10 is a sample / hold circuit, which samples and holds Vi under the control of CLK, and outpu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More