Hash join acceleration method and system based on BRAM in FPGA chip

A technology for accelerating the system and hash table, which is applied in the field of hash connection acceleration method and system, can solve the problem of large occupation and achieve the effect of overcoming the memory bottleneck

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

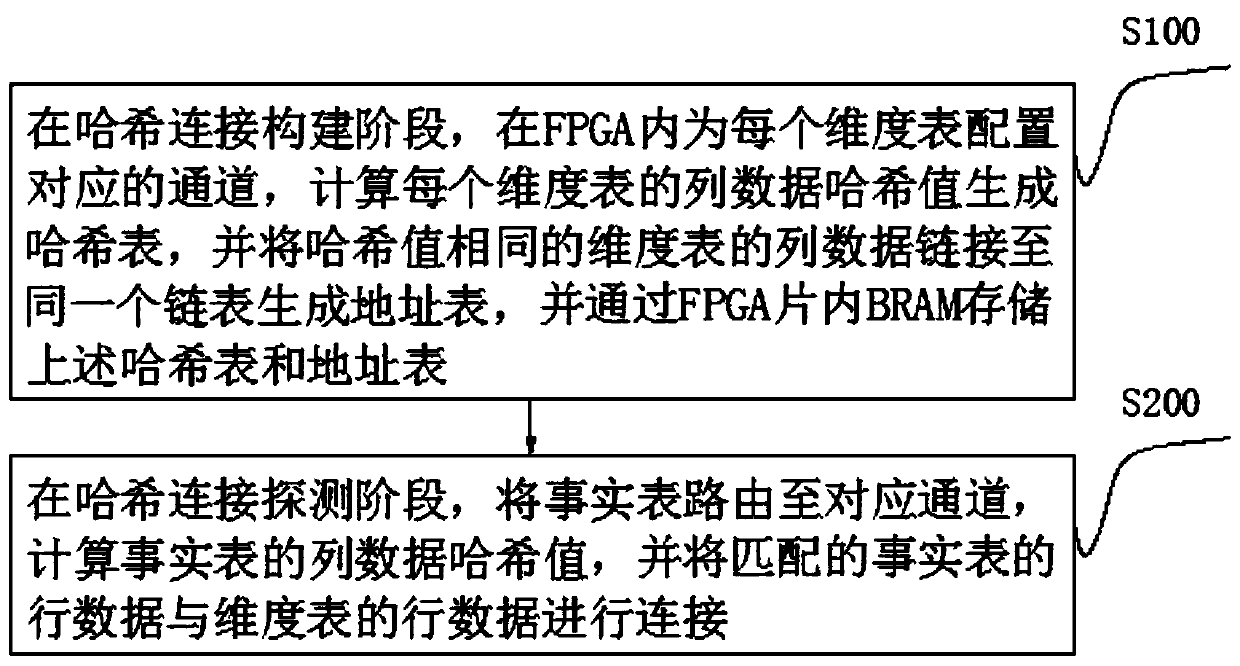

[0049] as attached Figure 1-4 As shown, the hash connection acceleration method based on FPGA on-chip BRAM of the present invention connects multiple dimension tables or multiple columns of the same dimension table to the fact table through multiple channels in parallel, including:

[0050]S100. In the hash connection construction phase, configure a corresponding channel for each dimension table in the FPGA, calculate the hash value of the column data of each dimension table to generate a hash table, and store the column data of the dimension tables with the same hash value Link to the same linked list to generate an address table, and store the above hash table and address table through the FPGA on-chip BRAM;

[0051] S200. In the hash join detection phase, route the fact table to the corresponding channel, calculate the hash value of the column data of the fact table, and connect the row data of the matched fact table and the row data of the dimension table.

[0052] Among...

Embodiment 2

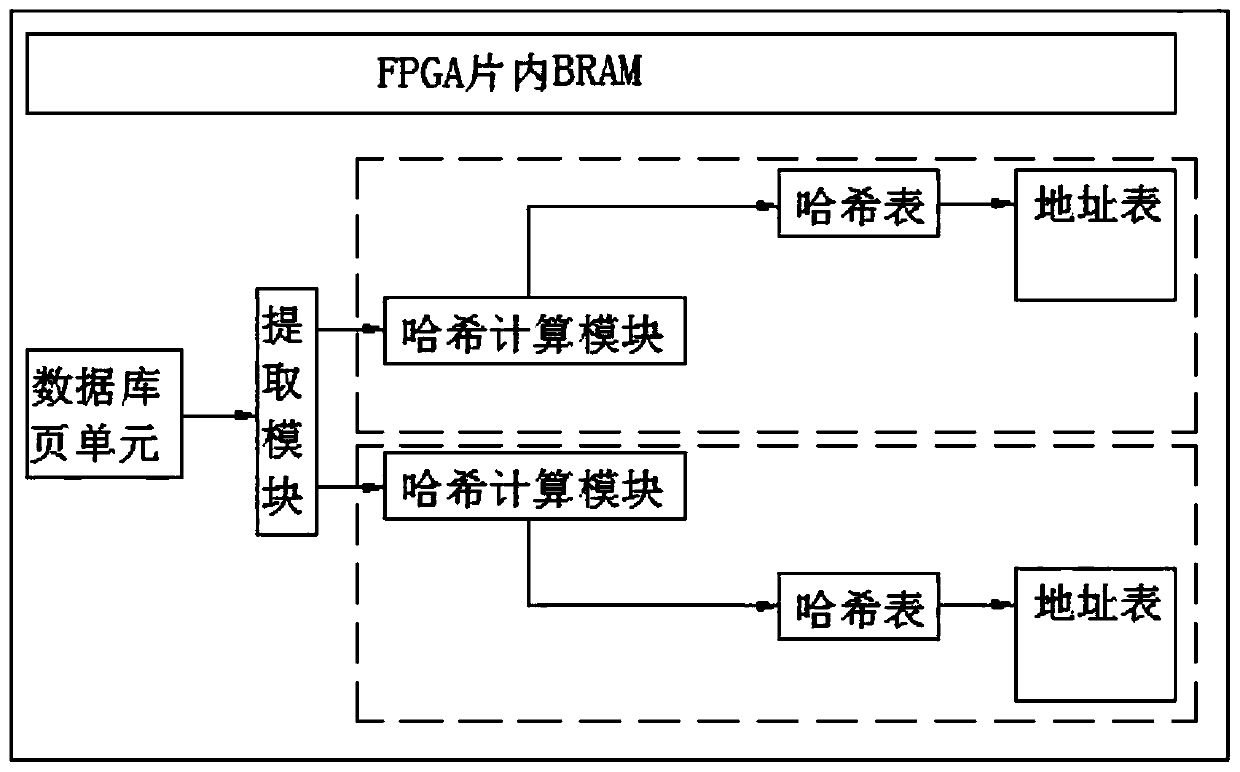

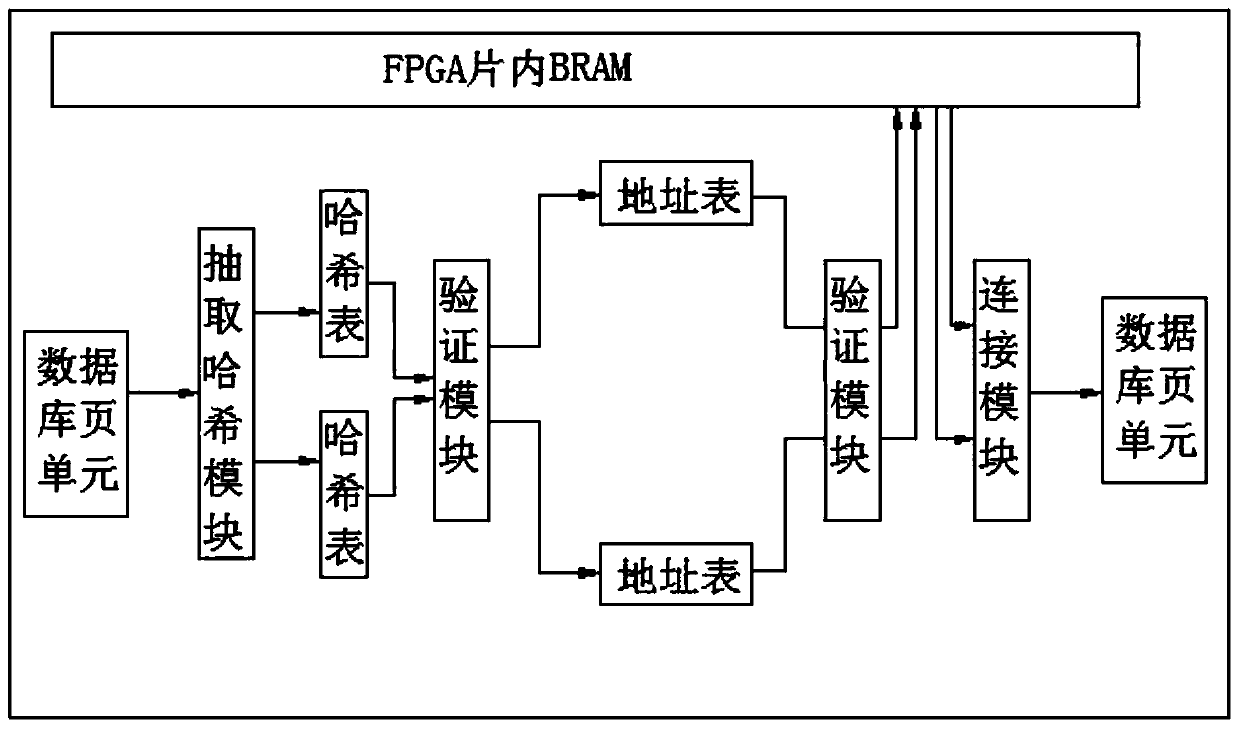

[0066] The present invention provides a hash connection acceleration subsystem based on the BRAM in the FPGA chip, including the BRAM in the FGPA chip configured on the PFGA, a plurality of channels, a hash calculation module, an extraction module, an extraction / hashing module, a verification module and control module.

[0067] Among them, FPGA on-chip BRAM is used to store hash table, address table and database element unit.

[0068] Each channel is assigned a dedicated resource that allows multiple channels of all the above configurations to be processed in parallel during the probing phase of the hash table.

[0069] The hash calculation module is used to calculate the hash value of the column data of the dimension table.

[0070] The extraction module is used to extract database page units for each dimension table.

[0071] The extraction / hash module is used to match the fact table into the corresponding channel, and is used to calculate the column data hash value of eac...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More