A fault-tolerant architecture for tsv in 3D integrated circuits

An integrated circuit, three-dimensional technology, applied in the direction of circuit, CAD circuit design, electrical components, etc., can solve the problems of unable to transmit signals normally, 3D chips are prone to failure, poor cluster fault tolerance, etc., to improve redundancy rate, Avoid the effect of too large difference in length and high repair rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

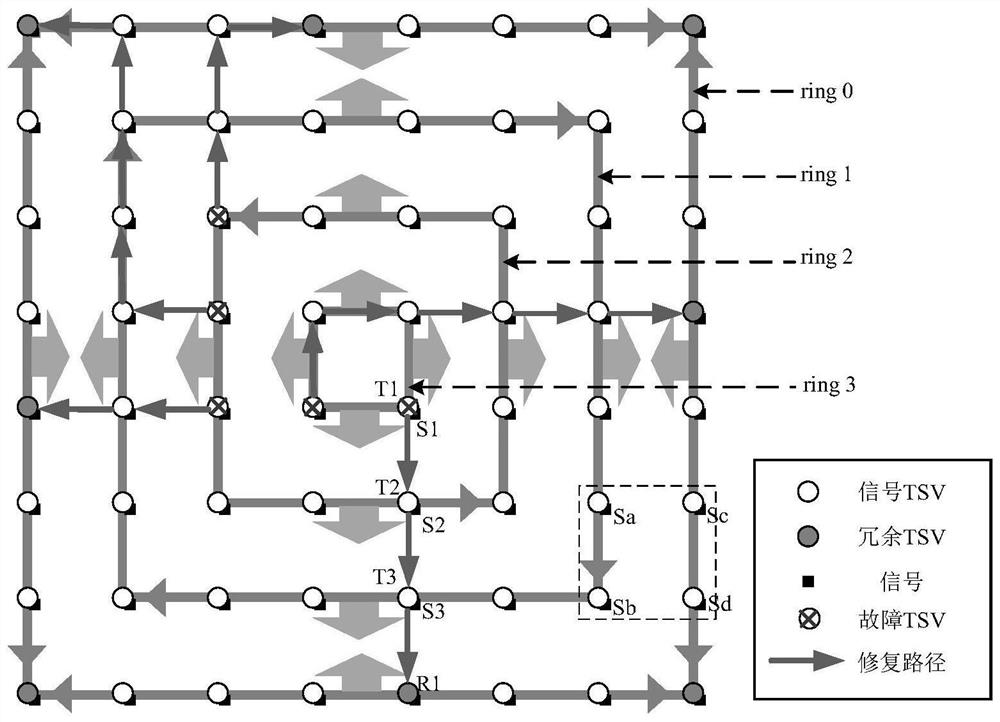

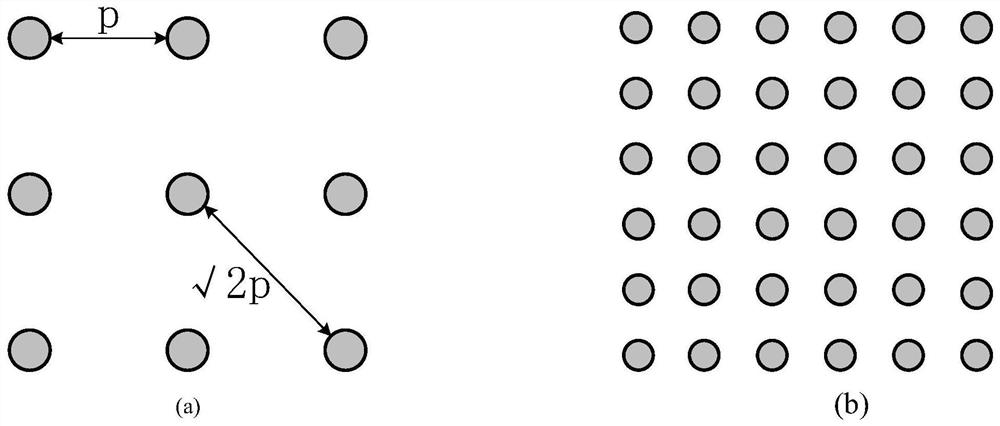

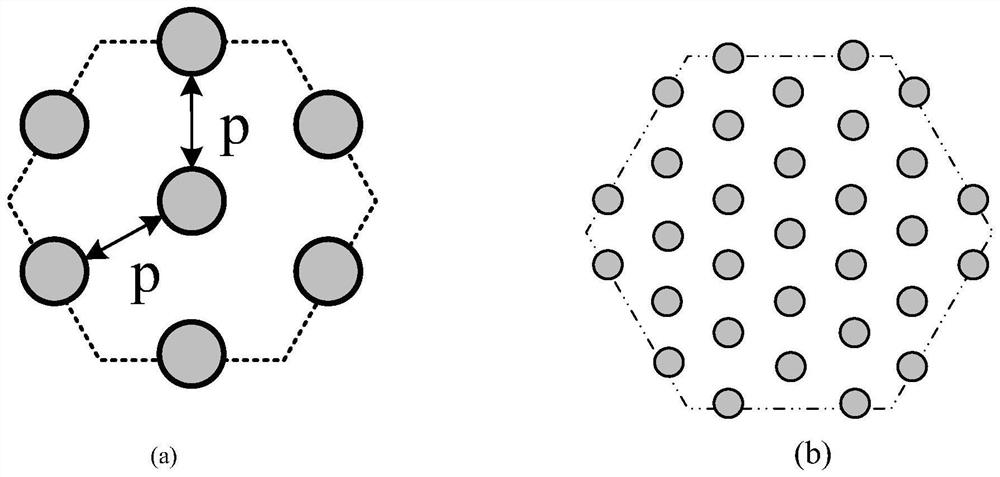

[0028] An important issue in the design process of a three-dimensional integrated circuit is the placement of TSVs, which are mainly responsible for signal transmission between layers. figure 2 (a) is a common 3×3 grid topology. There are 3 TSVs in each row and column of the TSV array, and a total of 9 TSVs are formed. figure 2 In (a), p is the pitch, that is, the distance between adjacent TSVs. In the grid topology, the TSV distance between the TSV and the adjacent horizontal and vertical direction is p, and the TSV distance from the center point TSV to the diagonal position is The distance b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com