A kind of NOR flash memory device and preparation method thereof

A flash memory device and control gate technology, which is applied in the direction of semiconductor devices, electric solid state devices, electrical components, etc., can solve problems such as breakdown and leakage of NOR flash memory devices, so as to avoid leakage or breakdown, increase thickness, and improve reliability Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

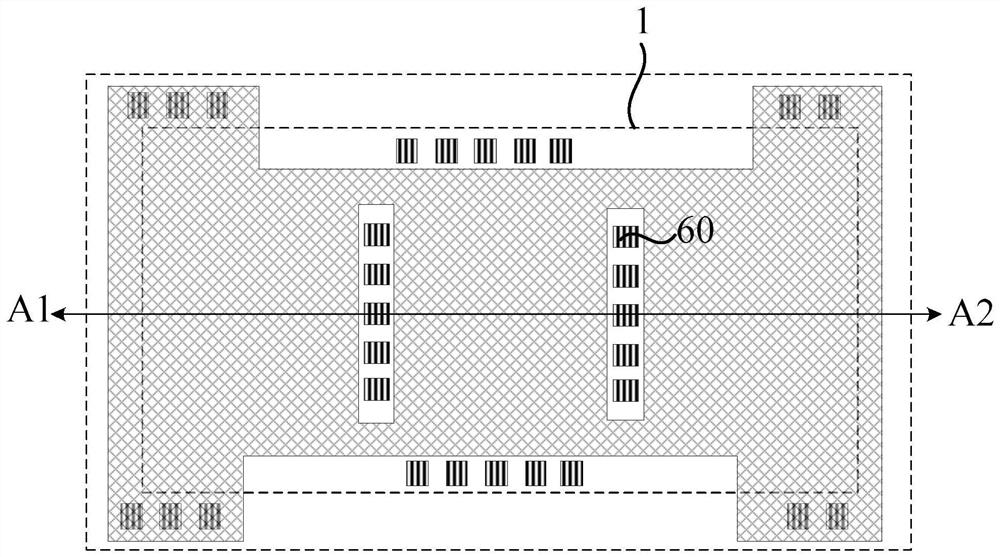

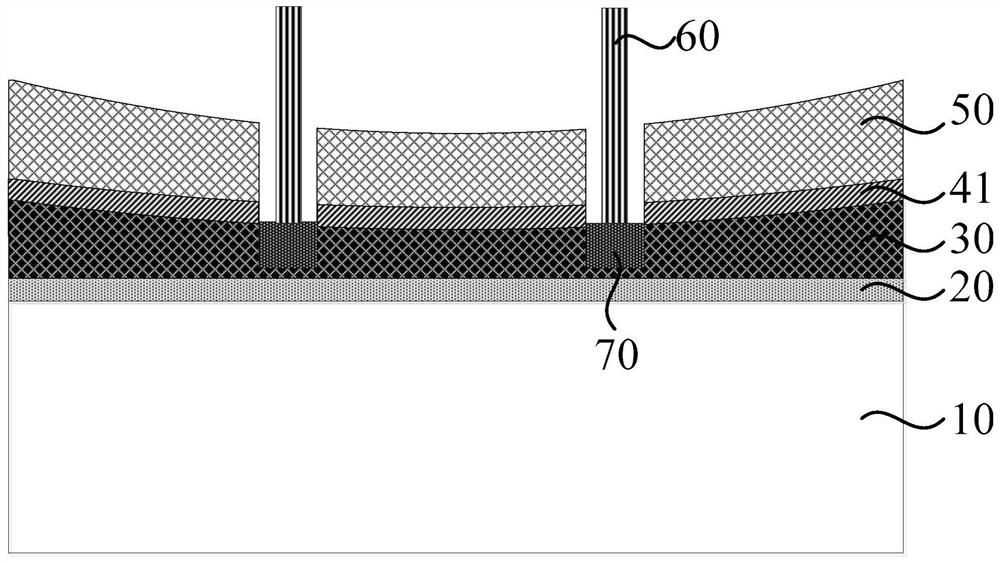

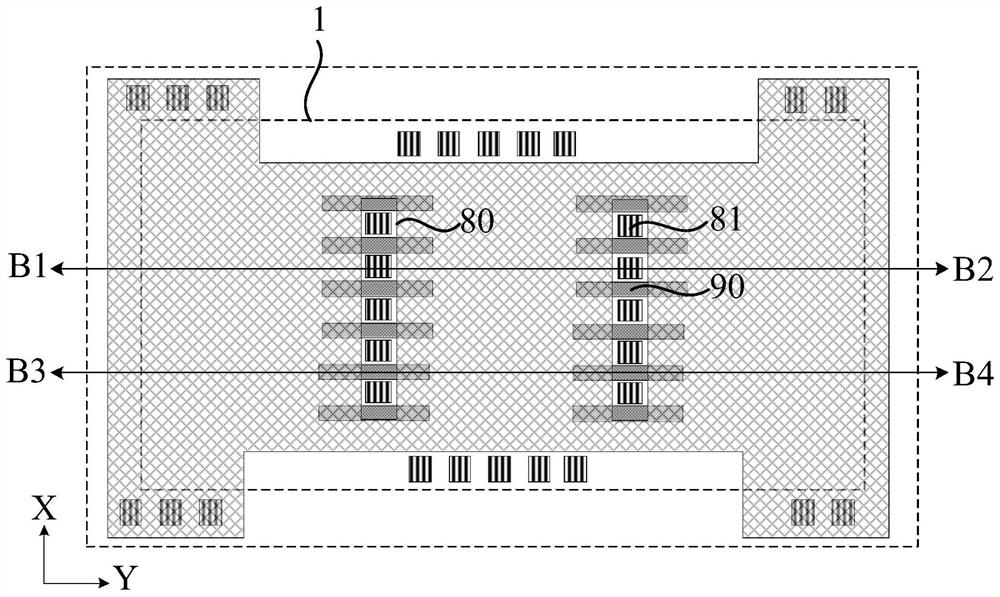

[0042] image 3 It is a schematic top view structure diagram of a NOR flash memory device provided by Embodiment 1 of the present invention. Figure 4 yes image 3 Schematic diagram of the cross-sectional structure along B1-B2. Figure 5 yes image 3 Schematic diagram of the cross-sectional structure along B3-B4. see Figure 3-Figure 5 The NOR flash memory device provided by Embodiment 1 of the present invention includes a substrate 10, a tunnel oxide layer 20, a floating gate layer 30, a dielectric layer 40, and a control gate layer 50 stacked in sequence; at least one through the control gate layer 50 and the dielectric layer The floating gate via hole 80 of the electrical layer 40, the floating gate via hole 80 is located in the active area 1, and is used to expose the floating gate layer 30 to lead out the floating gate electrode 81; at least one active area blocking structure 90, the active area The region barrier structure 90 is disposed between the substrate 10 and...

Embodiment 2

[0080] Figure 11 It is a flow chart of a method for preparing a NOR flash memory device provided in Embodiment 2 of the present invention. Figure 12-Figure 17 It is a structural diagram corresponding to a manufacturing method of a NOR flash memory device provided in Embodiment 2 of the present invention. It should be noted, Figure 13-Figure 15 is the section along the active region barrier structure (see image 3 B3-B4) in the structure diagram of the NOR flash memory device obtained, Figure 16 and Figure 17 is along the cross-section that does not pass through the active region barrier structure (see image 3 Schematic diagram of the NOR flash memory device structure obtained in B1-B2).

[0081] see Figure 11 , the preparation method of the NOR flash memory device provided by the present invention, comprising:

[0082] S10: providing a substrate.

[0083] S20: forming at least one active region blocking structure on the substrate to define an opening area for fo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More