SoC chip deep sleep wake-up device

A deep sleep and wake-up device technology, applied in the direction of program control devices, program control design, instruments, etc., can solve the problem of inability to achieve ultra-low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The present invention will be described in more detail below in conjunction with the accompanying drawings and embodiments.

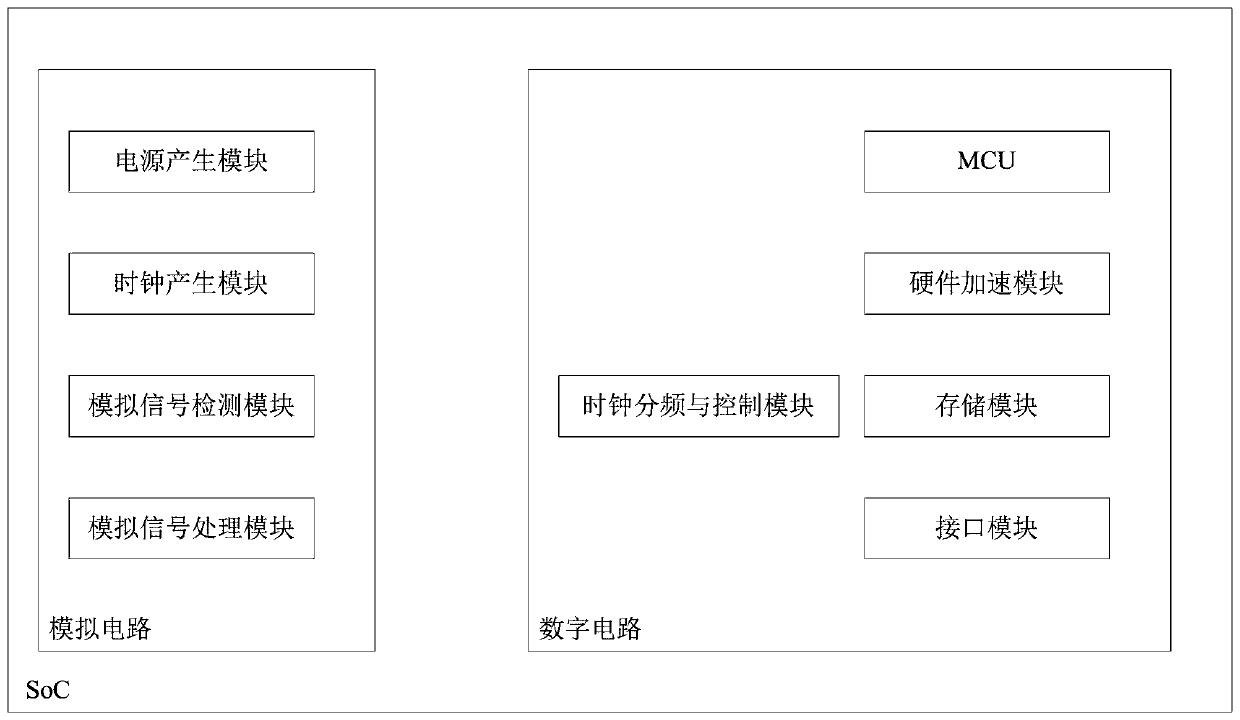

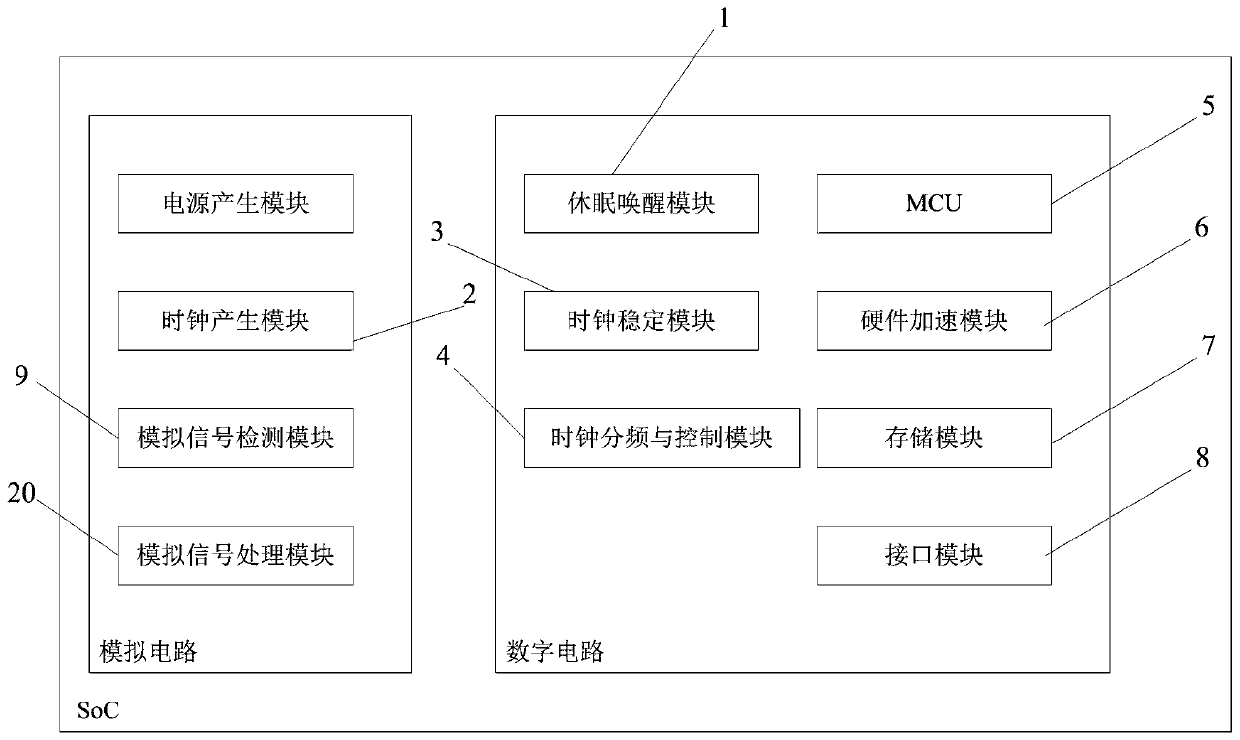

[0031] The invention discloses a SoC chip deep sleep wake-up device, please refer to image 3 and Figure 4 , which includes:

[0032] A dormant wake-up module 1, configured to access an external wake-up signal, generate an internal wake-up signal according to the external wake-up signal, and generate a source clock enable signal when the internal wake-up signal meets a preset wake-up requirement;

[0033] A clock generation module 2, connected to the dormancy wake-up module 1, the clock generation module 2 is used to generate a source clock signal according to the source clock enable signal;

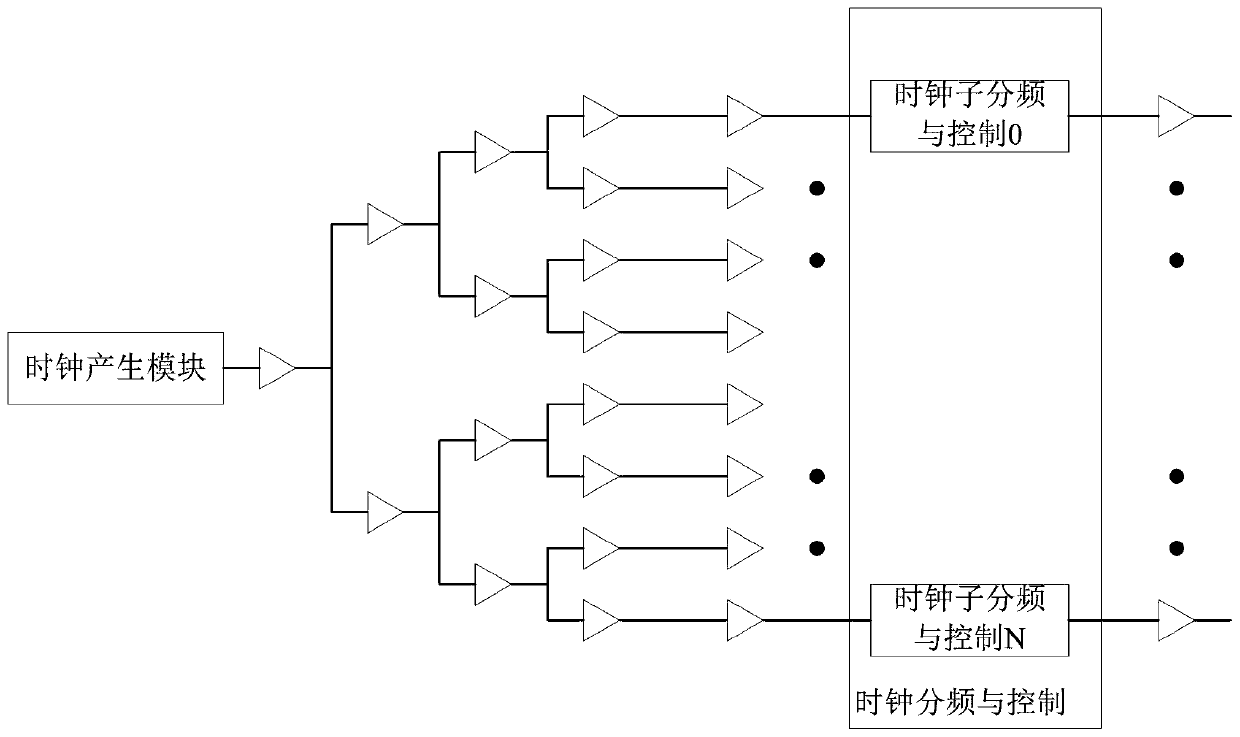

[0034] A clock stabilization module 3, connected to the clock generation module 2, the clock stabilization module 3 is used for cumulatively counting the source clock signal, and generating a stable clock signal when the cumulative count value reaches a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More