System on chip and its interface data processing method and device

A technology of interface data and system-on-chip, which is applied in electrical digital data processing, architecture with a single central processing unit, digital computer components, etc. The effect of wrong selection, easy operation, and saving port resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

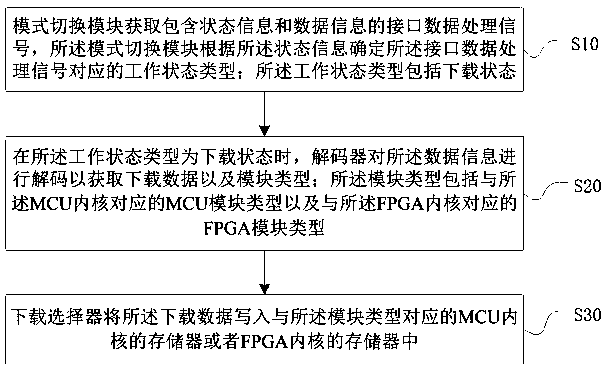

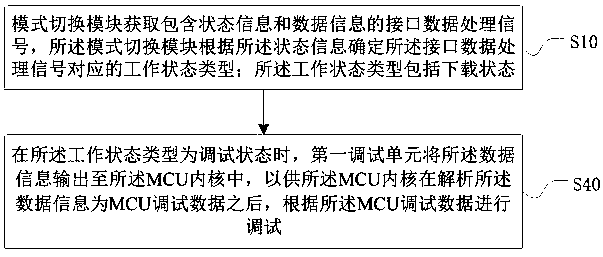

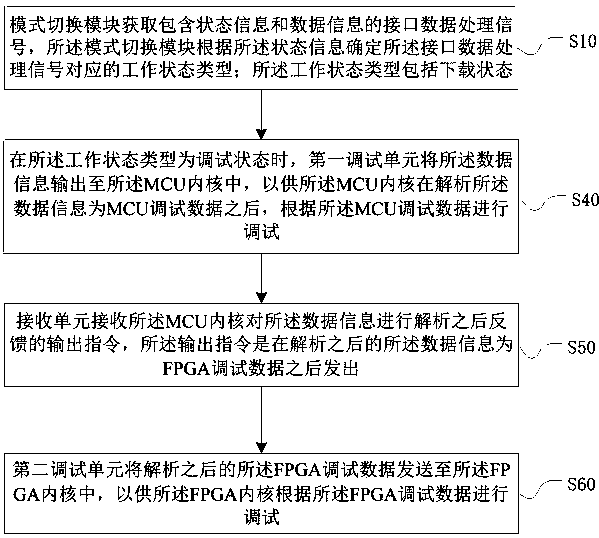

[0024] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are some of the embodiments of the present invention, but not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

[0025] The invention provides an on-chip system and its interface data processing method and device, which realizes the automatic switching of the download or debugging mode of the MCU core and the FPGA core, saves the port resources of the on-chip system, is easy to operate, and avoids the MCU core and FPGA core. The programming error of the system-on-chip is caused by the selection error of the core or the selection error of the mode.

[0026] The in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More