FPGA (Field Programmable Gate Array) switch unit based on STT-MRAM (Short Term Transistor-Magnetic Random Access Memory)

A switching unit and control unit technology, applied in the field of integrated circuits, can solve the problems of high cost of FLASH type FPGA, poor reliability of SRAM type FPGA, loss of data after power failure, etc. effect of times

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

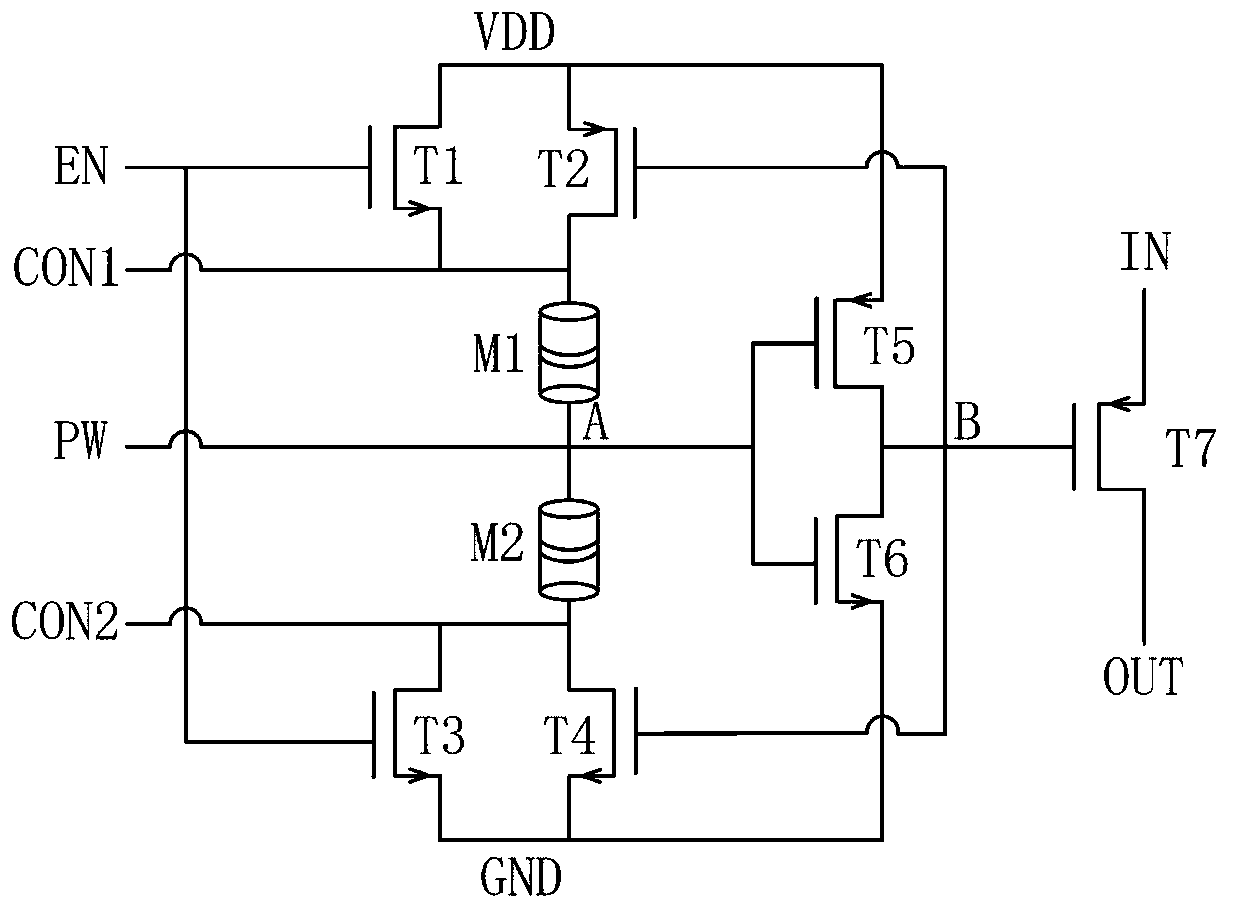

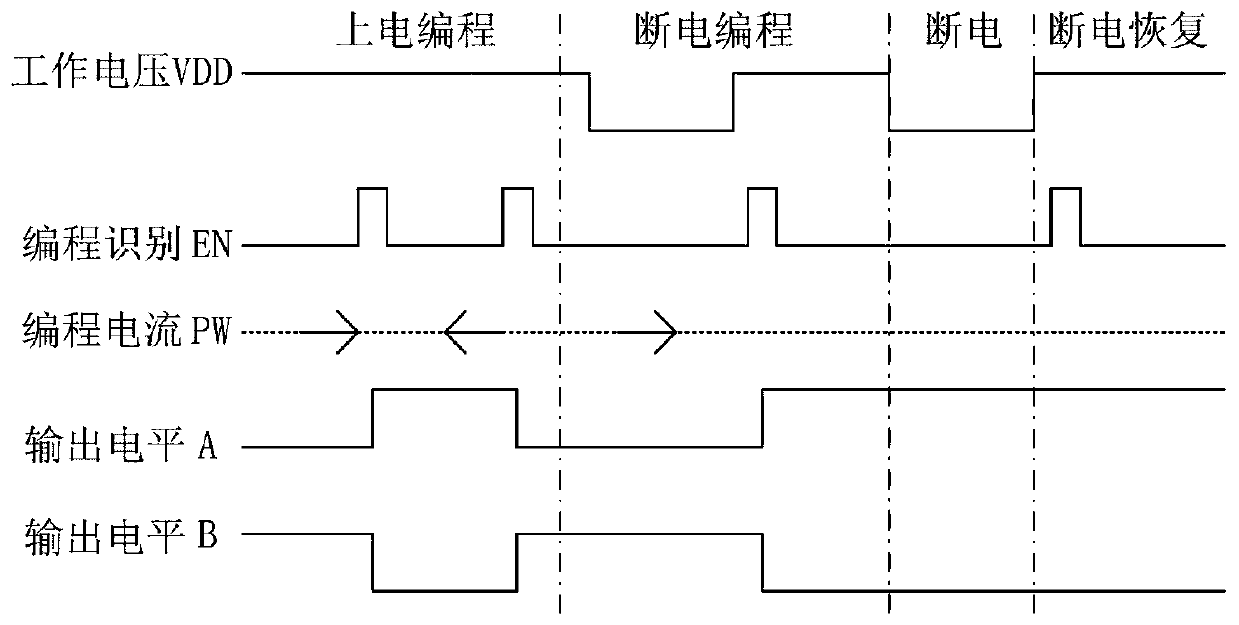

[0030] The present invention provides a FPGA switch unit based on STT-MRAM, comprising an STT-MRAM element group, a control unit, an inverter and a switch unit; wherein, the STT-MRAM element group generates a potential to the inverter, The inverter inverts the potential and feeds it back to the control unit, and the control unit controls the potential latch of the STT-MRAM element group under the action of the inverter; the switch unit is connected to the connected to the output of the inverter. Through the feedback effect of the inverter, the FPGA switch unit is in the working mode, and the two ends of the STT-MRAM element group are always in an equipotential state, reducing the electrical stress effect on the STT-MRAM element in the STT-MRAM element group , improve the reliability of the device.

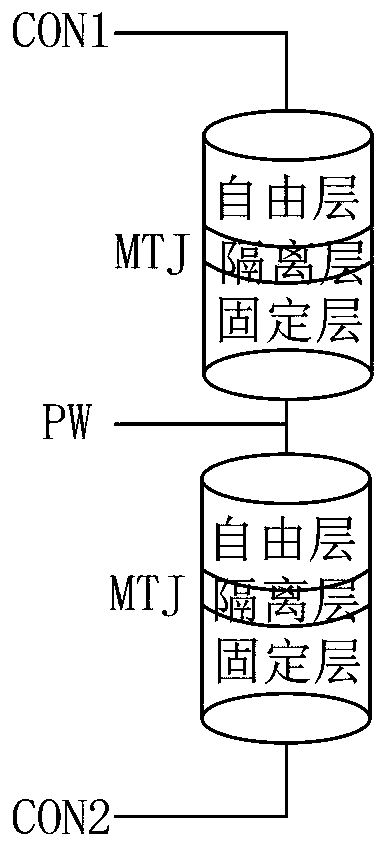

[0031] Specifically, an implementation structure of the FPGA switch unit based on STT-MRAM is as follows figure 1 shown. The STT-MRAM element group includes several STT-MRAM ele...

Embodiment 2

[0045] Embodiment 2 of the present invention provides another implementation of the FPGA switch unit based on STT-MRAM, such as Figure 4 shown. Compared with the first embodiment, the control unit includes PMOS transistors T1, T2, T3 and NMOS transistor T4; wherein, the gate of the PMOS transistor T1 is connected to the control signal EN, the source is connected to the power supply VDD, and the drain is connected to the PMOS transistor T2. Drain: the gate of the PMOS transistor T2 is connected to the output terminal of the inverter, the source is connected to the power supply VDD, and the drain is connected to the STT-MRAM element group, that is, the free layer of the STT-MRAM element M1; the PMOS transistor The gate of T3 is connected to the control signal EN, the drain is grounded to GND, the source is connected to the drain of the NMOS transistor T4; the gate of the NMOS transistor T4 is connected to the output terminal of the inverter, the source is grounded to GND, and t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More