Low emi deep trench isolation trench type power semiconductor device and manufacturing method thereof

A power semiconductor, deep trench isolation technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as EMI interference, high cost, large area, etc., to reduce chip cost, Improvement of chip current density and reduction of EMI interference

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0069] The present invention will be further described below in conjunction with specific drawings and embodiments.

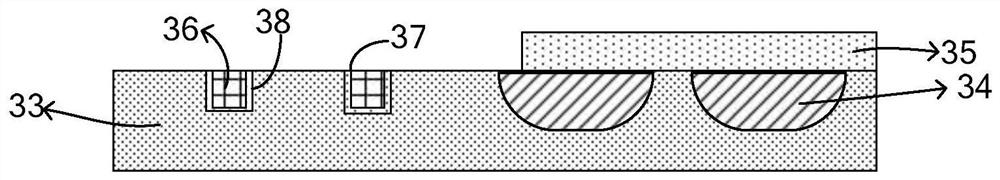

[0070] In order to effectively reduce EMI interference, reduce chip area, reduce cost, and increase current density, taking an N-type power semiconductor device as an example, the present invention includes a semiconductor substrate 1 with an N conductivity type, and at the center of the semiconductor substrate 1 The cell area and the terminal area located at the outer circle of the cell area are set in the area; the source metal 15 for connecting the cells in the cell area in parallel is arranged on the front side of the semiconductor substrate 1, and the semiconductor substrate 1 A back electrode structure is set on the back;

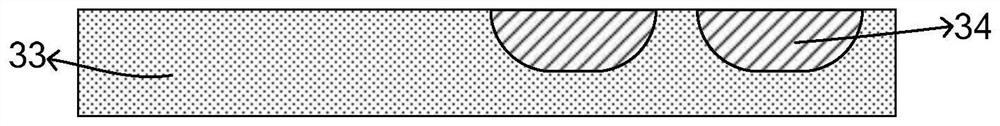

[0071]On the cross-section of the power semiconductor device, a P-type base region 11 penetrating through the semiconductor substrate 1 is provided in the upper part of the semiconductor substrate 1, and a plurality of terminal via hol...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More