Burr-free asynchronous set TSPC type D trigger with scanning structure

A glitch-free, flip-flop technology, applied in pulse generation, electrical components, and electrical pulse generation, etc., can solve glitches and power consumption improvement, imperfection and other problems, achieve small internal data delay, small ground area, and enhanced drive capability Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The specific implementation manner of this embodiment is described in detail below in conjunction with accompanying drawing:

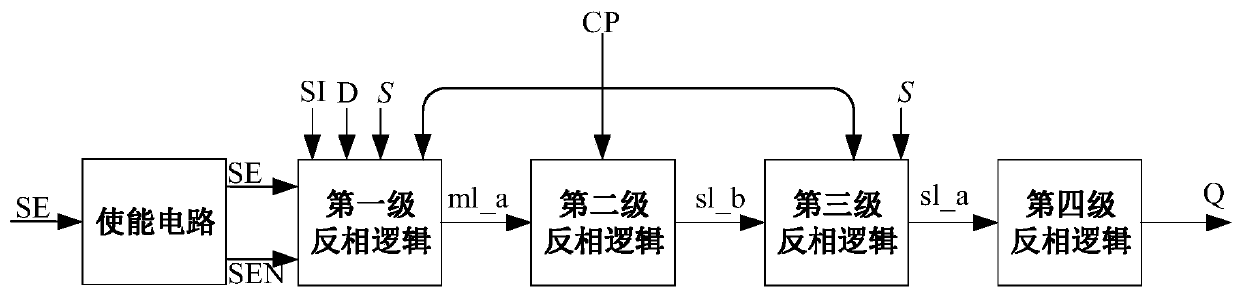

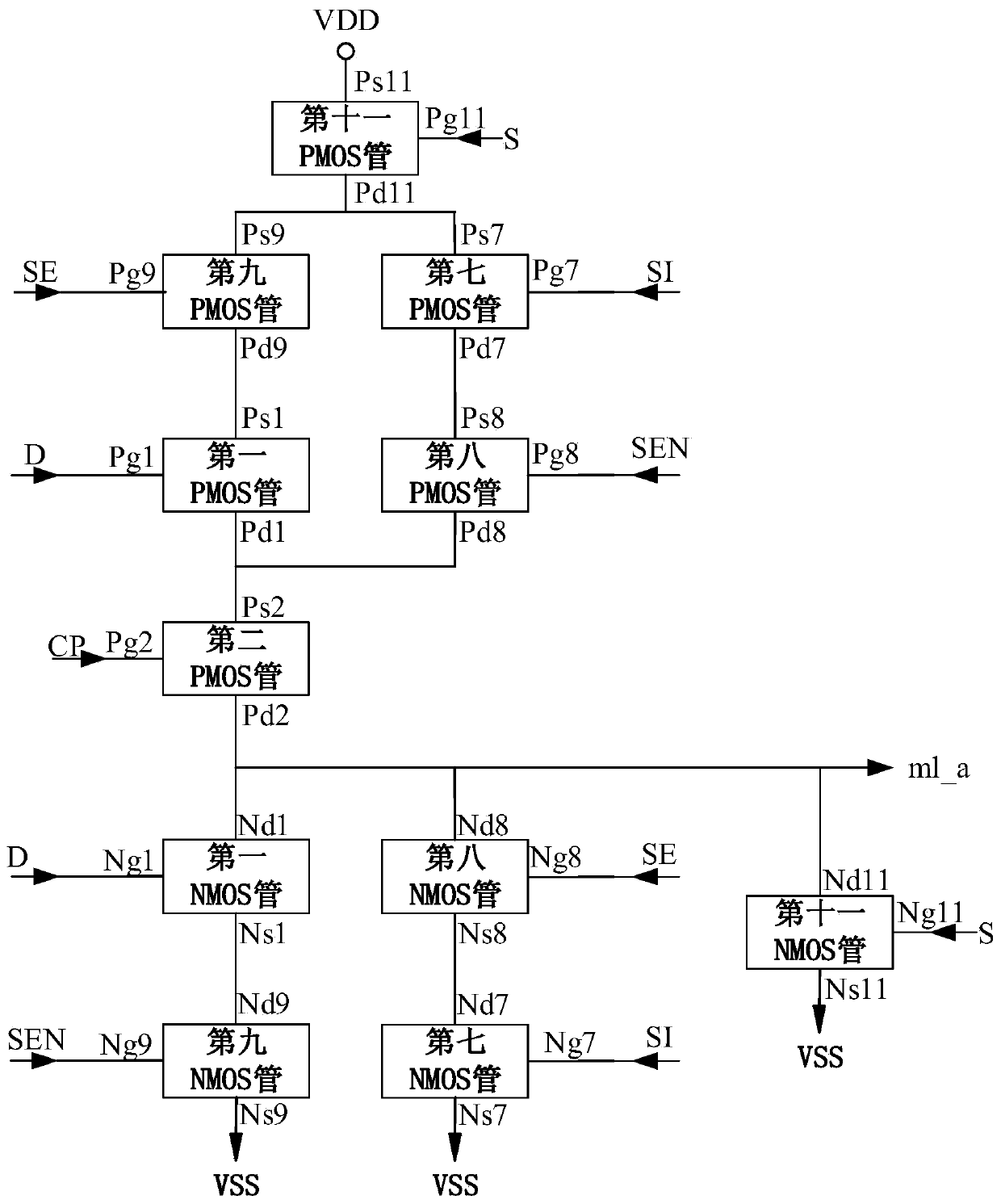

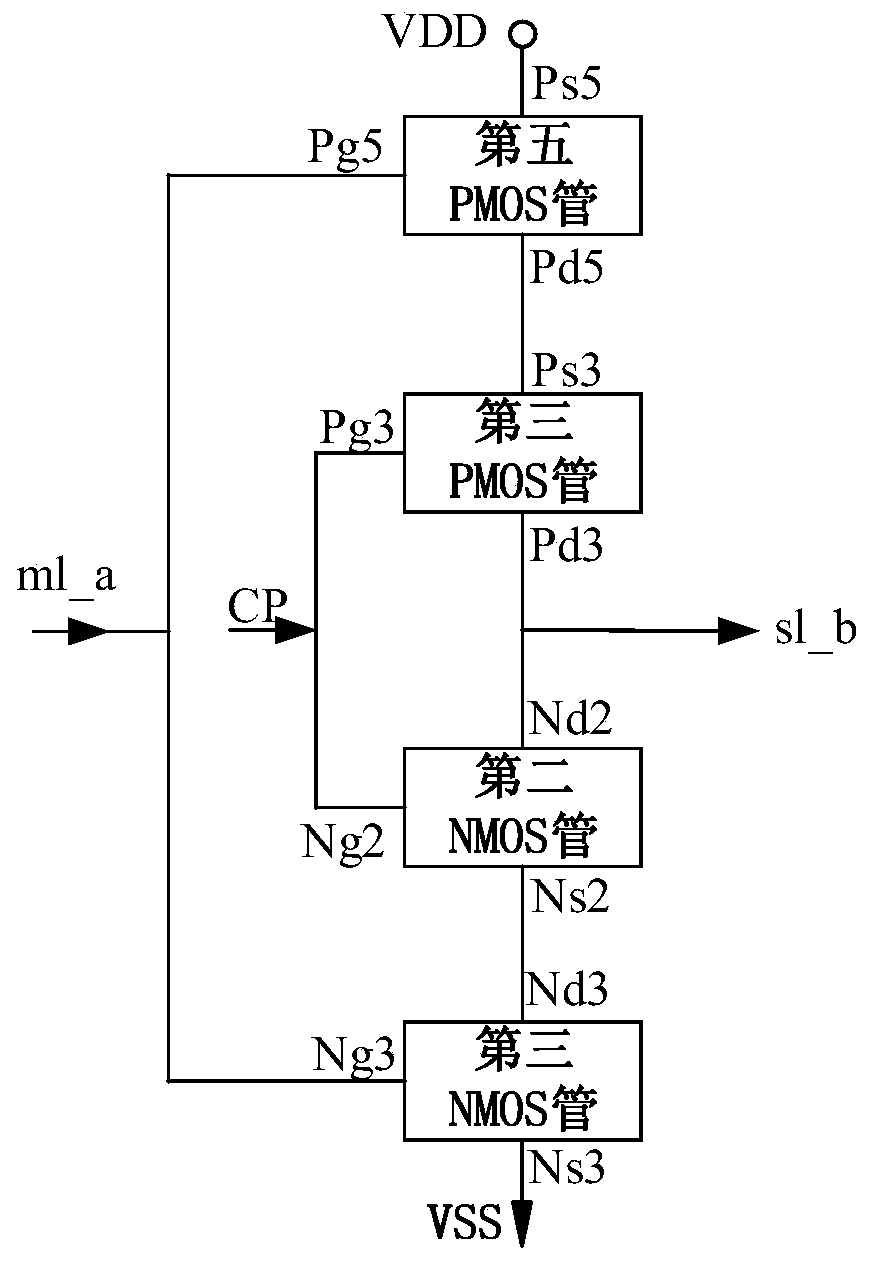

[0024] Such as figure 1 As shown, the glitch-free asynchronous setting TSPC type D flip-flop with scanning structure in this embodiment includes an enabling circuit, a first-stage inversion logic, a second-stage inversion logic, a third-stage inversion logic, and a fourth-stage inversion logic. To the logic, the enable circuit has an output end of the enable signal SE and its inversion signal SEN and is connected to the input end of the first-stage inverting logic, and the first-stage inverting logic also has the scanning signal SI respectively. The input terminal, the input terminal of the input data D, the input terminal of the set signal S and the input terminal of the clock CP and the output terminal of the signal ml_a, the second-stage inverting logic is used to convert the signal ml_a under the control of the clock CP Generate signal sl_b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More