Semiconductor Structure with Material Modification and Low Resistance Plug

A manufacturing method and technology of integrated circuits, applied in the manufacturing of circuits, electrical components, semiconductor/solid-state devices, etc., can solve problems such as voids or other defects, and inability to fully meet requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

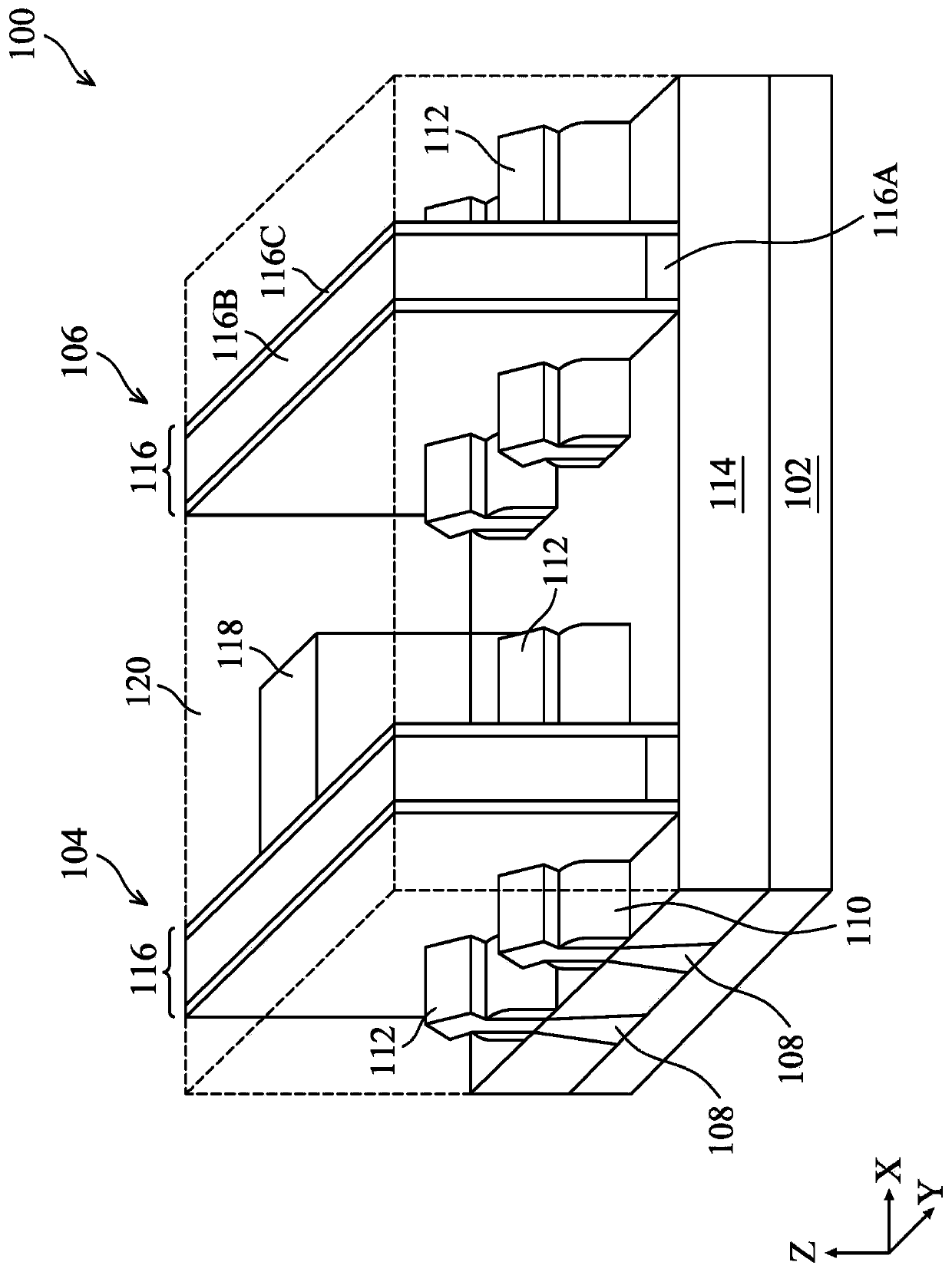

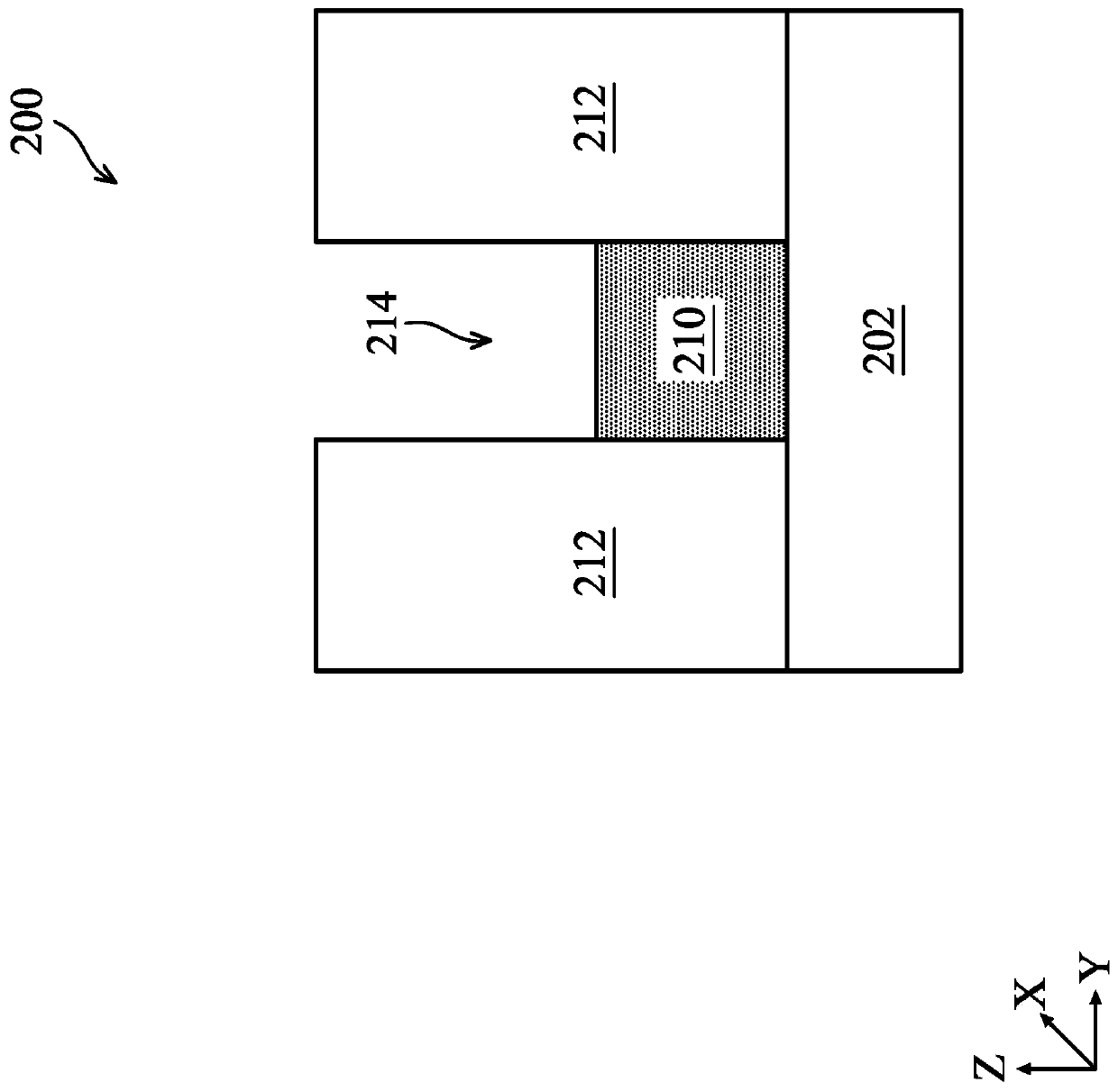

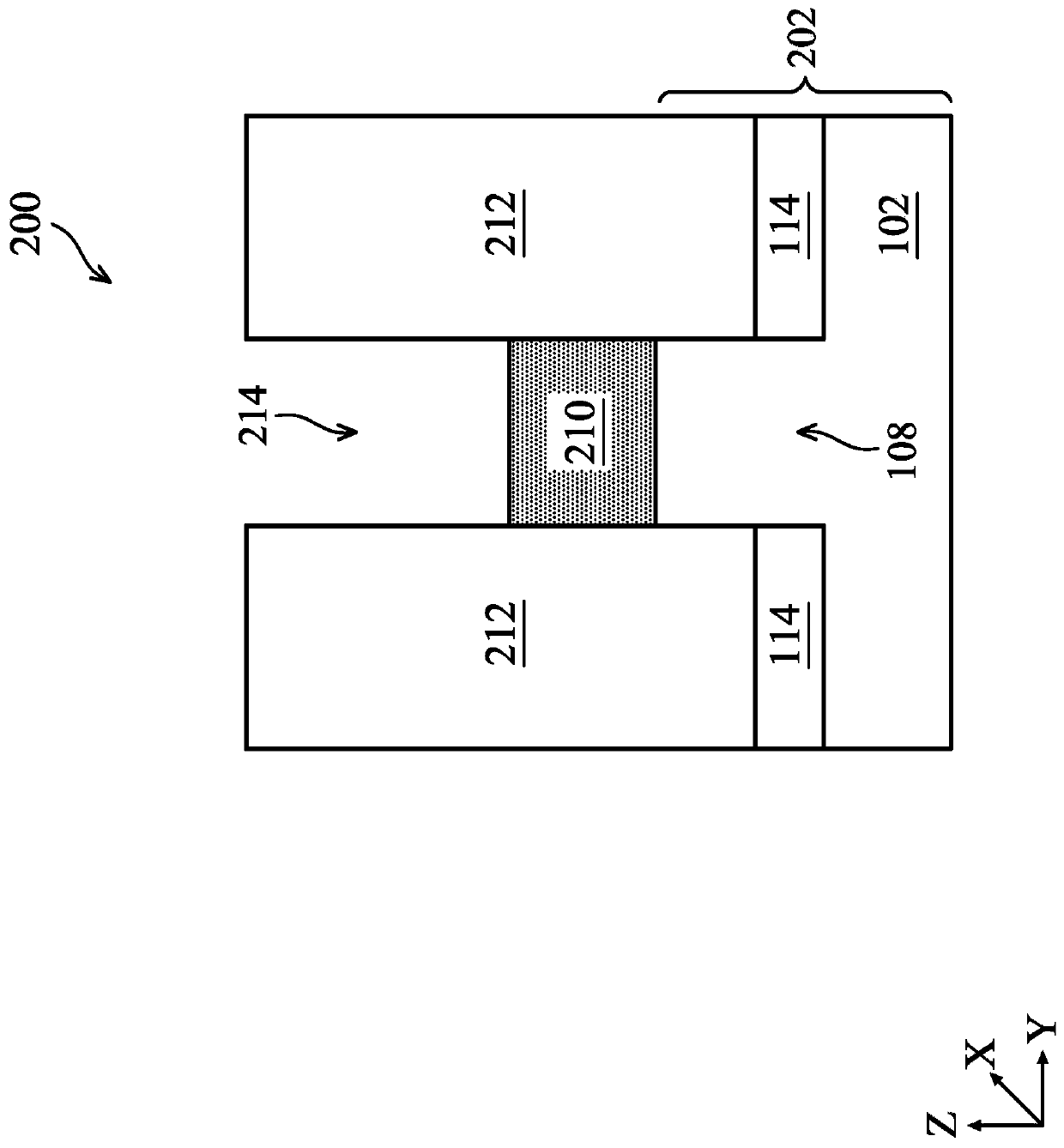

[0057] Different embodiments or examples provided below may implement different configurations of the present invention. The examples of specific components and arrangements are used to simplify the invention and not to limit the invention. For example, the statement that a first component is formed on a second component includes that the two are in direct or physical contact, or there are other additional components interposed therebetween rather than in direct contact. In addition, numbers may be repeated in various examples of the present disclosure, but these repetitions are only for simplification and clarity of illustration, and do not mean that units with the same numbers in different embodiments and / or arrangements have the same corresponding relationship.

[0058] In addition, spatial relative terms such as "below", "beneath", "lower", "above", "above", or similar terms may be used to simplify describing the relationship between one element and another element in the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More