Scanning test compression optimization method

A technology of scanning test and optimization method, applied in the field of image sensor, can solve problems such as increasing test difficulty, and achieve the effect of improving test efficiency and yield, low loss of fault coverage, and high test compression efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

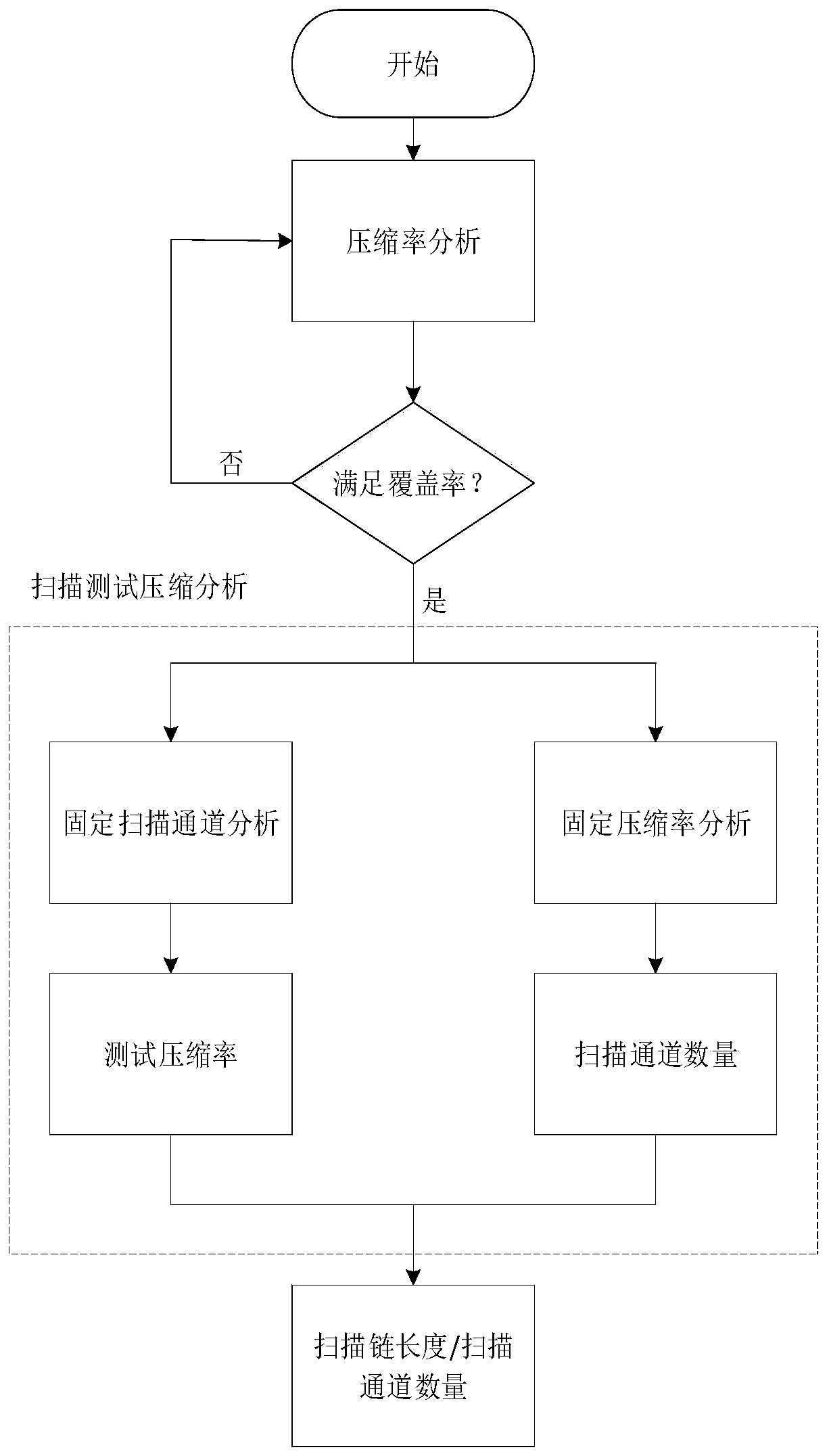

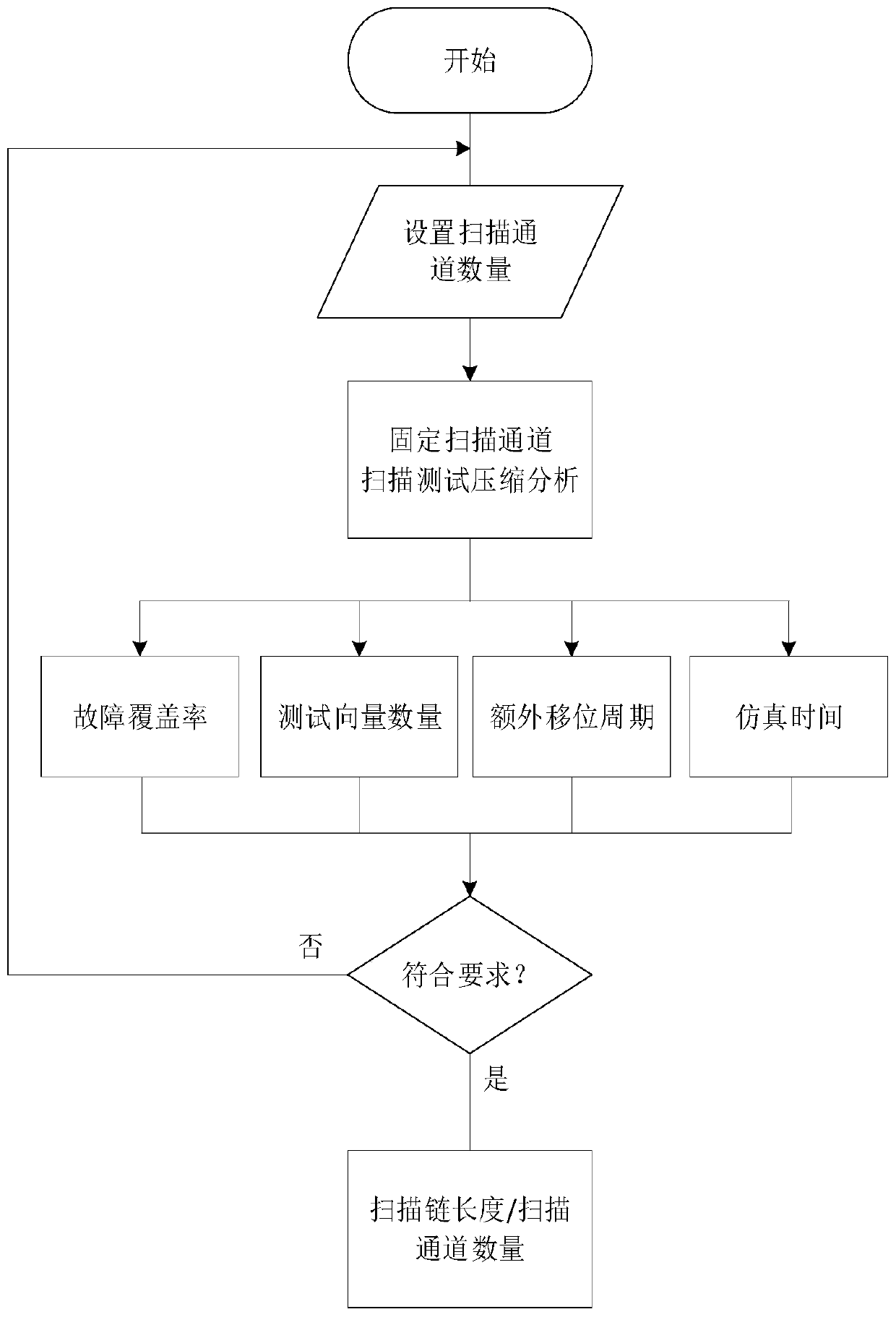

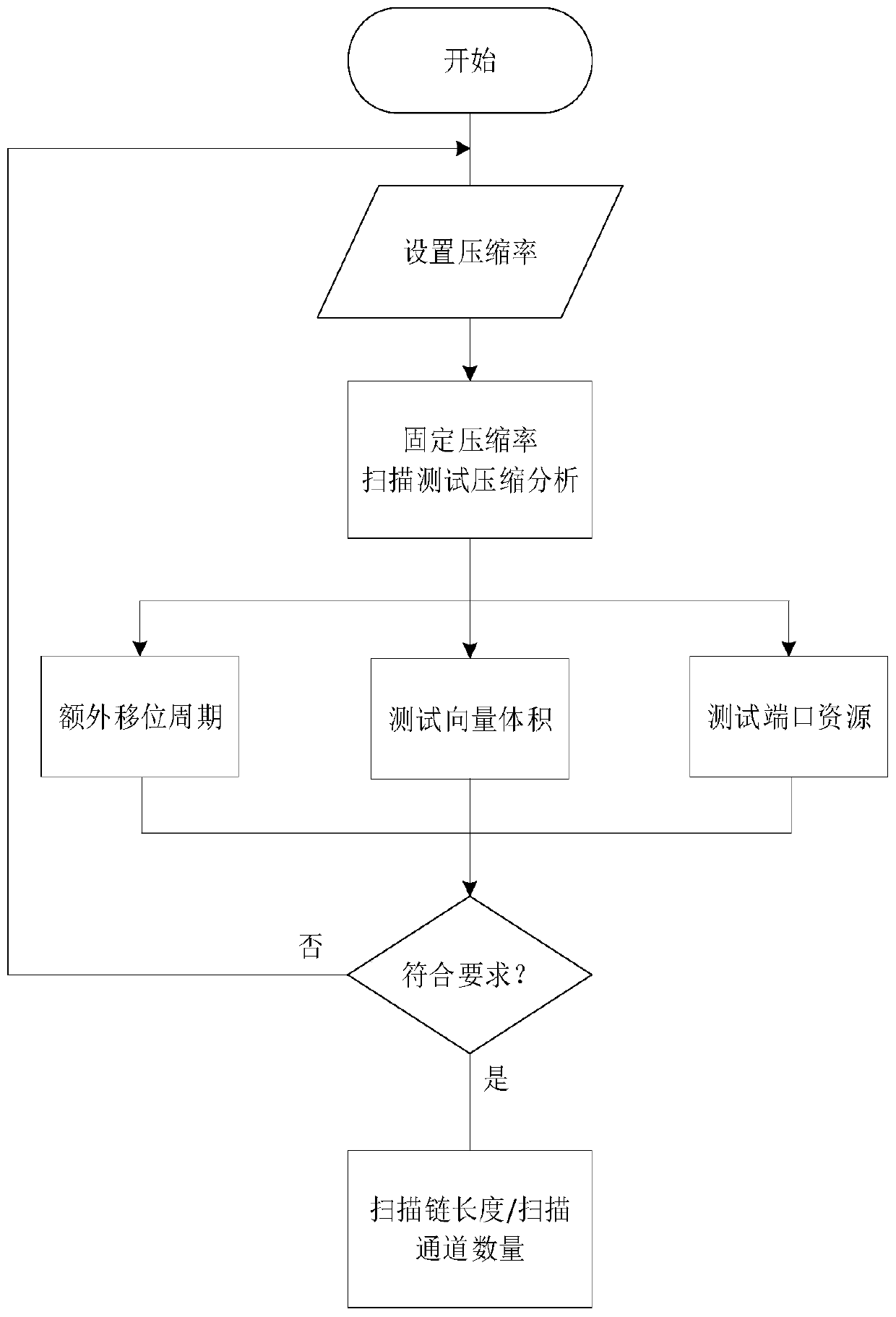

Method used

Image

Examples

Embodiment Construction

[0021] The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0022] The scan test of the chip is divided into three processes of test initialization, shift and capture. Each test vector will complete its own shift and capture. The shift occupies most of the time of the scan test. Therefore, only the scan shift is considered. Under data and cycle conditions, the volume of scan test data V test and test time T test They can be calculated by the following formulas respectively:

[0023] V test =IOs*Patterns*Cycles (1)

[0024]

[0025] In the formula: IOs is the number of scanning test ports, Patterns is the number of test vectors, Cycles is the number of shift cycles of test vectors, F shift In order to test the clock frequency, the value...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com