Semiconductor device and method of forming the same

A semiconductor and device technology, applied in the field of semiconductor structure and its formation, can solve the problems of semiconductor device performance to be improved, gate dielectric layer thermal breakdown, device reliability reduction, etc., to improve the effective oxide layer thickness, reliability improvement, Effect of improved breakdown resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] As mentioned in the background, the performance of semiconductor devices formed in the prior art needs to be improved.

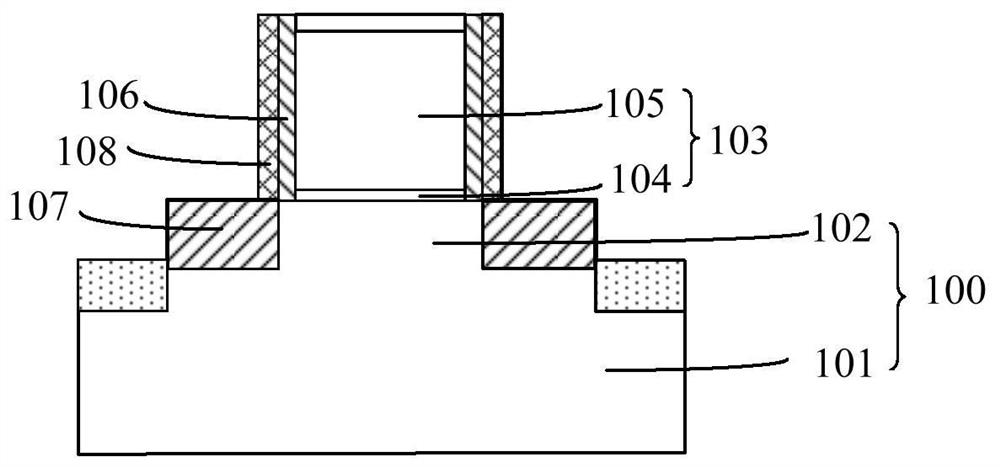

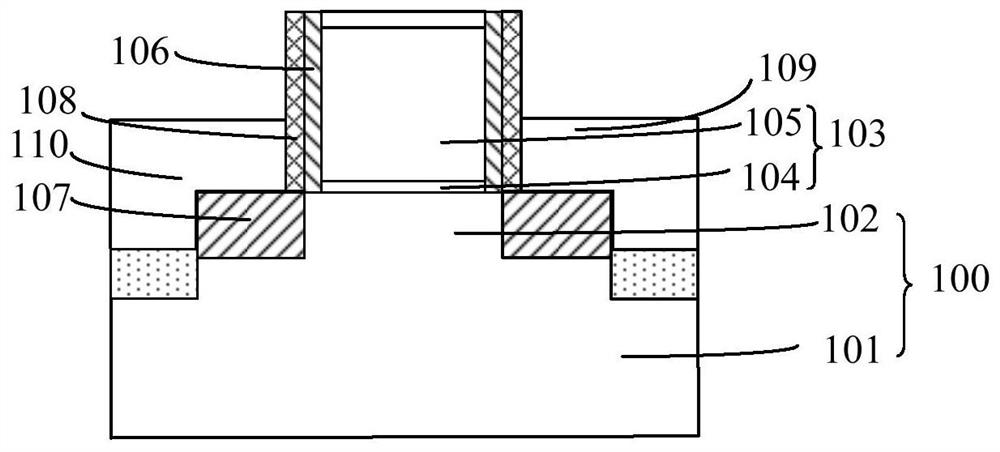

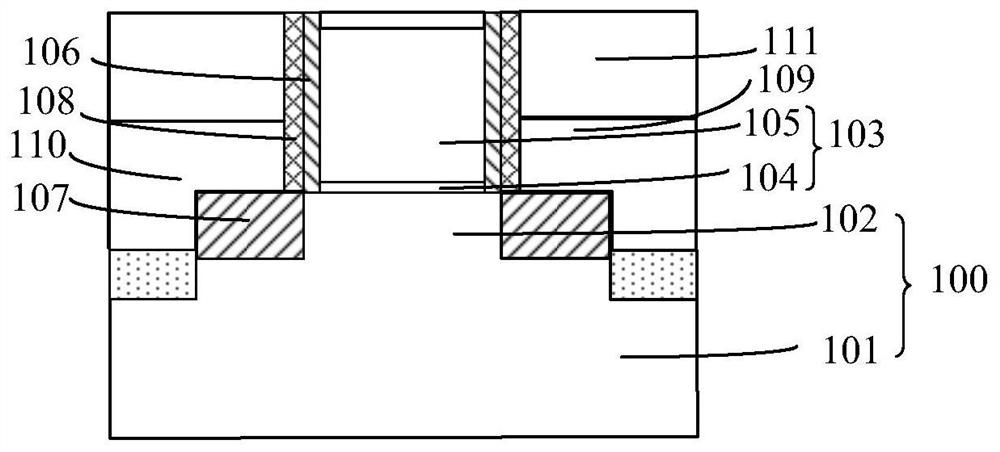

[0031] A method for forming a semiconductor device, comprising: providing a semiconductor substrate with a dummy gate structure on the semiconductor substrate, the dummy gate structure including a dummy gate dielectric layer and a dummy gate electrode layer positioned on the dummy gate dielectric layer , there are source and drain doped regions on the substrate on both sides of the dummy gate structure, and there is an interlayer dielectric layer on the source and drain doped regions and the dummy gate structure; the dummy gate electrode layer is removed until exposed On the top surface of the dummy gate dielectric layer, an opening is formed in the interlayer dielectric layer; a gate dielectric layer is formed on the sidewall of the opening and the surface of the dummy gate dielectric layer; after the gate dielectric layer is formed, the opening is I...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More