Process method for truncating polysilicon gate of fin transistor

A fin transistor and polysilicon gate technology, which is applied in the field of polysilicon gate truncation, can solve the problems of reducing product yield, polysilicon etching residue, polysilicon removal, etc., and achieves the effects of improving product yield, improving process window, and preventing polysilicon residues.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

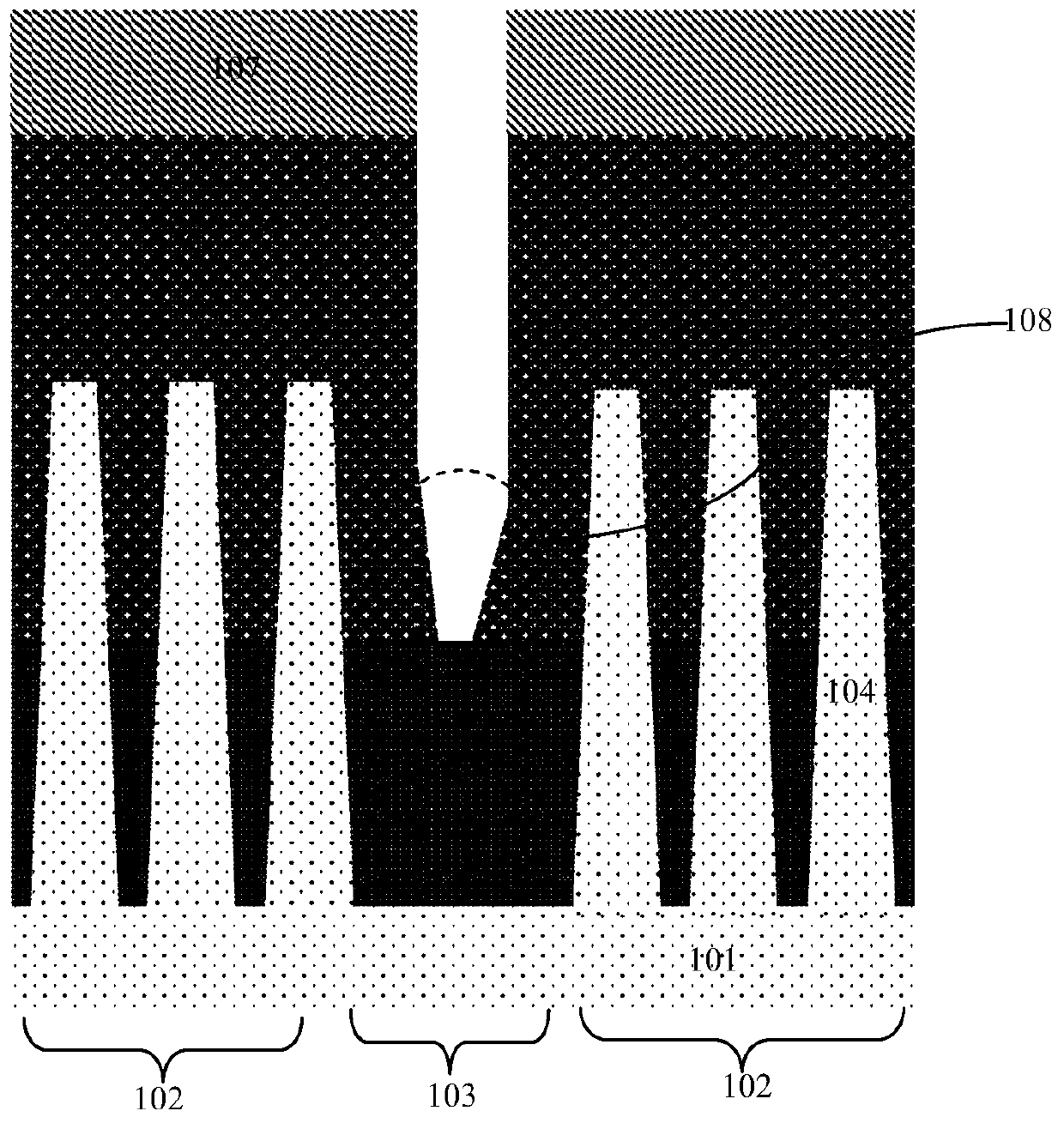

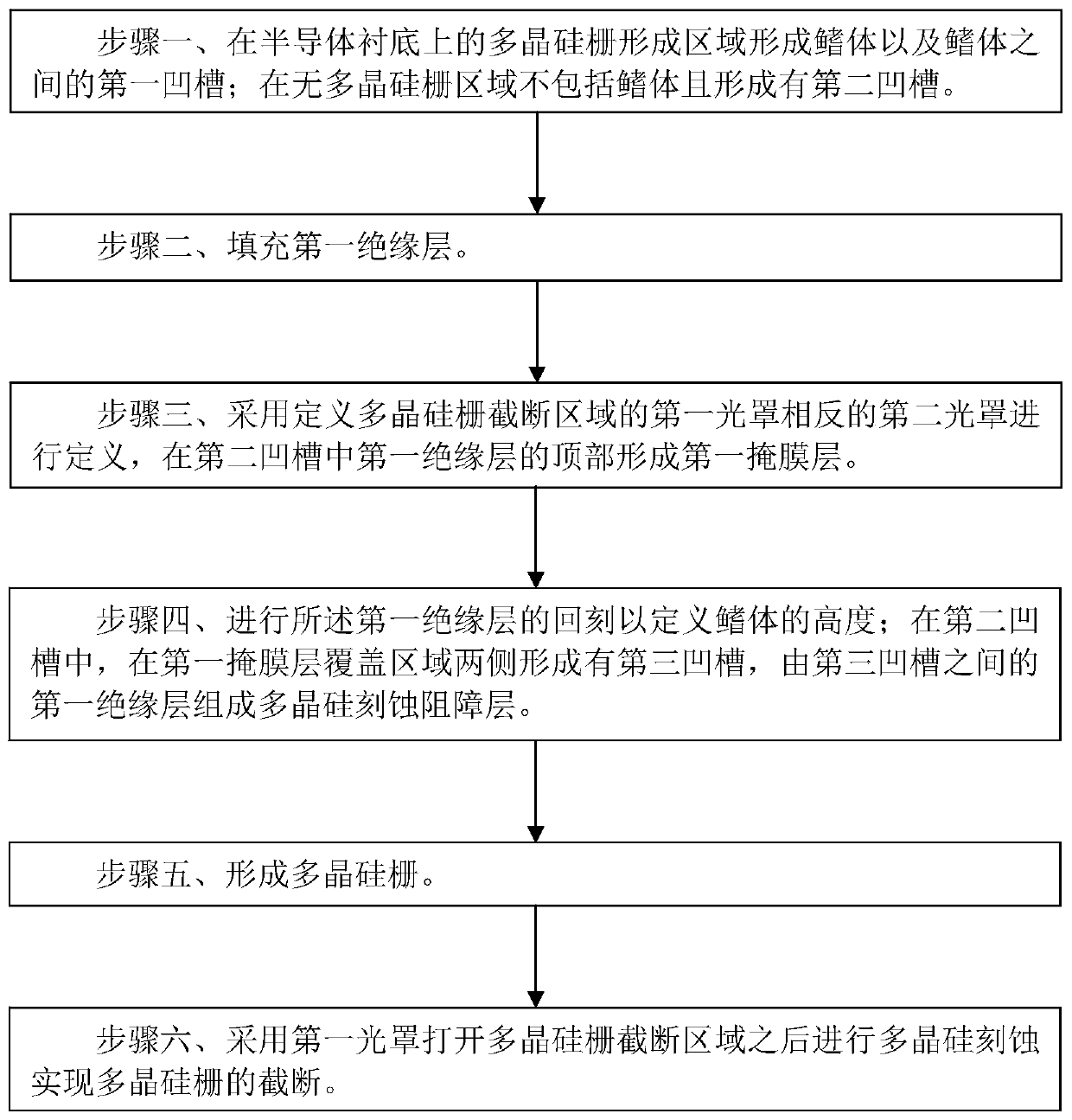

[0049] Such as figure 2 As shown, it is a flow chart of the process method of polysilicon gate truncation of the fin transistor of the embodiment of the present invention; as Figure 3A to Figure 3F As shown, it is a schematic diagram of the device structure in each step of the process method of polysilicon gate truncation of fin transistor in the embodiment of the present invention; the process method of polysilicon gate truncation of fin transistor in the embodiment of the present invention includes the following steps:

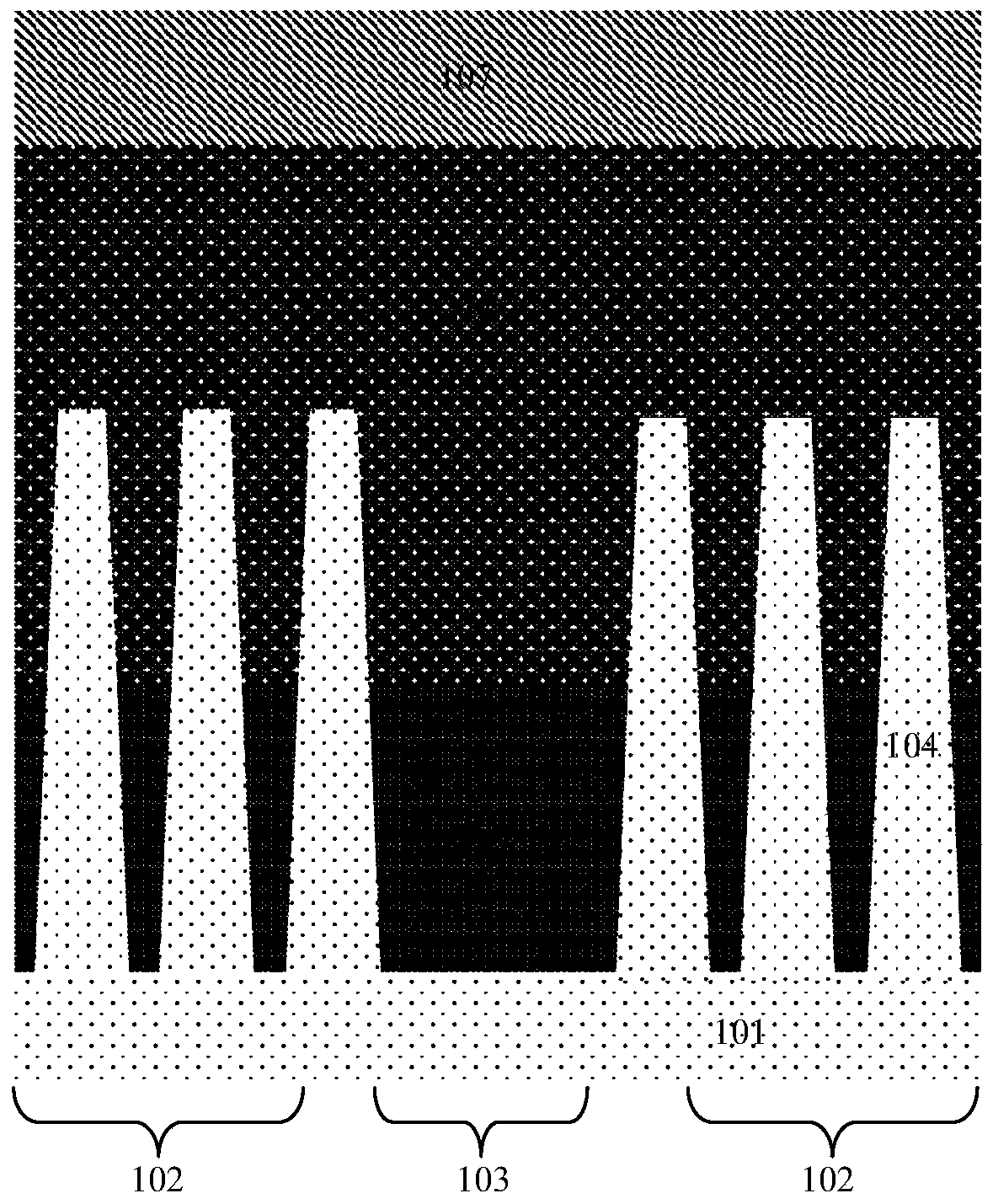

[0050] Step 1, such as Figure 3A As shown, a semiconductor substrate 1 is provided, and the semiconductor substrate 1 includes a polysilicon gate forming region 201 and a polysilicon gate-free region 202 .

[0051] A plurality of fin bodies 2 formed by etching the semiconductor substrate 1 are formed in the polysilicon gate formation region 201 , and first grooves 3 are formed between each of the fin bodies 2 . Each of the fins 2 is strip-shaped and paral...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More