Diode with NTC temperature detection and preparation method thereof

A technology of diodes and testing experiments, applied in the field of diodes, can solve problems such as chip damage, achieve the effects of reducing loss, ensuring normal operation, and improving work efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0029] This embodiment provides a method for preparing a diode with NTC temperature detection. First, the chip and the NTC are bonded together on the DCB substrate, and then the leads are bonded to both ends of the chip and the NTC, and then the internal structure of the diode is packaged. Material packaging to isolate it from the outside. After the packaging is completed, use electroplating equipment to plate metal on the leads, then cut off the excess leads, and bend the remaining leads. After the above steps are completed, the finished product is tested and tested. The preparation is completed if the test is passed. Diode with NTC temperature detection.

[0030] Beneficial effects of this embodiment: the diode made by this method is isolated from the outside because the chip and NTC are packaged together in the diode, so that the temperature of the chip detected by the NTC is more accurate, and the loss during chip operation can be reduced, improving work efficiency.

Embodiment 2

[0032] On the basis of Example 1, this example provides that the method of bonding the chip and NTC on the DCB substrate in step (a) is soldering, and the temperature range is 235°C-255°C. This example uses 235°C ℃, the adhesive material is a mixture of tin-based alloy and rosin; using this method of bonding can make the chip and NTC bonded to the DCB substrate more firmly and not easy to fall off.

Embodiment 3

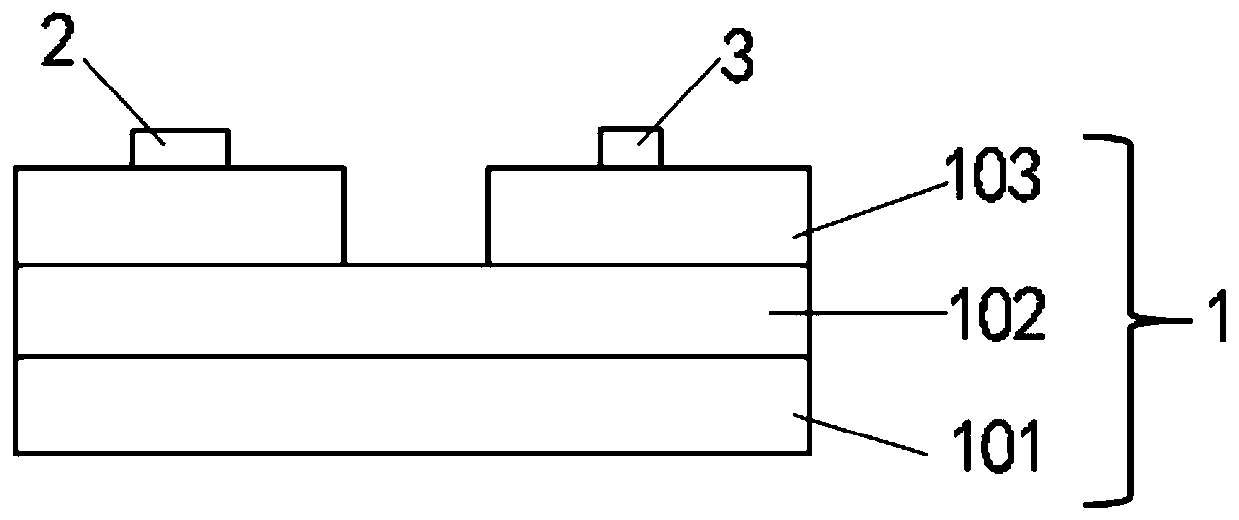

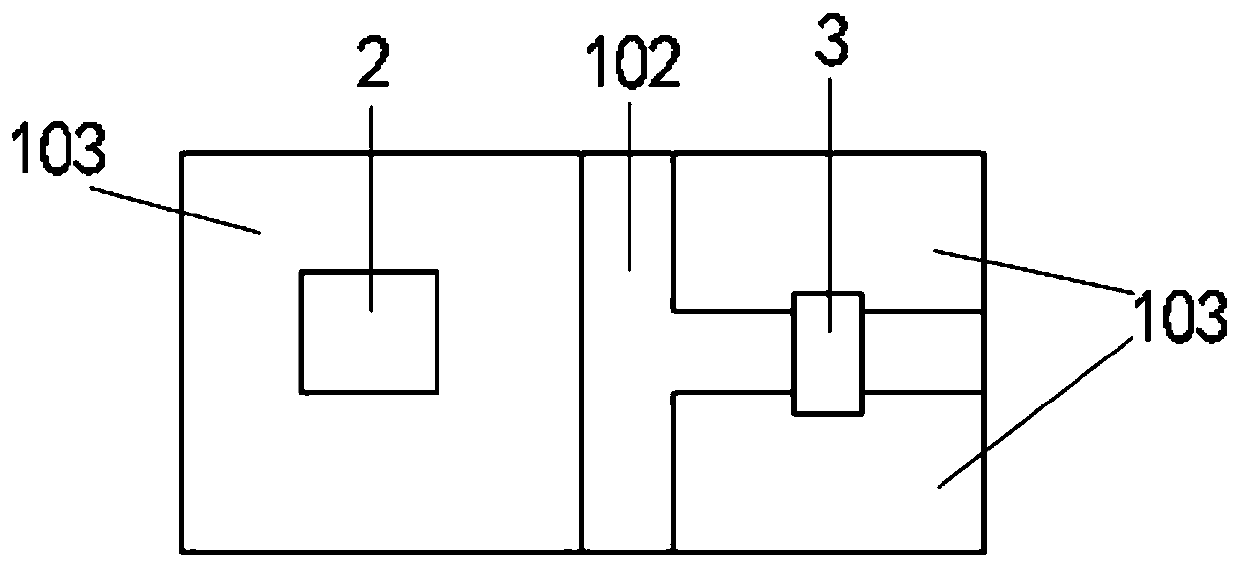

[0034] On the basis of Example 1, combined with Figure 1-2 , the material of DCB substrate 1 in the present embodiment is by top layer Cu plate 103, middle layer Al 2 o 3 The layer 102 and the bottom Cu board 101 are stacked in sequence, and the top Cu board 103 is provided with a T-shaped notch, which can prevent the short circuit of NTC3 and ensure that chip 2 and NTC3 will not communicate with each other when there is a close enough distance, thereby ensuring that NTC3 normal work.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More