Duty cycle design method, system, medium and equipment for eliminating current sampling interference

A current sampling and design method technology, applied in the field of frequency conversion control, to achieve the effect of improving precision and accuracy, accurate sampling value, and stable output

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

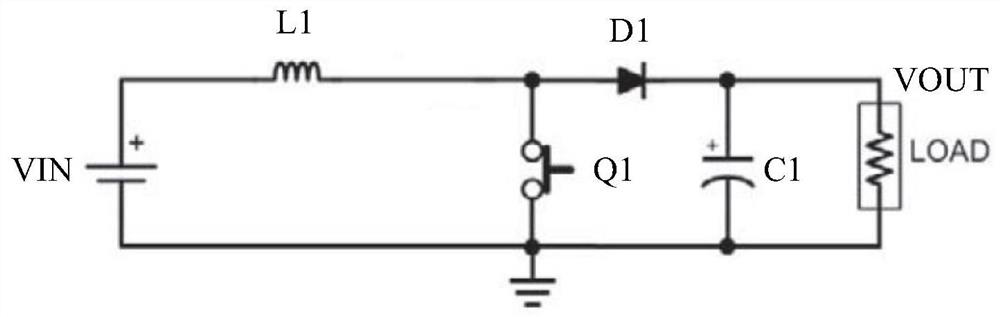

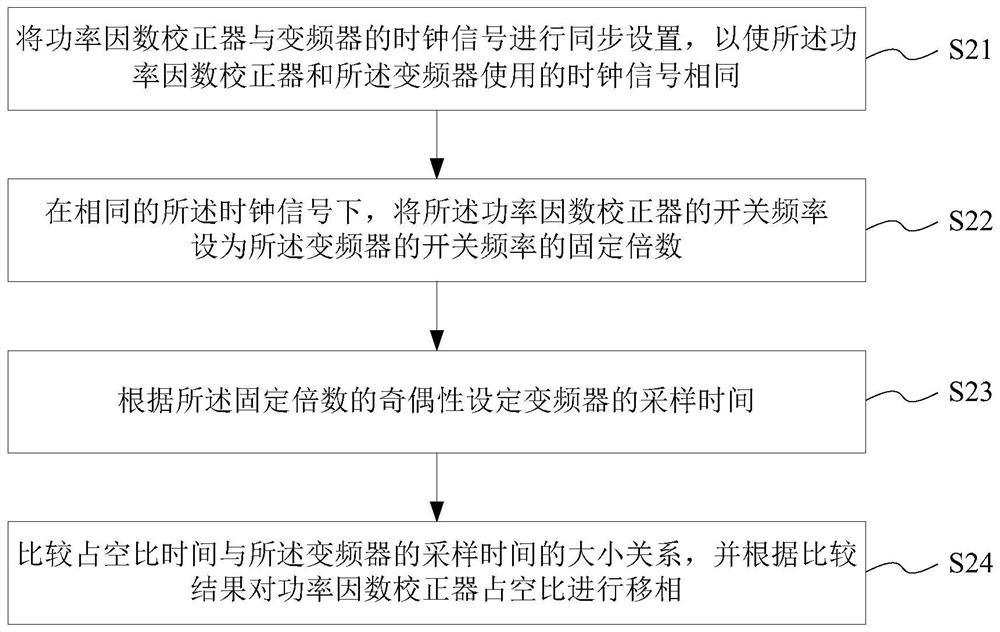

[0035] This embodiment provides a duty cycle design method for eliminating current sampling interference. The duty cycle design method for eliminating current sampling interference includes:

[0036] synchronously setting the power factor corrector and the clock signal of the frequency converter, so that the clock signals used by the power factor corrector and the frequency converter are the same;

[0037] Under the same clock signal, setting the switching frequency of the power factor corrector to a fixed multiple of the switching frequency of the frequency converter;

[0038] Setting the sampling time of the frequency converter according to the parity of the fixed multiple;

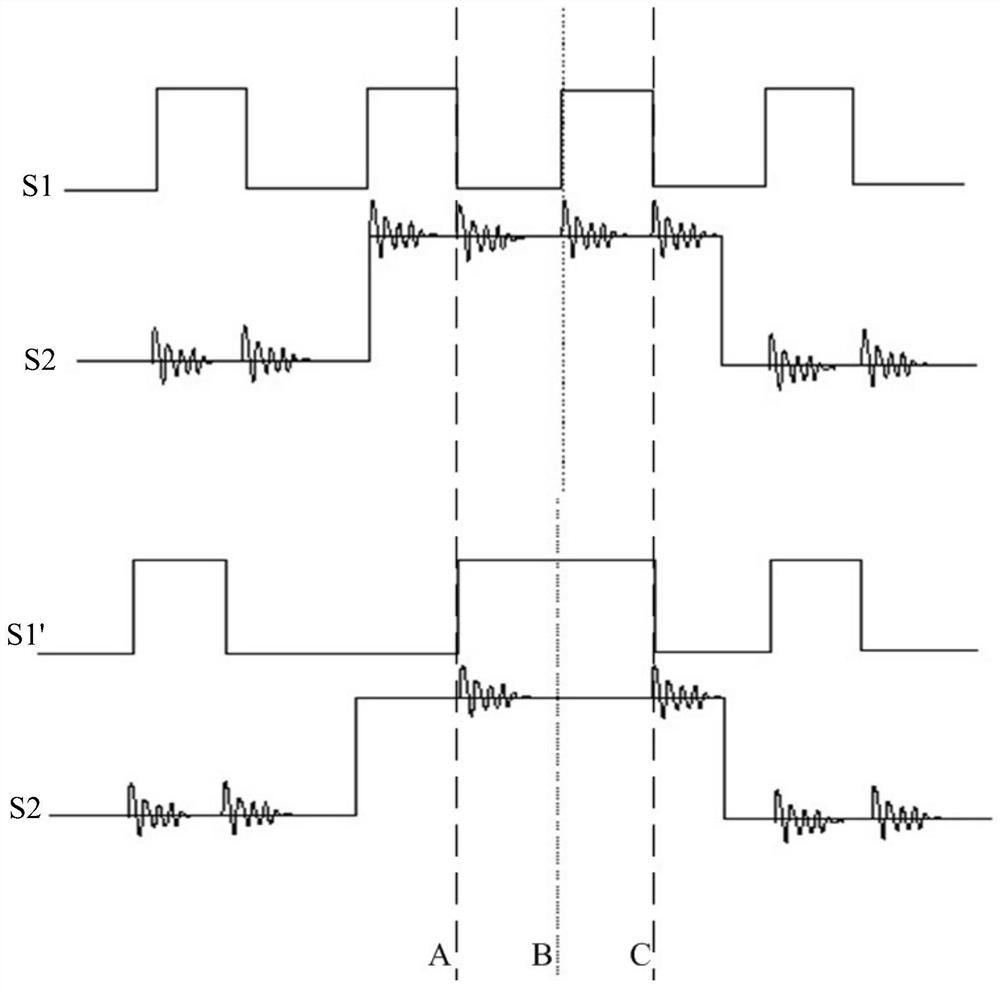

[0039] Comparing the relationship between the duty cycle time and the sampling time of the frequency converter, and phase-shifting the duty cycle of the power factor corrector according to the comparison result; the duty cycle time and the duty cycle of the power factor corrector are based on The switc...

Embodiment 2

[0063] This embodiment provides a duty cycle design system for eliminating current sampling interference. The duty cycle design system for eliminating current sampling interference includes:

[0064] A clock synchronization module, configured to synchronize the clock signals of the power factor corrector and the frequency converter, so that the clock signals used by the power factor corrector and the frequency converter are the same;

[0065]A period setting module, configured to set the switching frequency of the power factor corrector to a fixed multiple of the switching frequency of the frequency converter under the same clock signal;

[0066] The sampling time setting module is used to set the sampling time of the frequency converter according to the parity of the fixed multiple;

[0067] a phase shifting module, used to compare the relationship between the duty cycle time and the sampling time of the frequency converter, and shift the phase of the power factor corrector d...

Embodiment 3

[0081] This embodiment provides a device, including: a processor, a memory, a transceiver, a communication interface or / and a system bus; the memory and the communication interface are connected to the processor and the transceiver through the system bus and complete mutual communication, and the memory is used for The computer program is stored, the communication interface is used to communicate with other devices, the processor and the transceiver are used to run the computer program, so that the device executes each step of the duty cycle design method for eliminating current sampling interference.

[0082] Specifically, the device includes: a processor, a memory, a transceiver, a communication interface or / and a system bus; the memory and the communication interface are connected to the processor and the transceiver through the system bus and complete mutual communication, and the memory is used to store the The program, the communication interface are used to communicate w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More