A kind of tunneling field effect transistor and its preparation method

A tunneling field effect, transistor technology, applied in semiconductor/solid-state device manufacturing, diodes, semiconductor devices, etc., can solve the problems of bipolar parasitic current and low on-state drive current, improve on-state drive current, suppress dual Extreme parasitic current phenomenon, effect of improving subthreshold slope

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

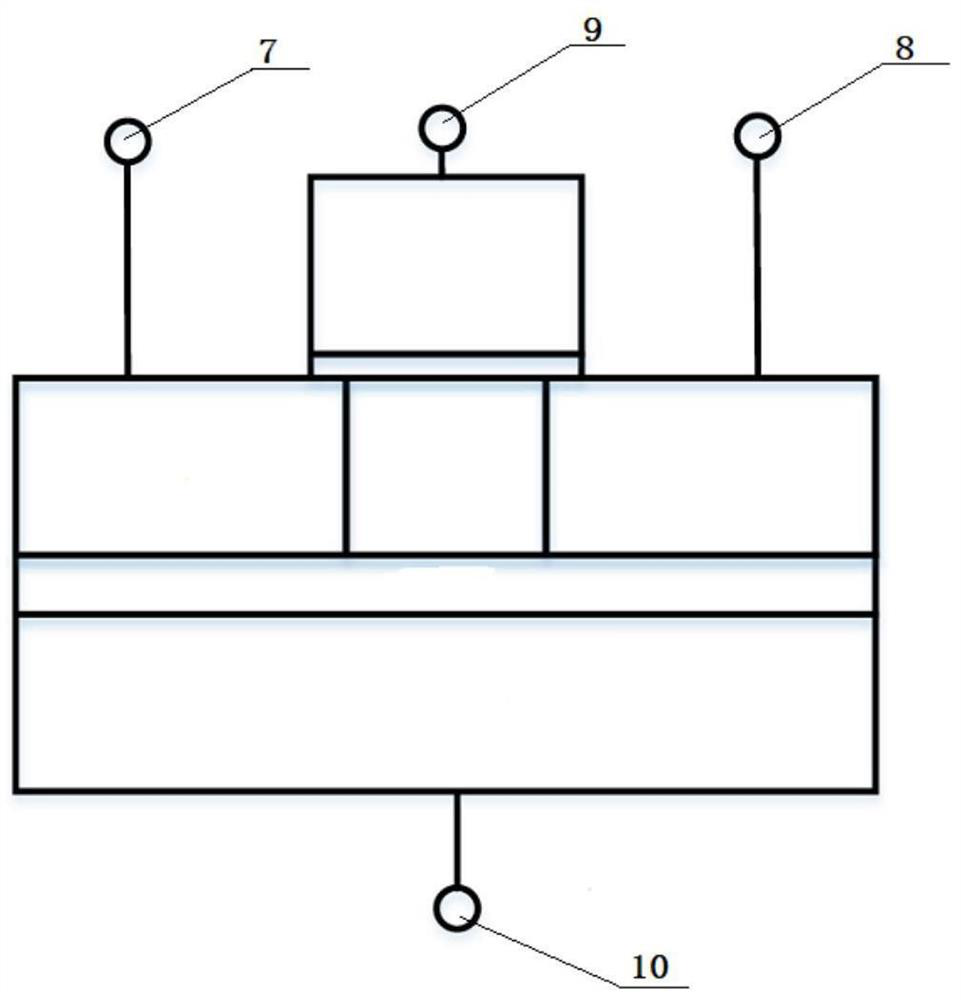

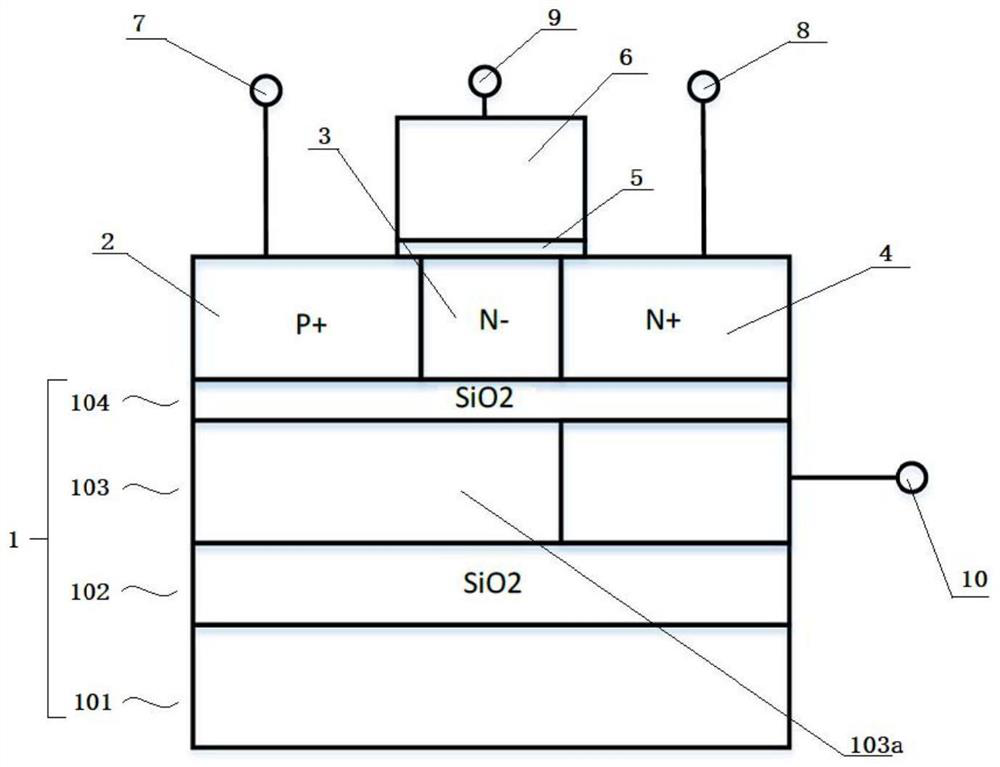

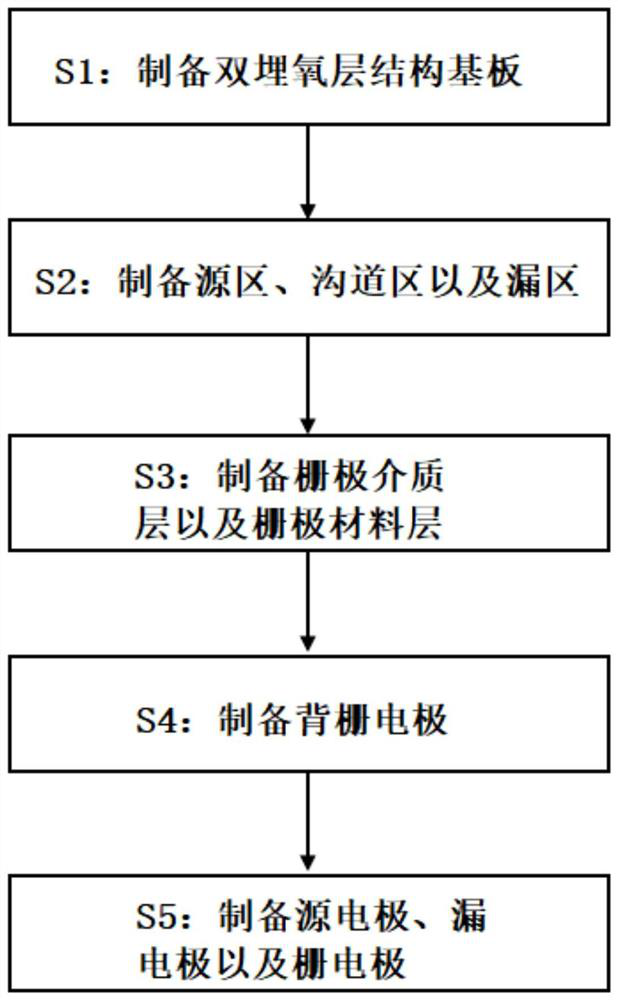

[0048] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the drawings in the embodiments of the present invention. Apparently, the described embodiments are only some of the embodiments of the present invention, but not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

[0049]Reference herein to "one embodiment" or "an embodiment" refers to a particular feature, structure or characteristic that can be included in at least one implementation of the present invention. In the description of the present invention, it should be understood that the orientation or positional relationship indicated by the terms "upper", "lower", "top", "bottom" etc. is based on the orientation or positional relationship shown in the drawings, a...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More