Fault Diagnosis Model of Analog Circuit Based on Algebraic Method

A technology for simulating circuit faults and fault diagnosis models, applied in analog circuit testing, electronic circuit testing, etc., can solve problems such as long fault diagnosis time, increased cost, inaccurate fault detection, etc., achieve less online calculation time and lower test requirements Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0075] In order to make the purpose, technical solutions and advantages of the present invention clearer, the technical solutions in the present invention are clearly and completely described below. Apparently, the described embodiments are part of the embodiments of the present invention, not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

[0076] The present invention will be further described below in conjunction with accompanying drawing:

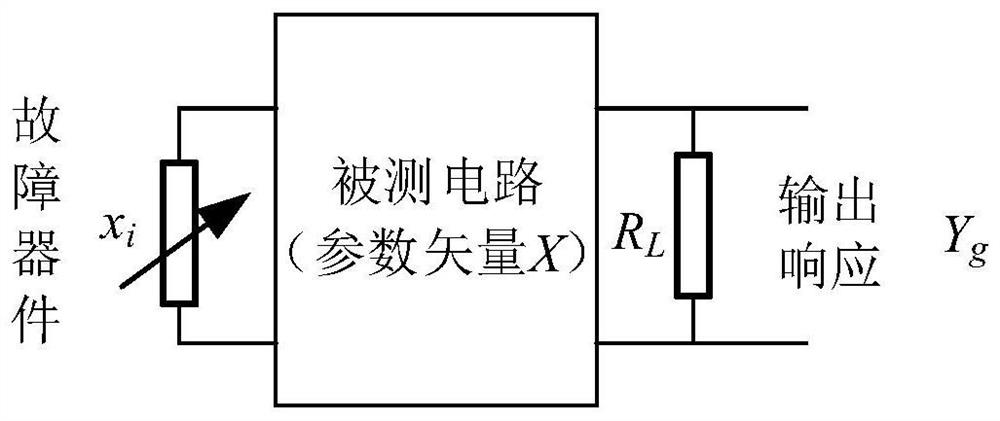

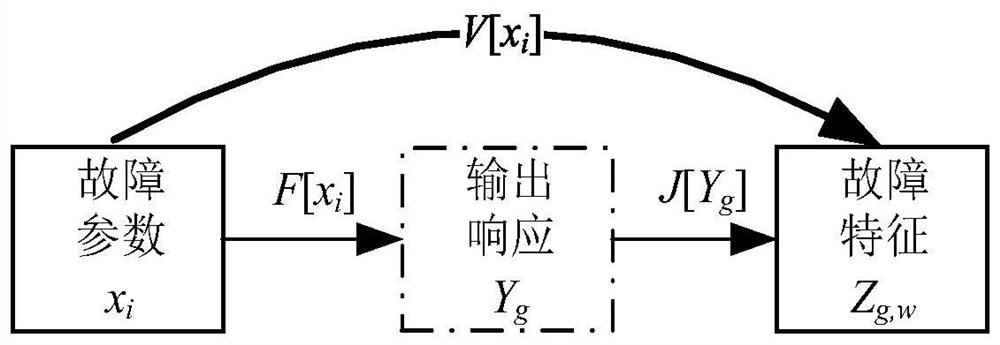

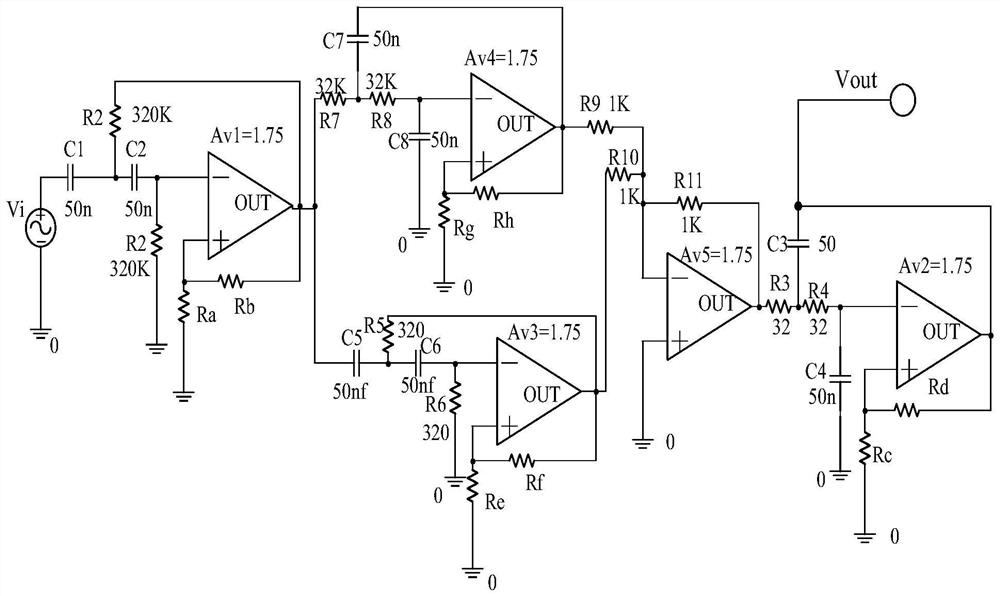

[0077] Refer to attached figure 1 - attached Figure 7, the present invention establishes the basic theory of failure model as follows:

[0078] Considering that the impact of circuit failure is that the output response does not meet the ideal requirements, that is, the output response deviates from the normal response, in order to avoid the established fault diagno...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More