Static random access memory based on back gate structure of FDSOI device

A static random access and memory technology, applied in static memory, digital memory information, information storage, etc., can solve the problem of reducing the yield of SRAM

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

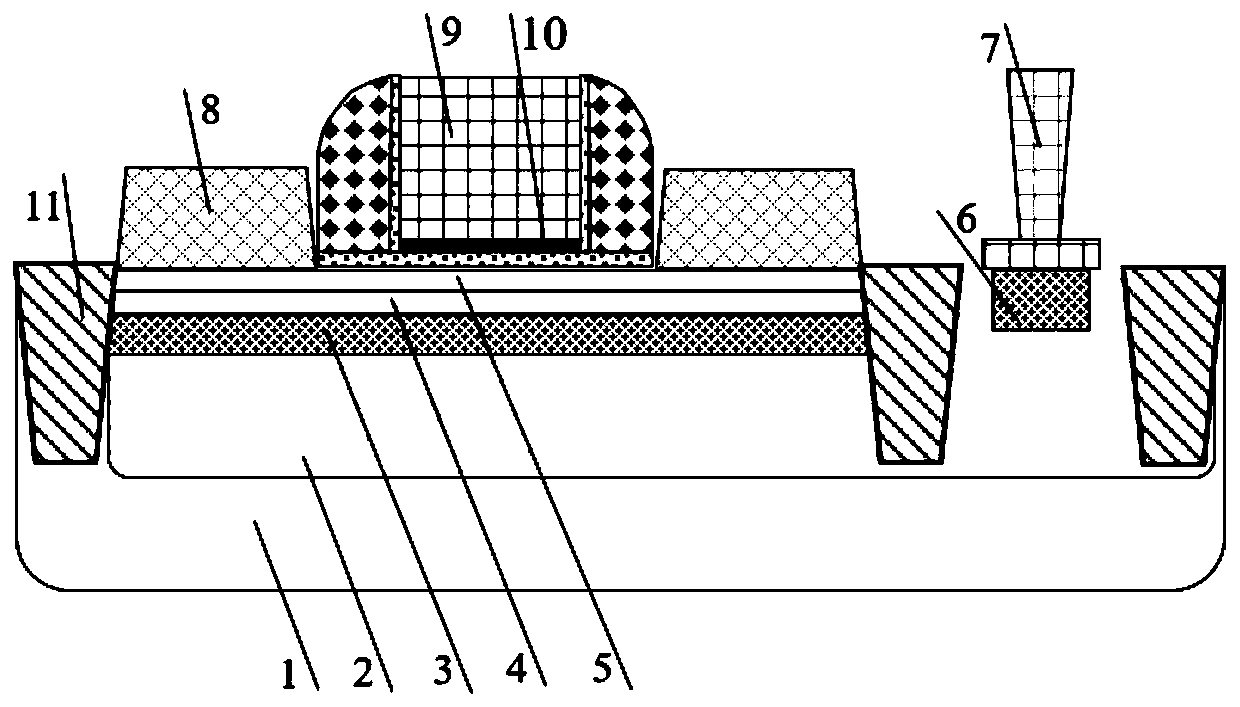

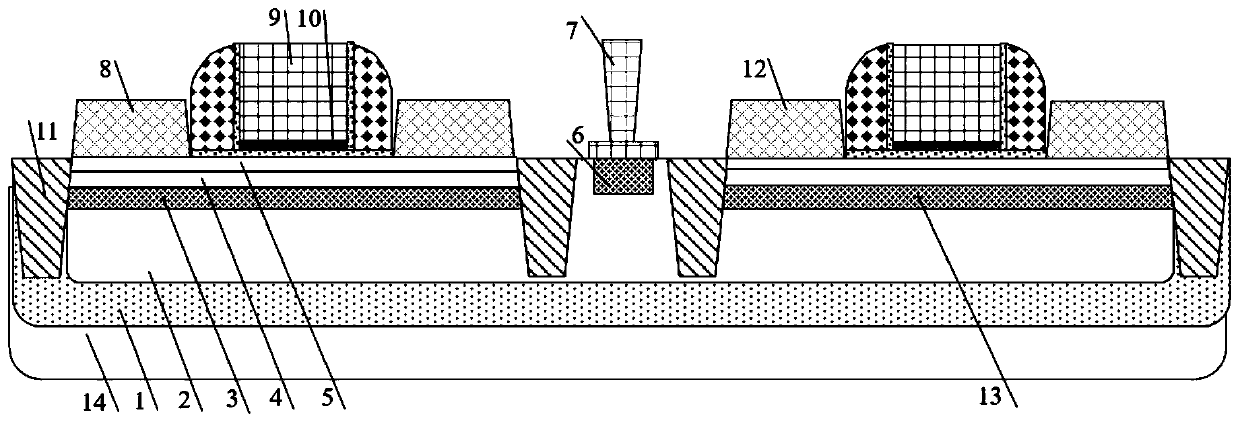

[0027] The present invention will be described in detail below in conjunction with the accompanying drawings and embodiments.

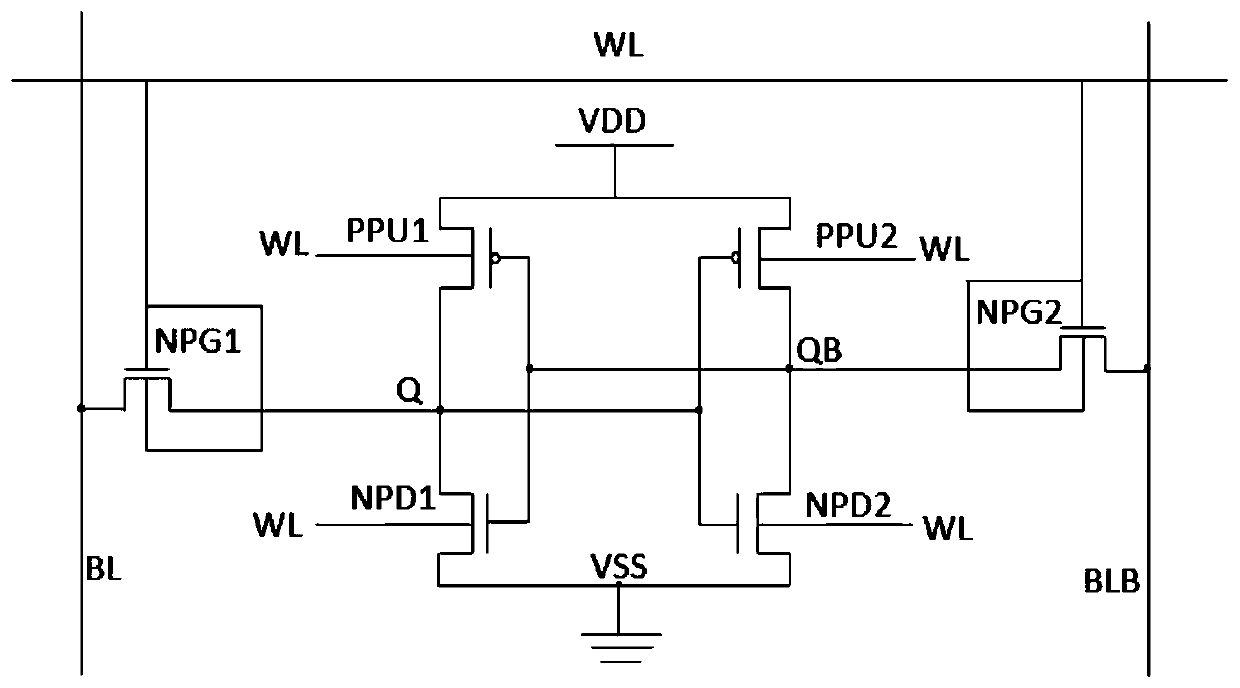

[0028] refer to figure 1 , the static random access memory of the present invention comprises:

[0029] The first pull-up transistor PPU1, the second pull-up transistor PPU2, the first pass transistor NPG1, the second pass transistor NPG2, the first pull-down transistor NPD1 and the second pull-down transistor NPD2, the first pull-up transistor PPU1, the second The pull-up transistor PPU2, the first pass transistor NPG1, the second pass transistor NPG2, the first pull-down transistor NPD1 and the second pull-down transistor NPD2 are FDSOI devices; the first pull-up transistor PPU1 and the first pull-down transistor NPD1 constitute the first An inverter, the second pull-up transistor PPU2 and the second pull-down transistor NPD2 form a second inverter;

[0030] The output terminal of the first inverter forms a first storage node Q, the output termina...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More