Semiconductor structure and forming method thereof

A semiconductor and gate structure technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problem of reducing the breakdown voltage of contact hole plugs and gate structures, and poor electrical performance of semiconductor structures Influence and other issues, to achieve the effect of improving electrical performance, reducing contact resistance, and increasing breakdown voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] The devices formed so far still suffer from poor performance. Now combined with a method of forming a semiconductor structure, the reasons for the poor performance of the device are analyzed.

[0014] refer to Figure 1 to Figure 4 , a schematic diagram of the structure corresponding to each step in a method for forming a semiconductor structure is shown.

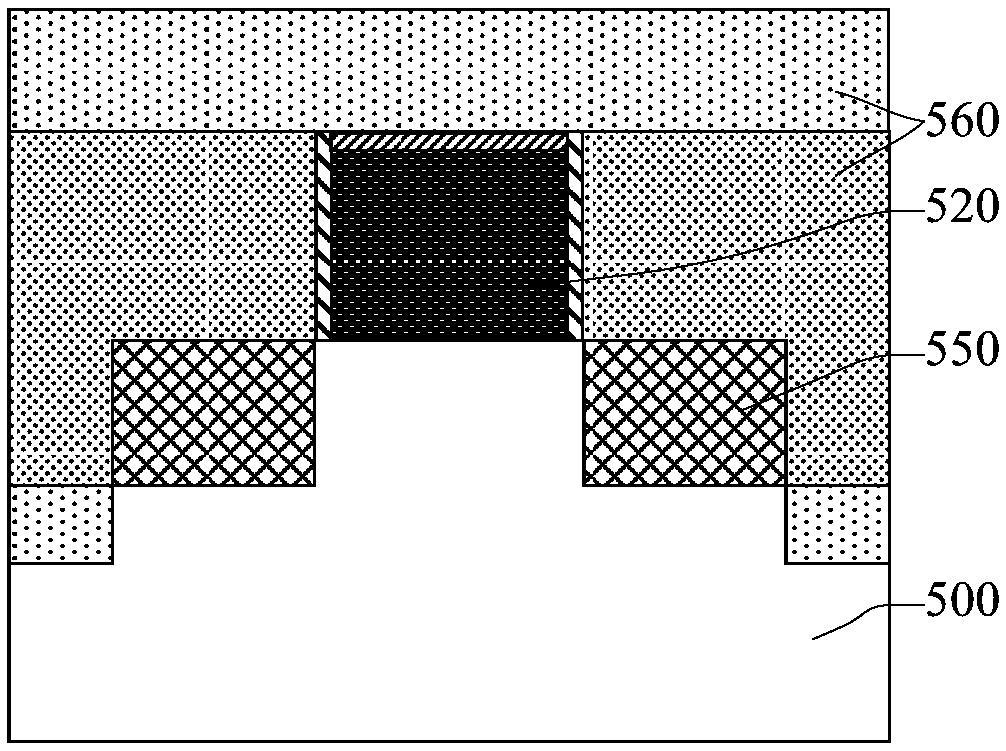

[0015] refer to figure 1 , a substrate 500 is provided, a gate structure 520 is formed on the substrate 500, a source-drain doped layer 550 is formed in the substrate 500 on both sides of the gate structure 520, and the gate structure 520 is formed on the substrate 500 exposed There is a dielectric layer 560 covering the top of the gate structure 520 .

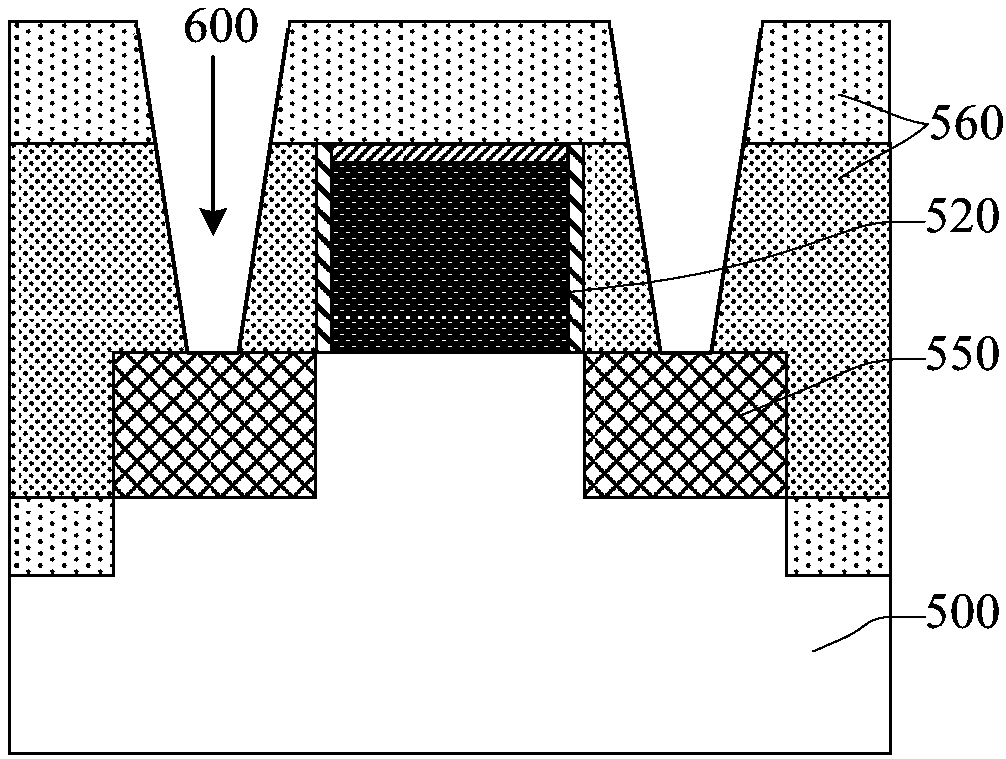

[0016] refer to figure 2 , a contact hole 600 is formed in the dielectric layer 560 on both sides of the gate structure 520 , and the contact hole 600 exposes the top of the source-drain doped layer 550 .

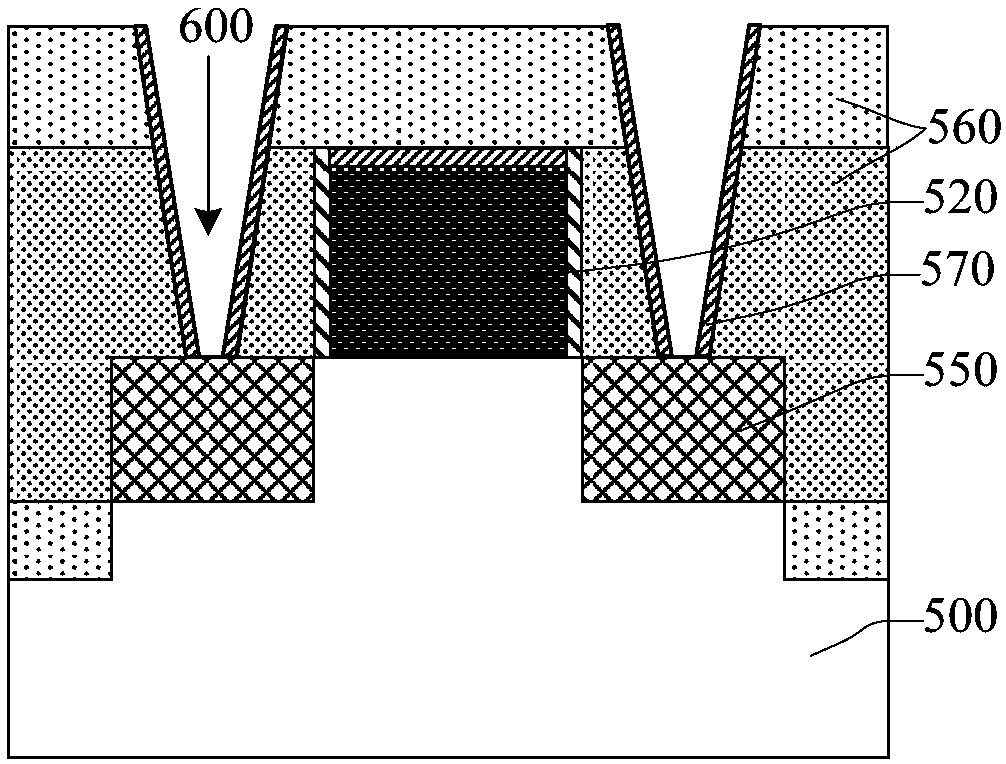

[0017] refer to image 3 , and a sidewall layer 570 i...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com