Successive approximation type analog-to-digital converter with capacitance mismatch correction function

A successive approximation, analog-to-digital converter technology, applied in the direction of analog/digital conversion, analog/digital conversion calibration/test, code conversion, etc., can solve the problem of high hardware overhead of digital circuits, increased circuit area and power consumption, and algorithm Convergence and other issues, to simplify the design process, reduce area and complexity, simple and reliable digital circuit

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

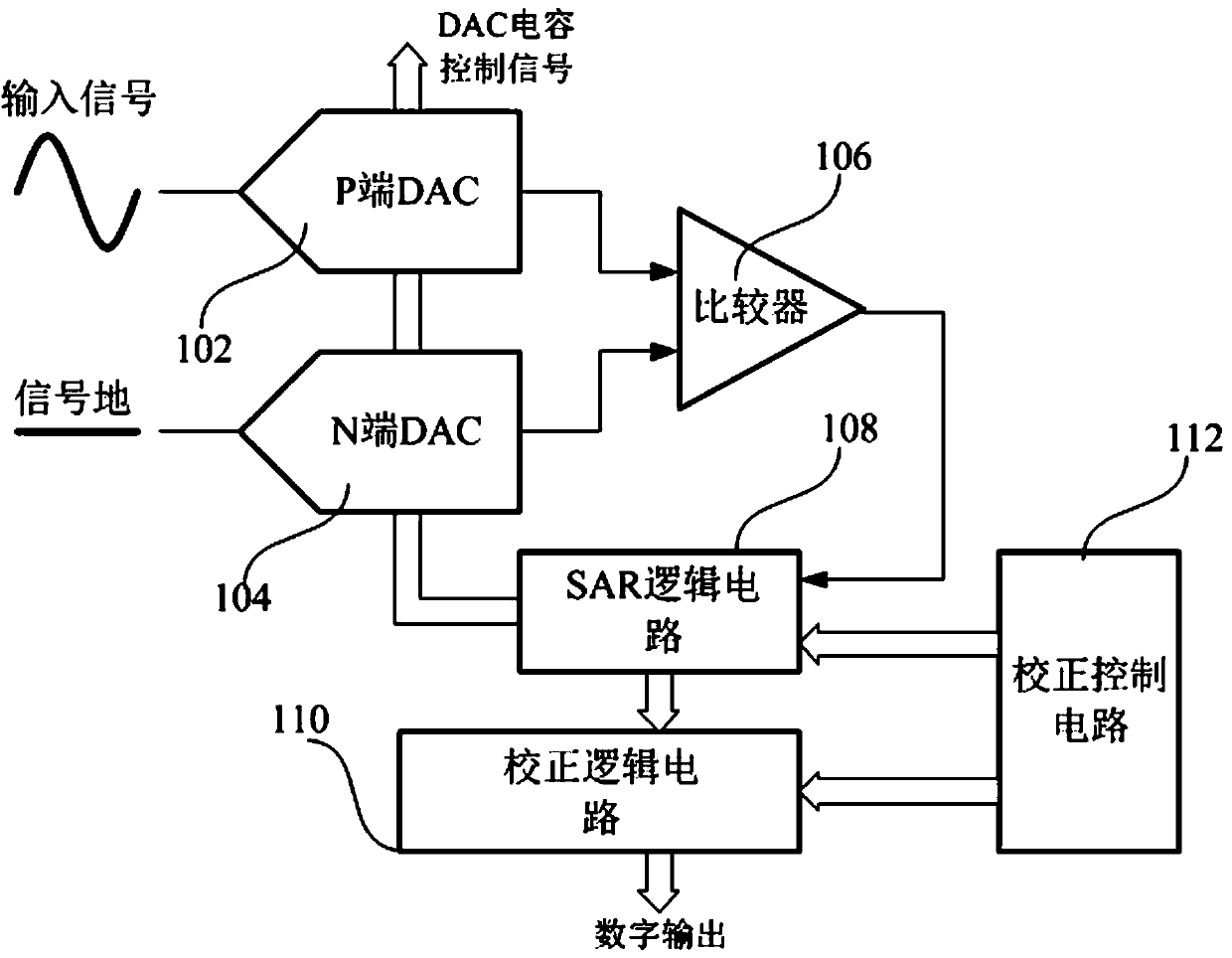

[0053] The present invention designs a successive approximation analog-to-digital converter with capacitance mismatch correction function, such as Figure 1~3 As shown, the following setting method is adopted in particular: a P-terminal DAC102, an N-terminal DAC104, a comparator 106, a SAR logic circuit 108, a correction logic circuit 110 and a correction control circuit 112 are provided, and the output terminal of the P-terminal DAC102 and the N-terminal The output end of DAC104 connects two input ends of comparator 106 respectively, and the output connection of comparator 106 connects SAR logic circuit 108, and SAR logic circuit 108 controls and connects P end DAC102, N end DAC104 and correction logic circuit 110, correction control circuit 112 The control is connected to the SAR logic circuit 108 and the correction logic circuit 110 ; the analog input signal is input on the P-terminal DAC102 , and the signal ground is connected to the N-terminal DAC104 .

[0054] As a prefe...

Embodiment 2

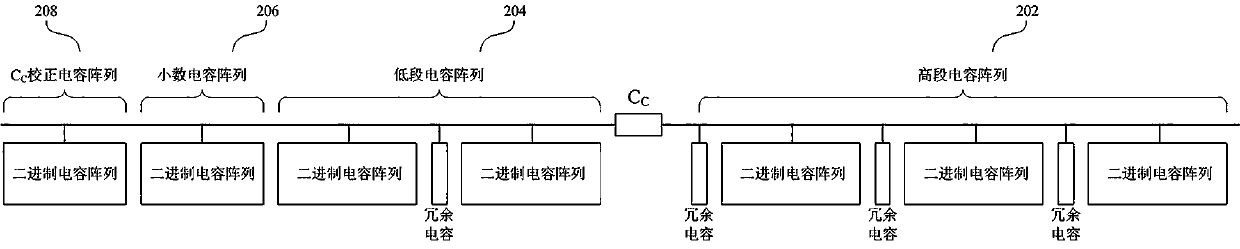

[0056] This embodiment is further optimized on the basis of the above embodiments, such as Figure 1~3 As shown, the same parts as the aforementioned technical solutions will not be repeated here. Further, in order to better realize the present invention, the following setting method is adopted in particular: the P-terminal DAC102 and the N-terminal DAC104 adopt the same DAC circuit structure, And the DAC circuit structure includes a high segment capacitor array 202, a low segment capacitor array 204, a fractional capacitor array 206 and a C C correction capacitor array 208, the C C The correction capacitor array 208 is connected to the fractional capacitor array 206, and the fractional capacitor array 206 is connected to the low segment capacitor array 204, and the capacitor C is passed between the high segment capacitor array 202 and the low segment capacitor array 204. C Coupling; at least one binary capacitor array is set in the high segment capacitor array 202 and the lo...

Embodiment 3

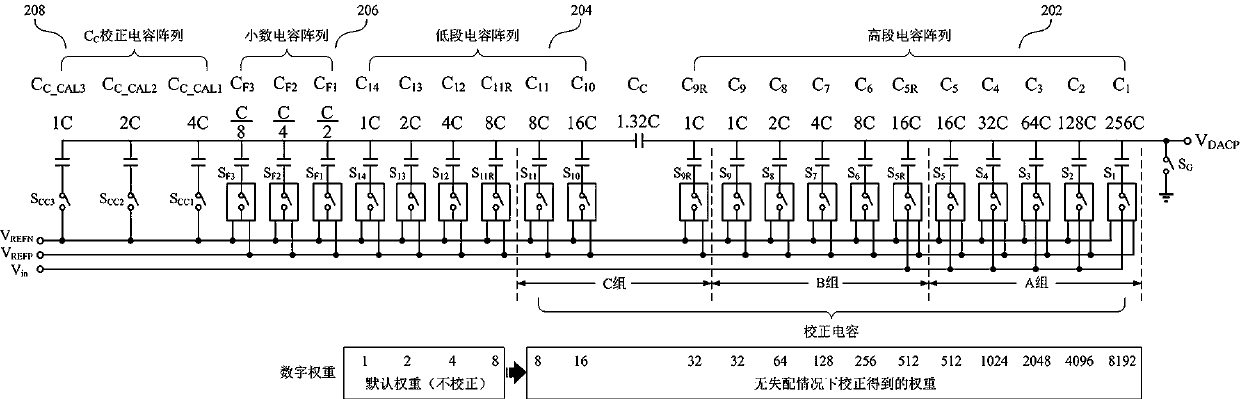

[0059] This embodiment is further optimized on the basis of any of the above embodiments, such as image 3 As shown, the same part as the foregoing technical solution will not be repeated here. In this embodiment, a binary 14-bit DAC (P-terminal DAC 102 or N-terminal DAC 104) with a redundant structure is used as an example as an example. The DAC structure By the high segment capacitor array 202, the low segment capacitor array 204, the decimal capacitor array 206 and C C The correction capacitor array 208 is composed of a capacitor C between the high segment capacitor array 202 and the low segment capacitor array 204 C for coupling. The high-segment capacitor array 202 is composed of 11 capacitors, which are respectively C 1 ~C 5 、C 5R 、C 6 ~C 9 and C 9R . where C 1 is the highest capacitance of the high-segment capacitance array 202, and is also the MSB capacitance of the entire SAR_ADC, C 9 is the lowest bit capacitance of the high-segment capacitance array 202, C...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com