Universal chip test system and test method and storage medium

A chip test and chip technology, applied in the field of chip verification and testing, can solve the problems of slow construction of chip test systems and inability to share test hardware resources, so as to facilitate the rapid establishment of test systems, improve construction efficiency, and improve test efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

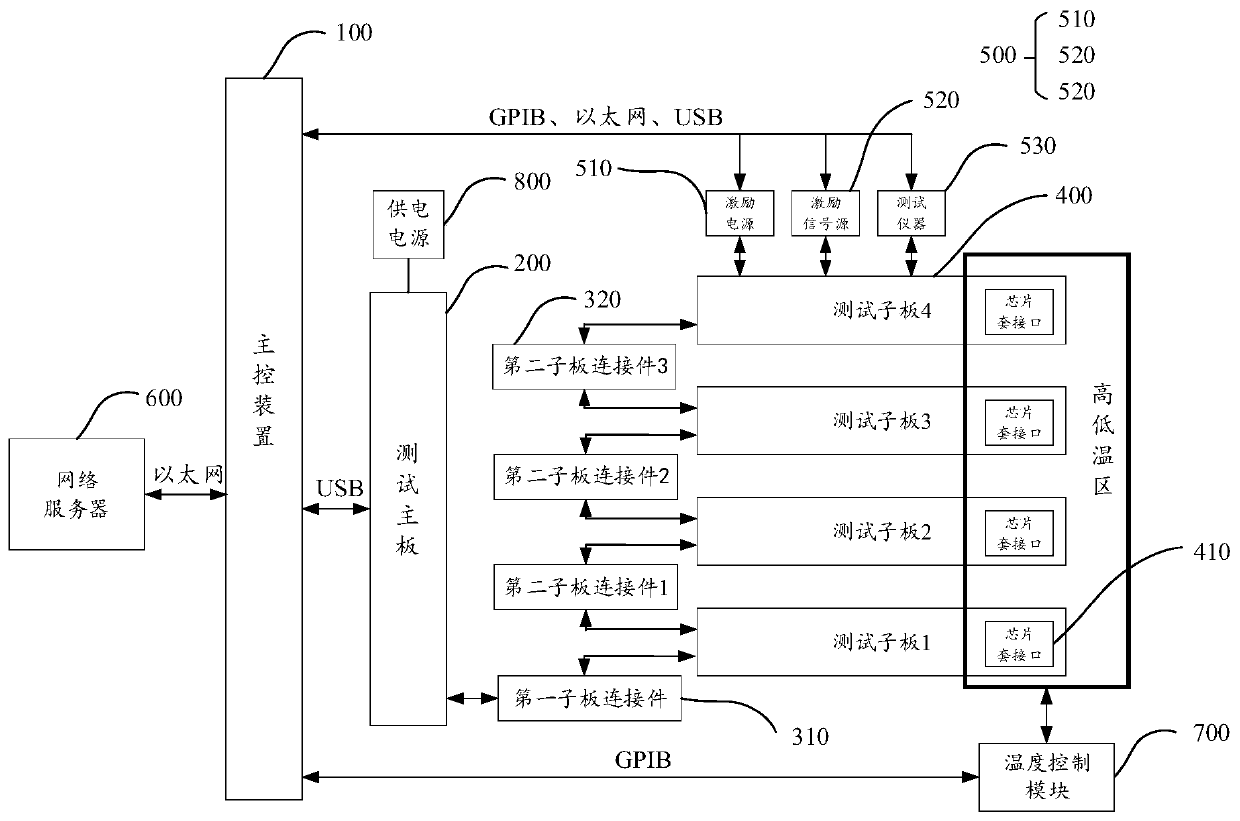

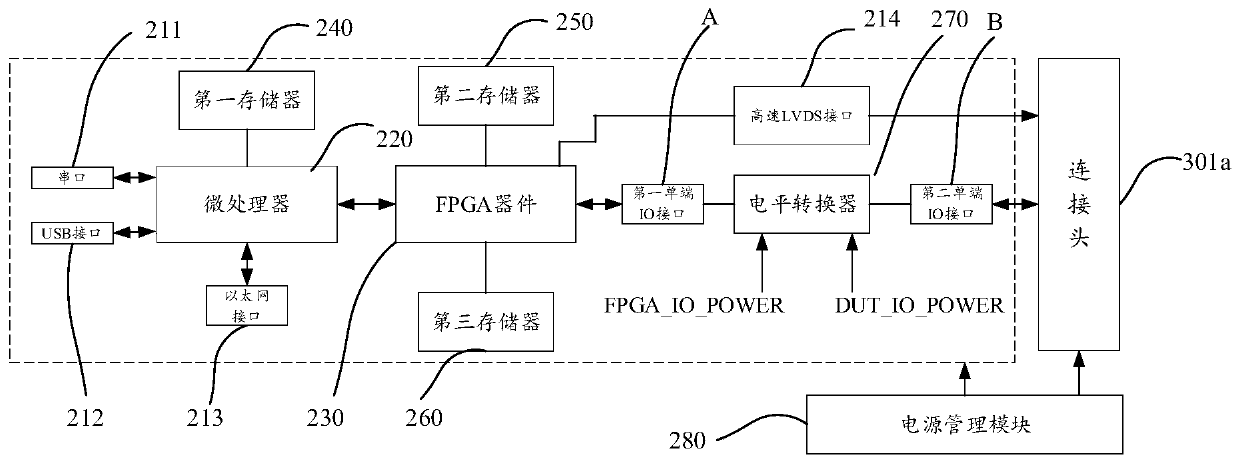

[0080] This embodiment provides a general chip test system, as attached figure 1 As shown, it includes a main control device 100 , a test main board 200 , N sub-board connectors 300 , several test sub-boards 400 and several test suites 500 , where N≥1. In particular, for ease of understanding and illustration, N=4, obviously, this is not a limitation of the present invention.

[0081] The main control device 100 is respectively connected to the test main board 200 and several test suites 500, and the N sub-board connectors include a first sub-board connector 310 and N-1 second sub-board connectors. 320, the test main board 200 is connected to the test sub-board 400 through the first sub-board connector 310, the test sub-boards 400 are connected through the second sub-board connector 320, and the first Signals are communicated between a sub-board connector 310 and the second sub-board connector 320 and between the second sub-board connectors 320 . The test sub-board 400 is co...

Embodiment 2

[0112] Based on a general chip testing system provided by any of the above implementations, the embodiment of the present invention provides a general chip testing method, see the attached Figure 9 , including the following steps,

[0113] S100: Receive test configuration information.

[0114] S200: Convert the test configuration information into incentive instructions and test instructions.

[0115] S300: According to the test stimulus, control the test main board, the test sub-board and the chip to be tested to execute the test instruction.

[0116] Preferably, before step S100, the following steps are also included, according to the test configuration information, connecting the test main board and the test suite with the main control device; connecting the test sub-board with the sub-board connector, and connecting the sub-board The board is connected with the test main board; the test suite is connected with the test sub-board, and the chip to be tested is fixed on the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More