Manufacturing method of self-aligned contact hole and manufacturing method of semiconductor device

A technology of self-aligned contact holes and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as short circuit, uncontrollable contact hole shape, device failure, etc., to achieve The effect of large process window, improved product competitiveness, and small chip area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0063] The technical solutions proposed by the present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments. The advantages and features of the present invention will become clearer from the following description. It should be noted that all the drawings are in a very simplified form and use imprecise scales, and are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention. In this article, the meaning of "and / or" is to choose one or both.

[0064] Please refer to Figure 4 , an embodiment of the present invention provides a method for manufacturing a self-aligned contact hole, comprising the following steps:

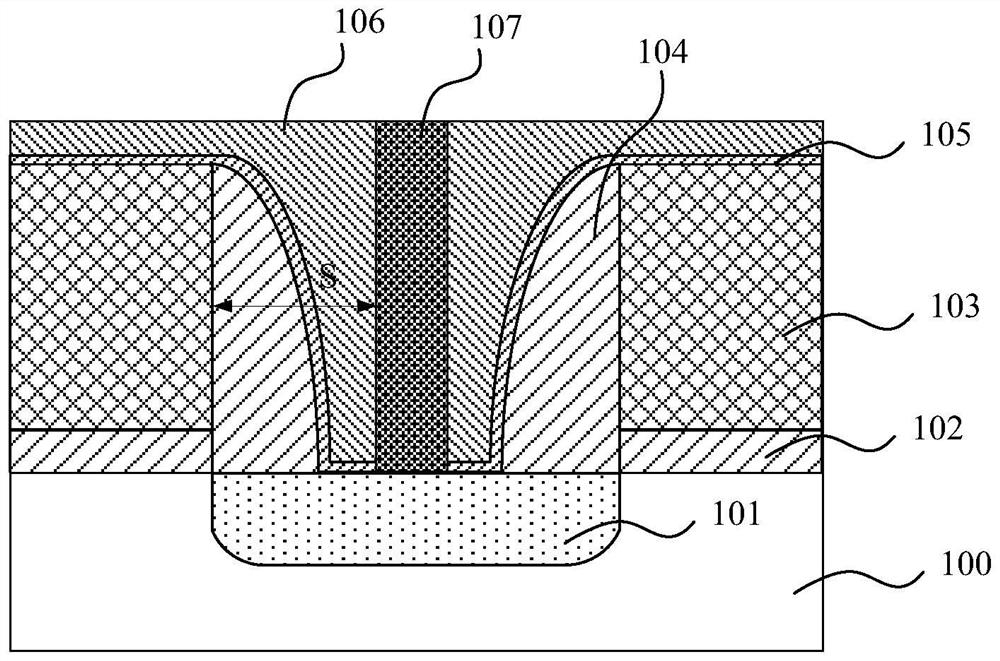

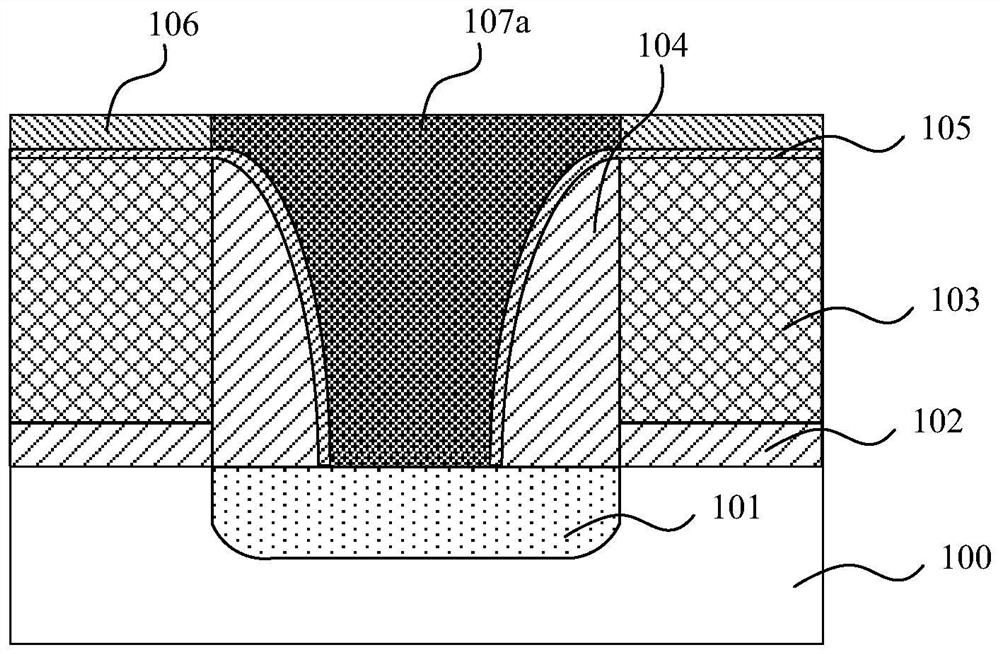

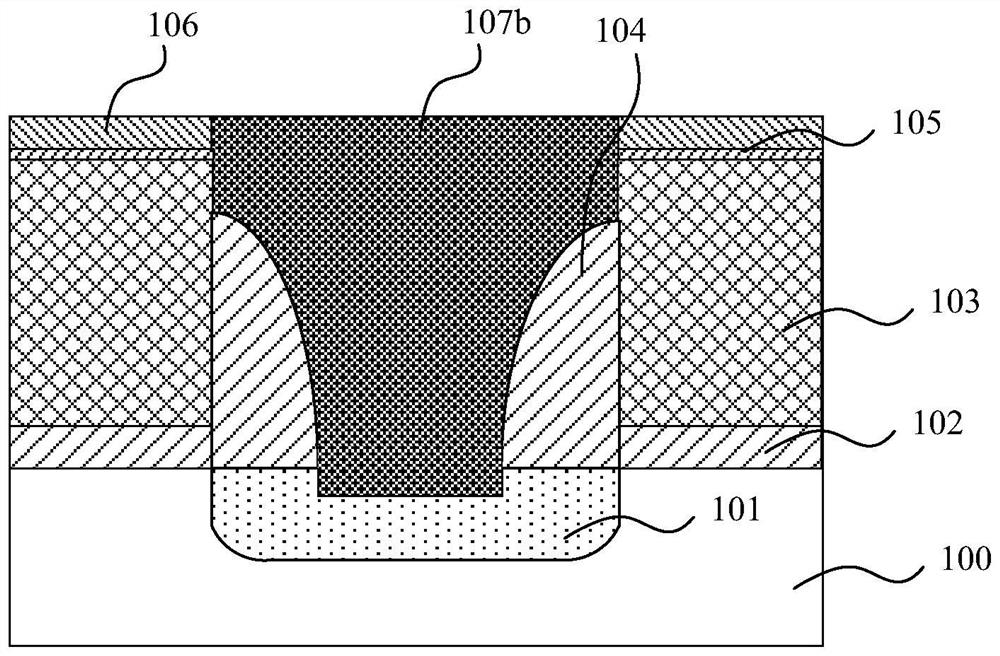

[0065] S1, providing a substrate, on which a plurality of gate stack structures and sidewalls located on both sides of each gate stack structure are formed, and trenches are formed between sidewalls on opposite sides of adjacent gate stack struc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More