Multi-phase multi-duty-ratio clock generation circuit

A technology of clock generation circuit and duty cycle, applied in the direction of electric pulse generation, multiple input and output pulse circuits, pulse generation, etc., can solve the problem of single duty cycle output state, limited operating frequency range, low maximum operating frequency, etc. problem, achieve the effect of overcoming poor frequency characteristics, good common mode noise suppression ability, and good matching characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

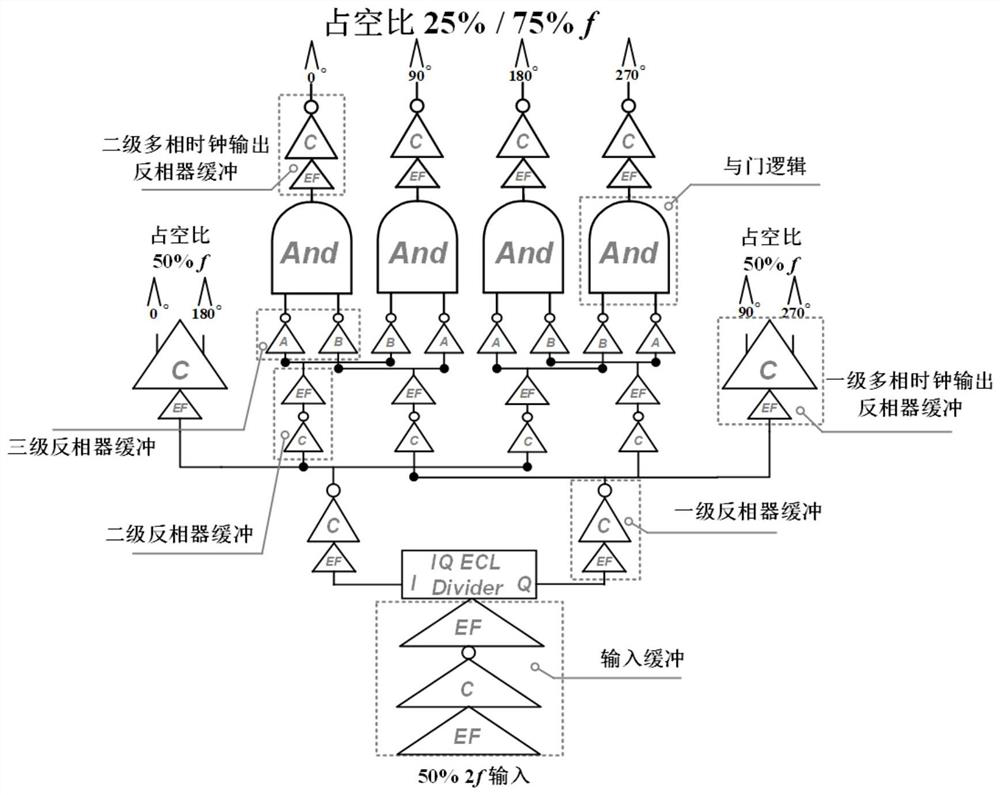

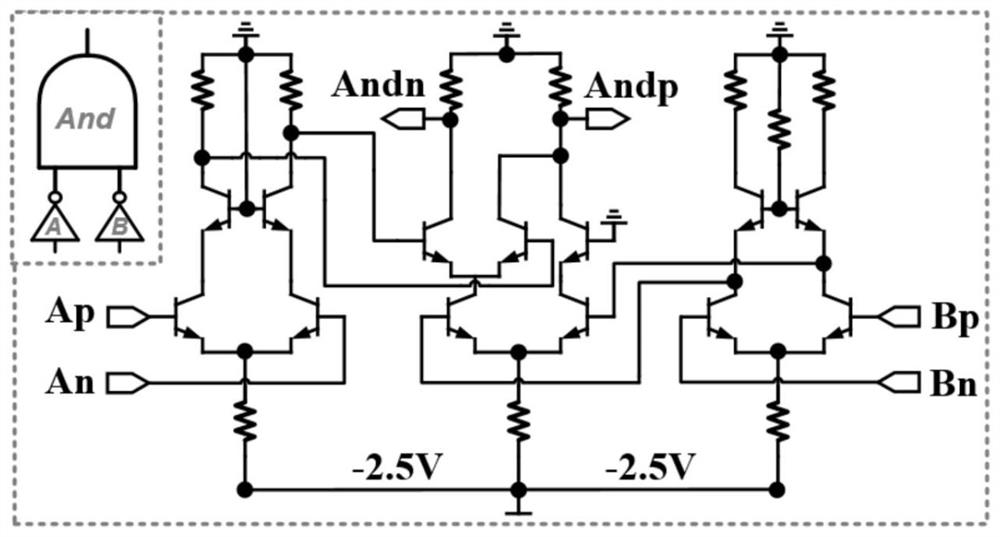

[0049] The embodiment of the present disclosure provides a multi-phase multi-duty cycle clock generation circuit, which will be combined with the following figure 1 - attached Image 6 , a multi-phase multi-duty cycle clock generation circuit provided in the embodiment of the present application is introduced in detail.

[0050] figure 1 It is a structural schematic diagram of a multi-phase multi-duty cycle clock generation circuit shown according to an exemplary embodiment. like figure 1 As shown, a multi-phase multi-duty cycle clock generation circuit, including:

[0051] Input buffer module, its input terminal receives the input signal, and the output terminal is connected to the input terminal of the frequency divider; in some exemplary scenarios, input a clock signal with a duty ratio of 50%, after being buffered and amplified by the input buffer module, the above signal is sent to the input of the divider.

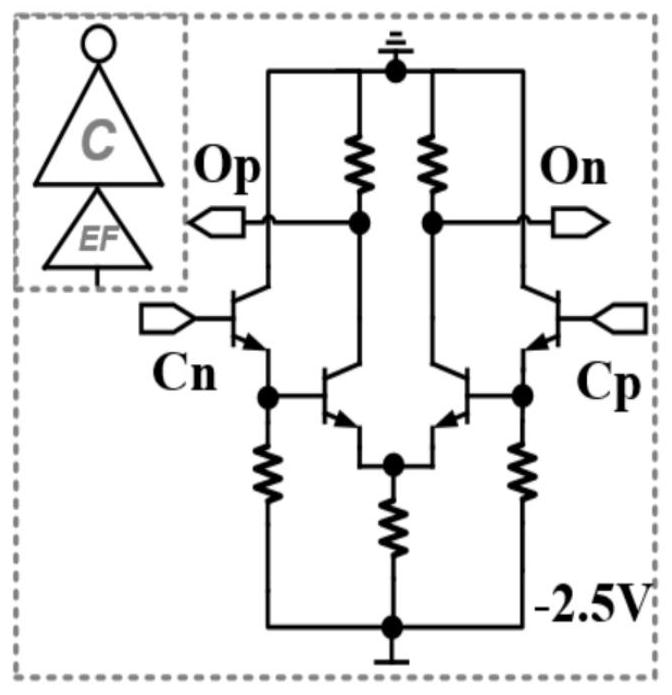

[0052] Specifically, the input buffer module is composed o...

Embodiment 2

[0073] The embodiment of the present disclosure provides a simulation example of a multi-phase multi-duty cycle clock generation circuit.

[0074] Figure 7 It is a schematic diagram of simulation results of a multi-phase multi-duty cycle clock generation circuit shown according to an exemplary embodiment.

[0075] In a possible implementation manner, a 0.8 μm InP DHBT device process library is used to simulate the characteristics of the multi-phase clock generation circuit of the embodiment of the present disclosure in ADS software.

[0076] Specifically, the circuit characteristics include the frequency range of the clock applied at the input, including the highest frequency and the lowest frequency, and the highest output spectrum of clocks with different duty ratios. The output waveforms corresponding to the frequencies respectively.

[0077] Figure 7 (a) is the multi-phase clock generation circuit of the embodiment of the present disclosure input 93GHz, output 46.5GHz...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More