IO expansion chip

An expansion chip and chip technology, applied in the field of IO expansion chips, can solve the problems of increasing system hardware circuit complexity, hardware circuit complexity, unfavorable pin utilization, etc., to achieve reliable and more accurate collection, precise protection logic control function, The effect of simple wiring

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment 1

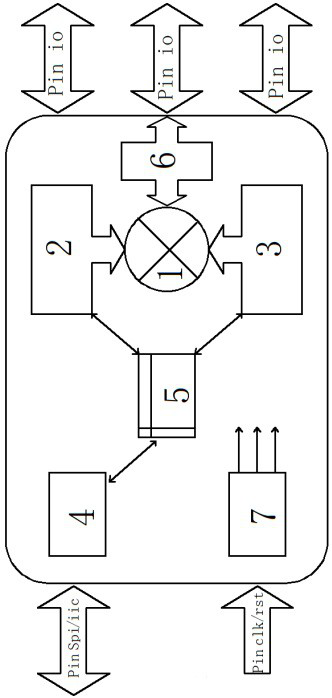

[0033] like figure 1 As shown, the IO configuration module 1 is used to select and control the connection of the IO input acquisition filter module 2, the IO output control module 3 and the specific pins outside the chip; the configuration data is transmitted from the external MCU through the MCU communication interface module 4 and the internal bus control module 5 write;

[0034] IO input acquisition filter module 2, the configuration selection is connected to the external Pin pin of the chip, the high and low level status of the pin is collected, and then the high and low level counts are performed. When the high level count is greater than the value of N1, the signal "1" is recorded, and the low level counts When it is greater than the value of N2, the signal "0" is recorded, and the signal remains unchanged in other states; the values of N1 and N2 are written by the internal bus control module 5, and the signal results are read by the internal bus control module 5;

[...

specific Embodiment 2

[0041] like figure 1 As shown, the chip pin Pin Spi / iic, where Spi includes 4 signals of MISO, MOSI, clock CLK, and CS chip selection; iic includes SDA, CLK, and is multiplexed with the Spi signal. In actual application, choose one of the communication methods. When the power is turned on, it is detected that the CS chip selection is always valid, and the configuration is iic communication, otherwise it is Spi communication.

[0042] Set the clock and reset pins separately for the chip to provide clock and reset control; set multiple IO pins, generally set 8 to 64 channels, for example, select 8, 12, 16, 32, 48, 64, etc.

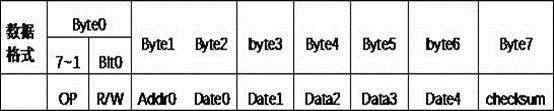

[0043] The MCU communication interface module 4 calls the common protocol stack to realize basic Spi / iic communication; in addition, the following data packet format is defined, and the total length of data includes but is not limited to 8 bytes. It defines the OP device address segment. When the chip address does not match it, it will stop exiting the comm...

specific Embodiment 3

[0054] The input port of the IO expansion chip of the present invention integrates a perfect digital filter function, which can be used for reliable sampling and acquisition of signals, and the filter constants of each channel can be independently programmed and configured; the output port integrates real-time protection logic for output control, and its Protection constants and control timing, each channel can be independently programmed and configured; each pin of the chip can be independently programmed and configured as input and output, and then respectively realize input or output filtering and related control functions;

[0055] The IO expansion chip of the present invention is based on the custom application protocol of Spi and iic, including communication formats and timing requirements such as device addresses and checksums, and can realize multi-chip cascading, and perform verification and detection of communication data packets to ensure communication reliability . ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com