Mask operation method of explicit independent mask register in GPU

A technology of a mask register and an operation method, applied in the field of image processing units, can solve the problems of frequent movement of data in implicit mask registers and general-purpose registers, increasing the power consumption of programmable processor cores, increasing the delay of program execution, and the like, Achieve the effect of avoiding invalid operand reading and performing pipeline operations, optimizing the instruction issue process, and reducing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

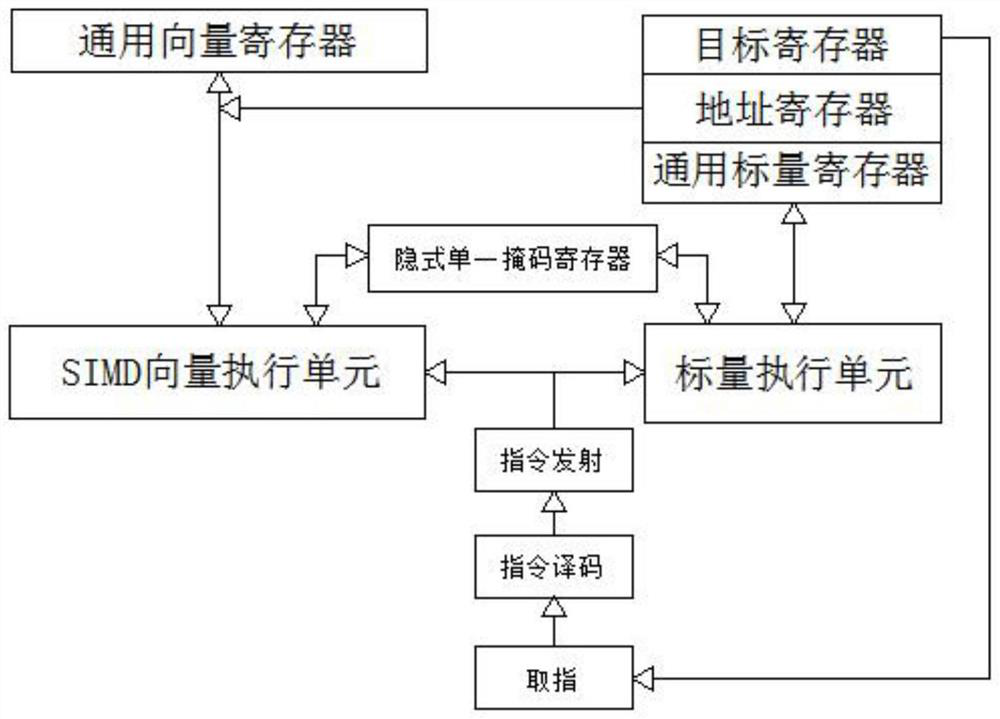

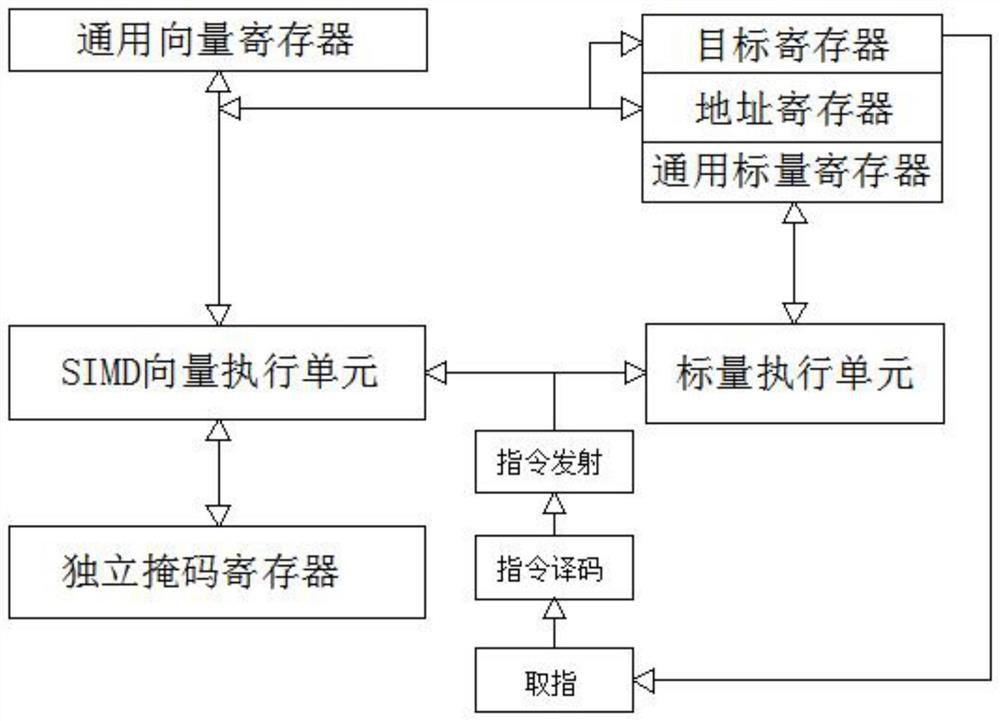

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

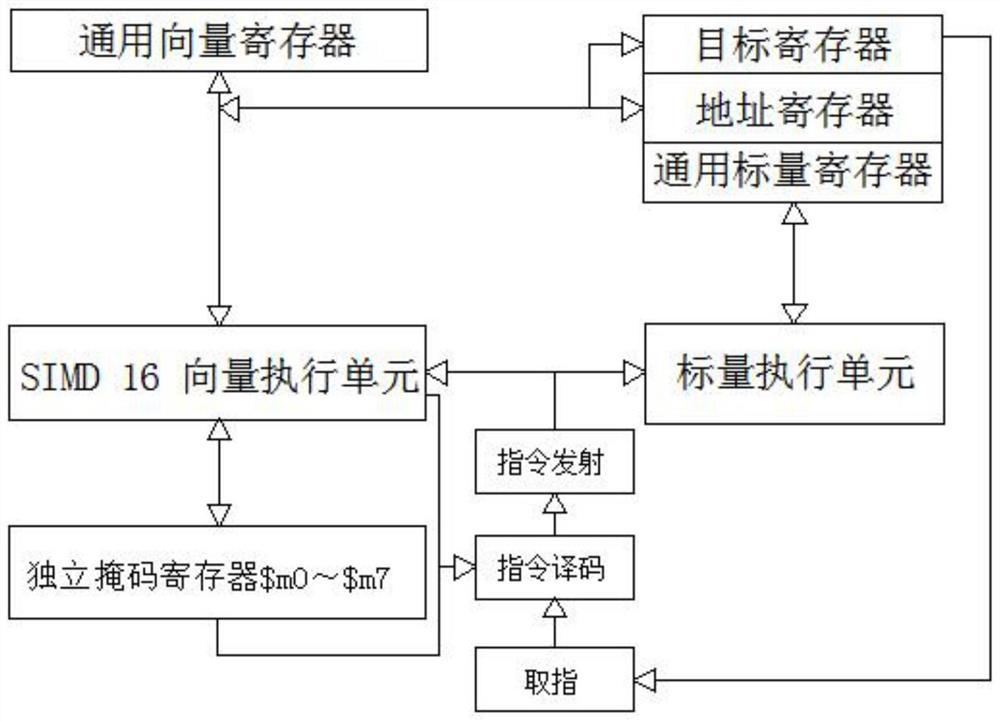

[0022] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

[0023] The present invention provides a technical solution: a mask operation method of an explicit independent mask register in a GPU, comprising the following steps:

[0024] A mask operation method for an explicit independent mask register in a GPU, comprising the following steps:

[0025] S1: Each GPU hardware thread can access its own 8 128-bit-wide independent mask registers, marked as $m0~$m7;

[0026] S2: The data in $m0 defaults to the execution mask ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More